相应的设计结构和设计内容也变得日益复杂

目前的应用开发速度已无法满足企业的需求

如何简化设计进程,提高应用开发效率

成为当下亟需解决的问题

赛灵思 Versal 自适应计算加速平台的设计方法论

是帮助精简 Versal 器件设计进程的一整套最佳实践

遵循这些步骤和最佳实践进行操作

将有助于以最快且最高效的方式实现期望的设计目标

多计算引擎支持不同系统设计类型

Versal ACAP 属于异构计算平台,具有多个计算引擎。在 Versal ACAP 上可映射各种应用,包括对无线系统、机器学习推断和视频处理算法进行信号处理。除了多个计算引擎外,Versal ACAP 还可使用高速串行 I/O、片上网络 (NoC)、 DDR4/LPDDR4 存储器控制器和多重速率以太网介质访问控制器 (MRMAC) 来提供超高系统带宽。Versal 器件分类为 Versal Prime 系列、Premium 系列和 AI Core 系列。

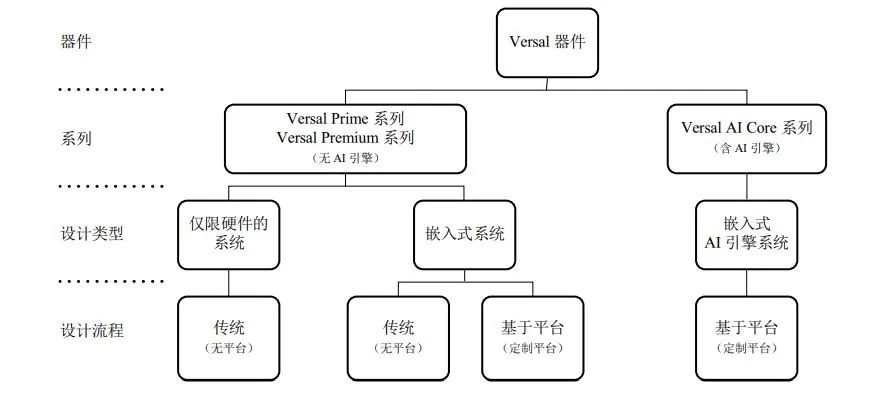

下图显示了每种 Versal 器件系列所支持的不同系统设计类型和设计流程。

图:系统设计类型

适用所有系统的设计流程

系统设计方法论要求基于目标应用明确所有系统要求。其中包括识别具有正确特性(例如,DDRMC IP 数量、AI 引擎 等)的相应 Versal 器件。您还必须考量功耗和发热要求。选择相应的器件后,下一步即可着手系统设计,包括在器件上进行目标应用的软硬件协同设计、系统验证以及初始化和调试。

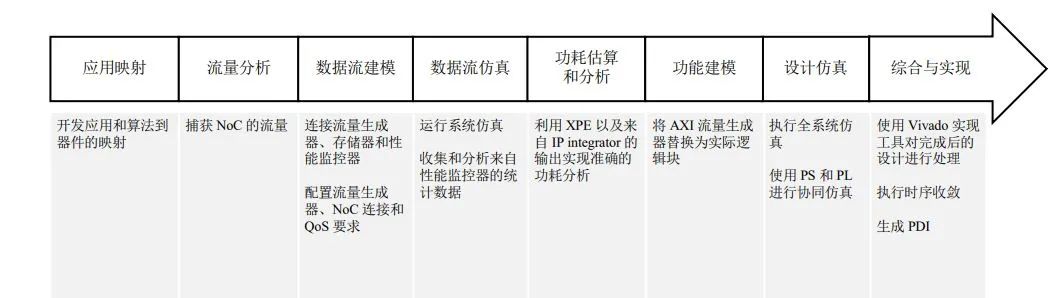

为确保充分利用 Versal ACAP 中可用的多种多样的计算元件,并使用最高效的实现流程,赛灵思建议采用下图所示的系统设计方法论流程,此流程适用于所有系统设计类型。

图:系统设计方法流程

系统设计时的考虑因素

合理可行的设计流程解决方案需要将各种关键变量考虑在内,在仅限硬件的系统设计中,关键注意事项之一设计中的数据流。通常这些设计都具有下列组件:

• 多个高速 I/O 接口

• 内部数据缓冲和存储,具有由片上 RAM 和外部 DDR 存储器组成的存储器层级

• 内部数据处理逻辑

对于能够处理外部和内部流量带宽和时延要求的设计,为其创建 DDRMC-NoC 配置至关重要。赛灵思建议先执行流量分析以评估并最终明确流量,然后再继续执行设计的整体集成和实现阶段。除此以外,报告中还涵盖了嵌入式系统设计值得考量的特殊注意事项,根据随附的是嵌入式系统还是服务器系统,每个步骤所面临的难题也不尽相同。

编辑:jq

-

存储器

+关注

关注

39文章

7756浏览量

172187 -

数据

+关注

关注

8文章

7348浏览量

95016 -

RAM

+关注

关注

8文章

1401浏览量

120998 -

DDR

+关注

关注

11文章

761浏览量

69551 -

AI

+关注

关注

91文章

41101浏览量

302579

原文标题:用户指南 | Versal ACAP:精简设计进程的最佳实践

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

手机主板散热导热胶薄层涂布最佳实践 |铬锐特实业

BMS设计中如何选择MOSFET——关键考虑因素与最佳实践

长电科技荣获2025年上市公司可持续发展最佳实践案例

立讯精密荣获2025年上市公司可持续发展最佳实践案例

思瑞浦获评“2025年上市公司董事会最佳实践案例”

爱芯元智荣获2025金辑奖最佳技术实践应用奖

安波福荣获2025年度最佳实践奖之产品领导力大奖

AMD Versal自适应SoC内置自校准的工作原理

达实智能荣获中国企业管理“十大最佳实践”奖

生产环境中Kubernetes容器安全的最佳实践

Linux网络管理的关键技术和最佳实践

AMD第二代Versal AI Edge和Versal Prime系列加速量产 为嵌入式系统实现单芯片智能

Versal 600G DCMAC Subsystem LogiCORE IP产品指南

天马荣获新财富杂志“2024 ESG最佳实践奖”

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

Versal ACAP:精简设计进程的最佳实践

Versal ACAP:精简设计进程的最佳实践

评论