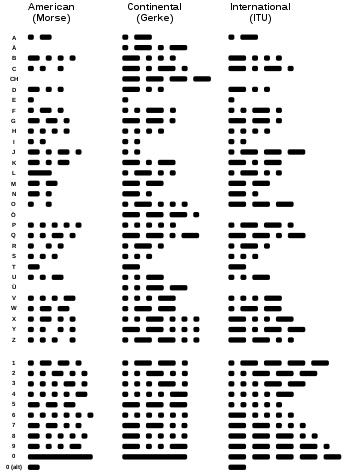

1 UART发展历史1.1 早期的串行通讯设备早期的电报机器使用长度可变的脉冲信号进行数据传输,比如摩斯电码;

摩斯电码

后来电传打印机(teleprinters )普遍使用5、6、7或8个数据位来表示各种字符编码,最终成为计算机外围设备。电传打字机( teletypewriter 简称 tty)成为小型计算机十分出色的通用I/O设备。

Teletypewritter

由于历史的发展原因,早期在Unix终端是一个名字为ASR33的电传打字机,而电传打字机的英文单词为Teletype(或Teletypewritter),缩写为tty。因此,终端设备也被称为tty设备。这就是TTY这个名称的来源。

1.2 早期的芯片级UARTDEC(Digital Equipment Corporation)公司的Gordon Bell 为该公司的PDP系列计算机设计了第一个UART,不过体积庞大,UART的线路占据了整个电路板;

后来DEC将串行线路单元的设计浓缩为早期的UART单芯片,以方便自己使用。

DEC是美国一家计算机公司;

西部数据(Western Digital)公司在1971年左右将其开发为第一个广泛可用的UART单芯片 WD1402A。这是中型集成电路的早期产品。

Western Digital是美国计算机硬盘驱动器制造商和数据存储公司。

1.3 现代UART的发展2000年代开始,大多数IBM或者相关的计算机都删除了其外部RS232的COM端口,将其替换为带宽性能更加出色的USB端口;

对于仍然需要RS-232串行COM端口的用户,现在通常使用外部USB转UART转换器,常见的有CH340,Silicon Labs 210x的驱动程序,现在很多处理器和芯片都内置了UART。

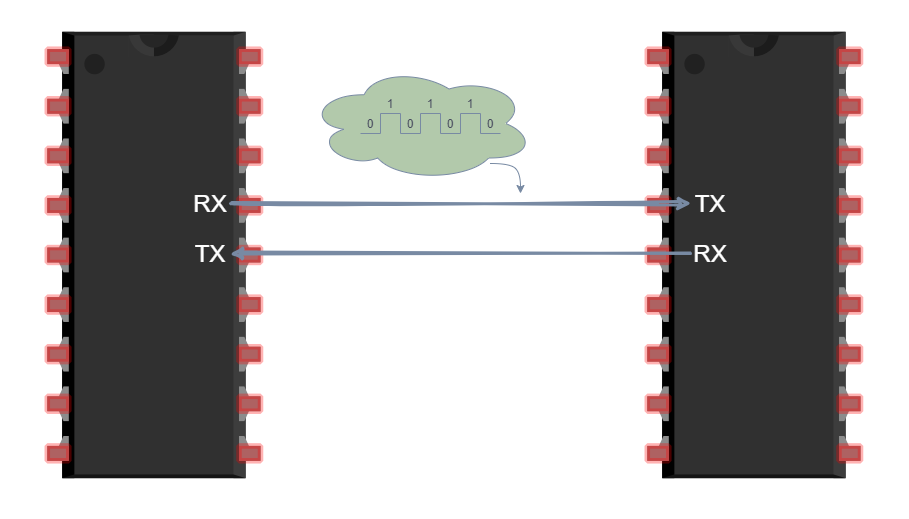

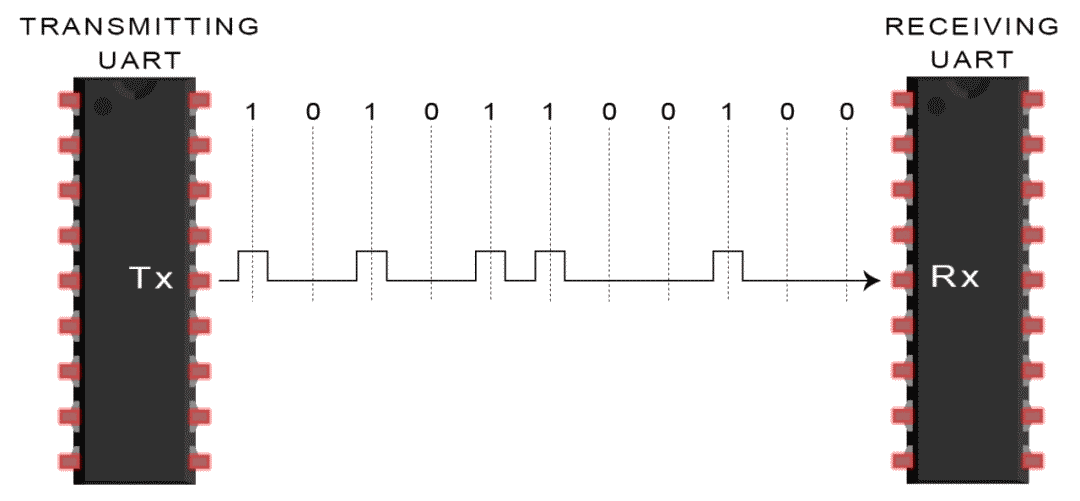

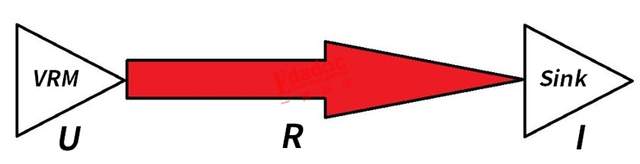

2 预备知识通用异步收发传输器(Universal Asynchronous Receiver/Transmitter,通常称为UART),在UART通信中,两个UART直接通信。

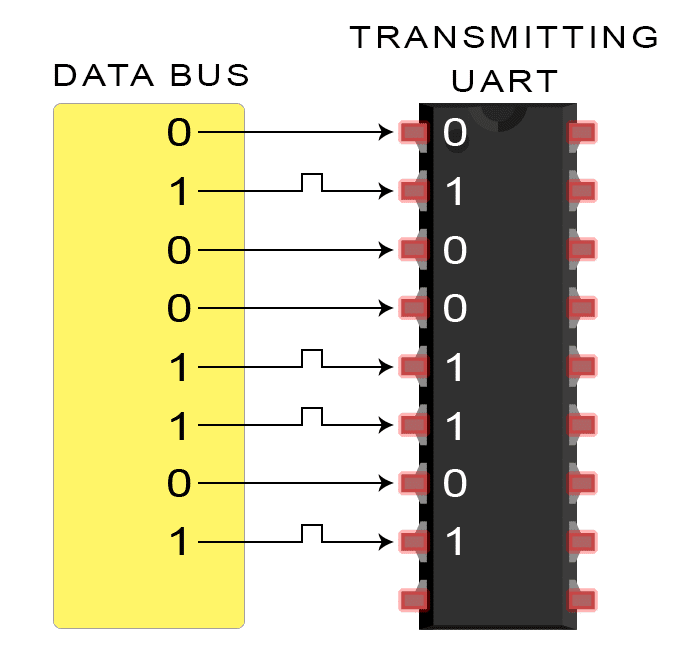

发送端的UART将来自控制设备(如CPU)的并行数据转换为串行数据,以串行方式将其发送到接收端的UART,然后由接收端的UART将串行数据转换为并行数据以用于接收设备的正常处理。

这里只需要两条线RX/TX即可在两个UART之间传输数据。具体如下图所示;

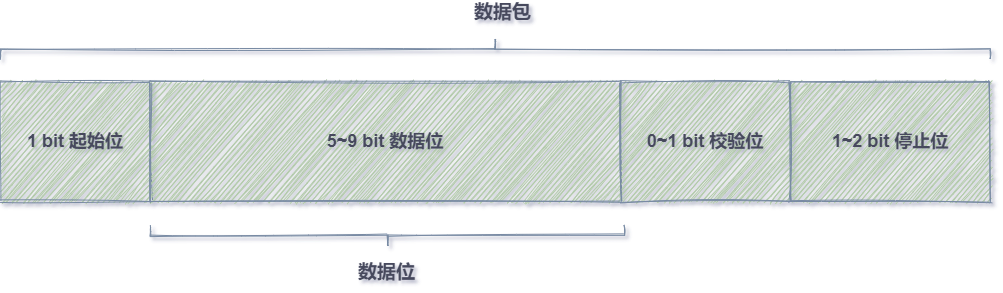

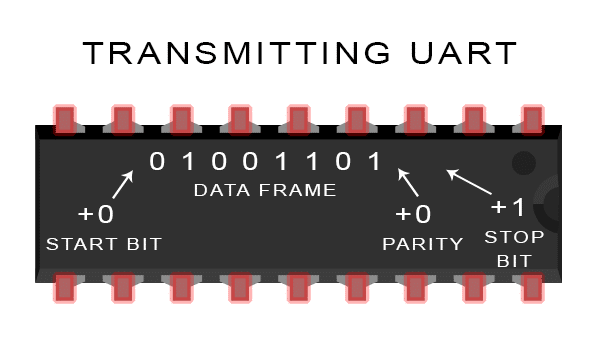

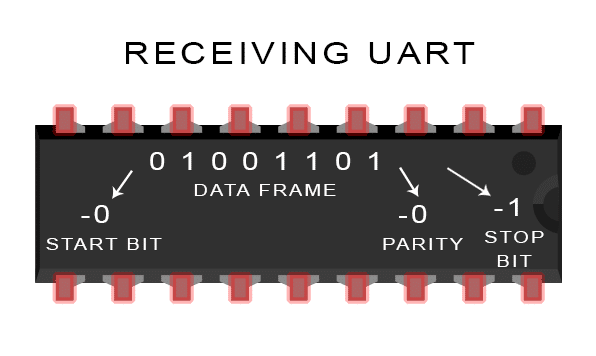

3 协议层UART传输的数据被封装成数据包。每个数据包包含1个起始位,5~9个数据位(取决于UART的具体设置),一个可选的奇偶校验位以及1个或2个停止位,具体如下图所示;

协议格式

起始位UART数据传输线通常在不传输数据时保持在高电平。

为了开始数据传输,发送端UART在一个时钟周期内将传输线从高电平拉低到低电平。

当接收端UART检测到高电压到低电压转换时,它开始以波特率的频率读取数据位中的每一位数据。

数据数据位包含正在传输的实际数据。如果使用奇偶校验位,则可以是5位,最多8位。如果不使用奇偶校验位,则数据帧的长度可以为9位。

在大多数情况下,数据首先以低有效位发送。

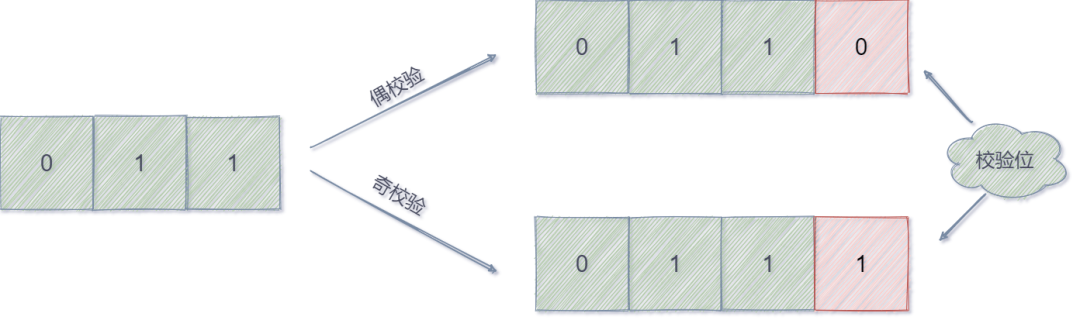

校验位在串口通信中一种简单的检错方式。

有四种检错方式:偶校验、奇校验、高校验和低校验。当然没有校验位也是可以的。

对于偶和奇校验的情况,串口会设置校验位(数据位后面的一位),用一个值确保传输的数据有偶个或者奇个逻辑高位。

举个例子,如果数据是011,则满足;

偶校验,校验位为0,保证逻辑高的位数是偶数个。

奇校验,校验位为1,这样就有3个逻辑高位。

具体如下图所示;

奇校验和偶校验

高位和低位不是真正的检查数据,而是强行将校验位设置为逻辑高或者逻辑低。这样使得接收设备能够知道一个位的状态,有机会判断是否有噪声干扰了通信或者是否传输和接收数据是否不同步。

停止位发送端UART将数据传输线从低电压驱动到高电压至少持续两位数据的时间宽度来表示整个数据包的传输已经结束。

由于数据是在传输线上定时的,并且每一个设备有其自己的时钟,很可能在通信中两台设备间出现了小小的不同步。因此停止位不仅仅是表示传输的结束,并且提供计算机校正时钟同步的机会。适用于停止位的位数越多,不同时钟同步的容错性越好,但是数据传输率同时也越慢。

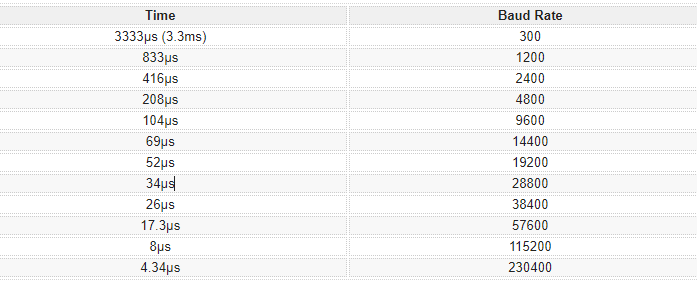

波特率波特率是串口数据的传输速度,即Bit/s,常见的波特率有:9600,19200,38400,57600,115200,当然还有很多波特率,不再一一给出;

假设目前UART的配置为,1个起始位,8个数据位,0个校验位,1个停止位,那么9600的波特率,可以计算出每一位数据的时间宽度为:

那么传输一个字节(也就是10 bit 数据)需要的时间为 1.04 毫秒。

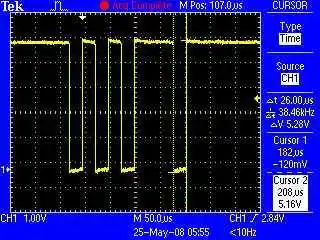

下面用串口抓取了UART的TX上的信号,其中一位数据的时间宽度为26微秒,具体如下图所示;

则可以简单计算得到;

因此波特率大概为 38400;

下表是各个波特率下数据位时间宽度;

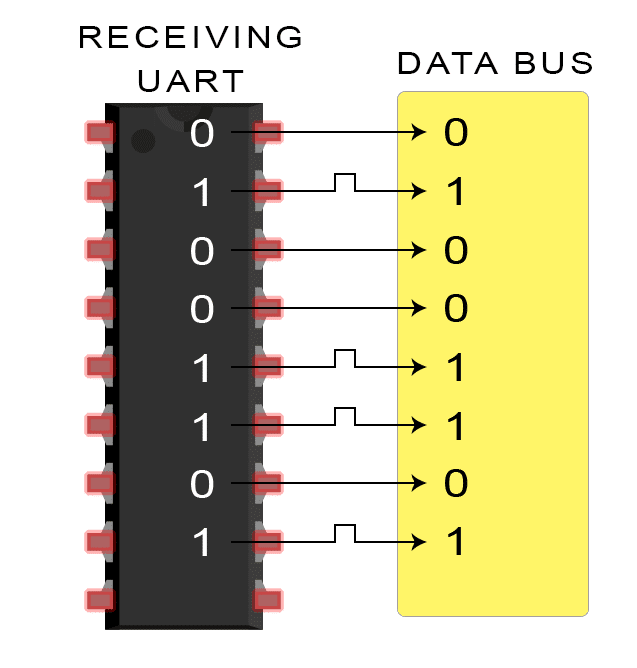

4 传输过程发送端UART从数据总线转换并行数据:

发送端UART将起始位,奇偶校验位和停止位添加到数据包中:

整个数据包从发送端UART串行发送到接收端UART;接收端UART按照预先配置好的波特率对数据线进行采样:

接收端UART解析接收的数据,丢弃数据包中的起始位,奇偶校验位和停止位:

接收UART将串行数据转换回并行数据,并将其传输到接收端的数据总线:

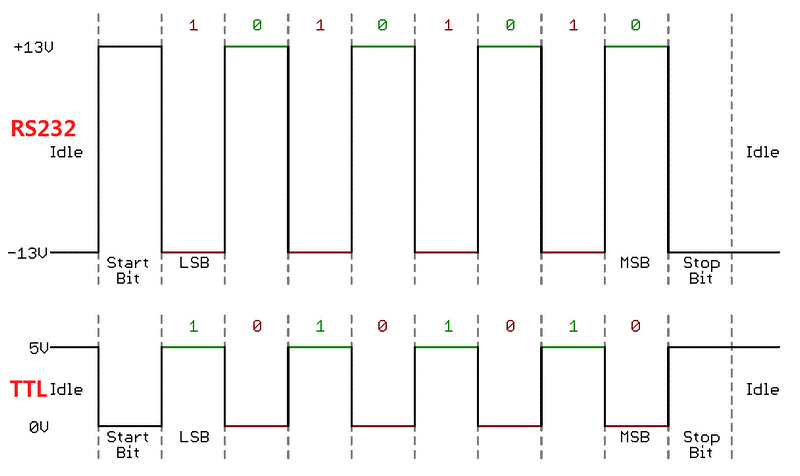

5 物理层UART、RS232、RS485在串口通信中,主要区别是电平的不同,其中UART通常使用TTL电平,下面介绍这几个存在的差异;

TTL

TTL全名是晶体管-晶体管逻辑集成电路(Transistor-Transistor Logic)

输入高电平最小2V,输出高电平最小2.4V,典型值3.4V;

输入低电平最大0.8V,输出低电平最大0.4V,典型值0.2V。

RS232

RS232 逻辑1电平(MARK)=-3V~-15V,逻辑0电平(SPACE)=+3~+15V;

同样的,对于传输数据0x55,即二进制的01010101,RS232和TTL的区别如下;

RS485

RS485是差分信号进行串行传输;

逻辑1以两线间的电压差为+(2~6)V表示;

逻辑“0”以两线间的电压差为-(2~6)V表示;

在工业通信中,使用RS485比较多,因为RS485是差分信号,可以抑制共模干扰,因此在恶劣的环境中拥有很好的抗干扰性,比较稳定;

6 优缺点没有任何通信协议是完美的,以下是UART的一些利弊,可帮助您确定它们是否适合您的项目需求:

优点

通信只需要两条数据线;

无需时钟信号;

有奇偶校验位,方便通信的差错检查;

只需要接收端和发送端设置好数据包结构,即可稳定通信;

缺点

数据帧最大支持9位数据;

不支持多主机或多从机的主从系统;

编辑:jq

-

集成电路

+关注

关注

5388文章

11544浏览量

361783 -

电平

+关注

关注

5文章

360浏览量

39895 -

晶体管

+关注

关注

77文章

9688浏览量

138159 -

uart

+关注

关注

22文章

1235浏览量

101383 -

数据包

+关注

关注

0文章

261浏览量

24390

原文标题:我打赌!你还不会UART!不信,你看看~

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

你知道LED全息隐形屏是什么吗?

明明我说的是25G信号,你却让我看12.5G的损耗?

明明我说的是25G信号,你却让我看12.5G的损耗?

关于陶瓷电路板你不知道的事

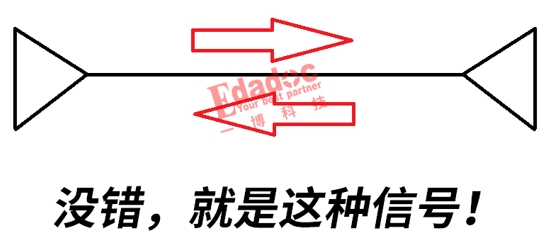

双向收发的信号应该在哪进行串联端接?分享几个实用设计方法!

FHT4644国产替代必然性崛起你还不来了解一下芯片这些事吗

为什么串阻阻值通常是22到33欧姆,看完后不信你不懂!

STM32F103RCT6 uart1中断方式接收后不返回主程序了,但新的中断还能进来是怎么回事?

还不会代码托管吗?一文教会你使用Gitee~

我猜你还不会UART!不信你点进来看看

我猜你还不会UART!不信你点进来看看

评论