一、介绍

在同步系统中,数据始终相对于时钟具有固定的关系 当该关系满足设备的建立和保持要求时,输出将在其指定的传播延迟时间内进入有效状态。在同步系统中,输入信号始终满足触发器的时序要求。因此,不会发生亚稳性。但是,在异步系统中,数据和时钟之间的关系不是固定的。因此,会偶尔发生违反建立时间和保持时序的情况。发生这种建立和保持时序的情况时,输出可能会到达其两个有效状态(0和1)之间的中间水平,不稳定的状态(0和1之外的状态即亚稳态)保持的时间也是不确定的,直到自己进入稳态。

二、亚稳态理论

由于违反了触发器的建立和保持时间,因此会产生亚稳定性。在任何设计中使用的每个触发器都有指定的建立和保持时间,或者说是在时钟上升沿之前和之后不允许输入数据变化的时间。如果信号在此时间窗口内确实发生变化,则输出将是未知的或“亚稳的”。这种有害状态的传播称为亚稳态。结果,触发器的输出会产生毛刺或暂时保持在亚稳状态,因此需要更长的时间才能返回到稳定状态。

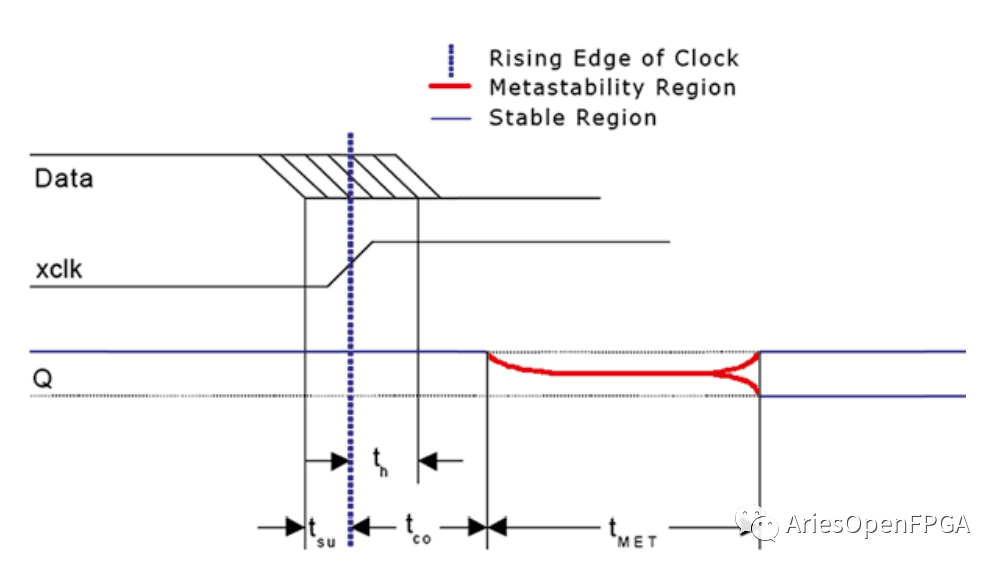

当触发器处于亚稳态时,输出会在高电平和低电平之间徘徊,导致输出转换被延迟,并超过指定的时钟到输出延迟(tco)。亚稳态输出需要花费超过tco的额外时间才能解析为稳定状态,该时间称为稳定时间(tMET)。

图1.1亚稳时序参数

这已在图1.1中显示,但并非每个违反建立或保持时间的转换(数据转换)都会导致亚稳态输出。触发器进入亚稳态的可能性和返回稳定状态所需的时间取决于用于制造器件的工艺技术以及环境条件。通常,触发器将在一两个时钟周期内返回稳定状态。

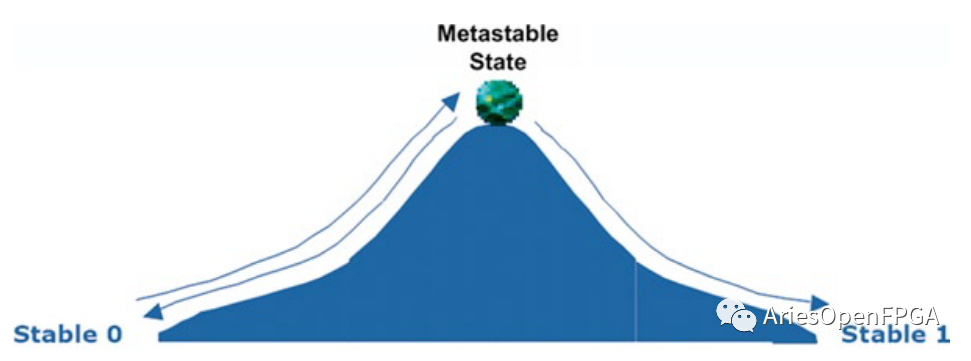

触发器的操作类似于在无摩擦的山坡上滚动的球,如图1.2所示。小山的每一侧代表稳定状态(即高或低),顶部代表亚稳态。假设球处于稳定状态(即1或0),并且对球进行了足够的推动(状态转换)(没有违反建立时间或保持时间),足以使球越过另一个稳定状态,则球在指定时间内越过另一个稳定状态。

但是,如果推力较小(即违反建立和保持时间),则球应移动到山顶(即输出亚稳态),停留在那里一段时间,然后返回任一稳定状态(即输出最终变得稳定)。球也可能会部分升起然后回来(即输出可能会产生一些毛刺)。任何一种情况都会增加从时钟转换到稳定输出的延迟。

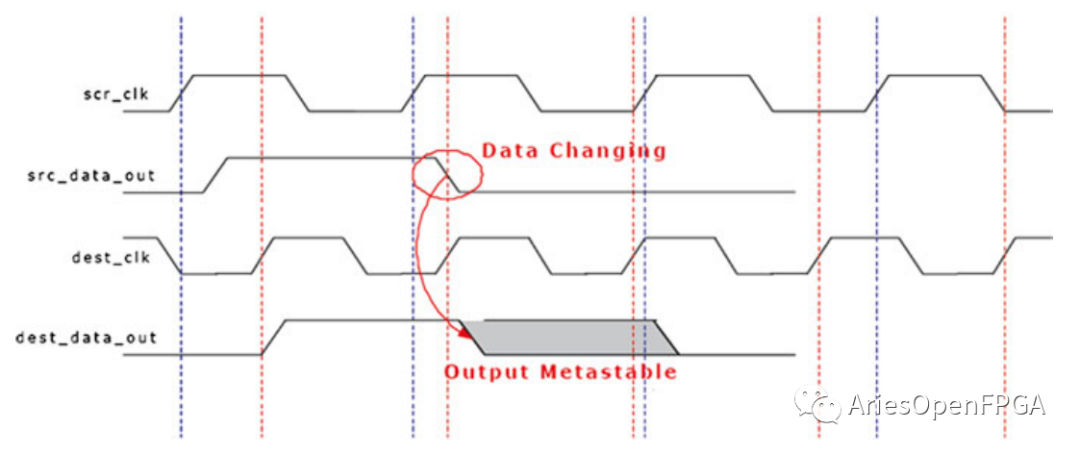

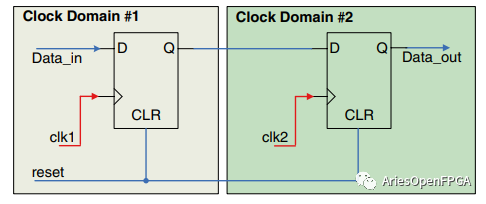

因此,简单来说,当信号在一个时钟域(src_data_out)中发生变化并在另一个时钟域(dest_data_in)中被采样时,这将导致输出变得亚稳。这被称为同步失败(如图1.3所示)。

图1.2触发器的亚稳态行为

图1.3触发器中的亚稳态

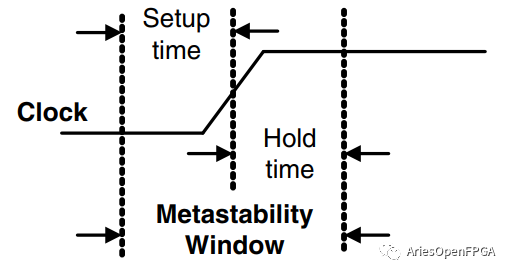

三、亚稳态窗口

亚稳态窗口被定义为特定的时间长度,在此期间数据和时钟均不应更改。如果两个信号有发生改变,则输出可能变为亚稳态。如图1.4所示,建立时间和保持时间的组合决定了亚稳窗口的宽度。窗口越大,设备进入亚稳态的机会就越大。在大多数情况下,较新的逻辑系列具有较小的亚稳态窗口,从而减少了设备变为亚稳的机会。

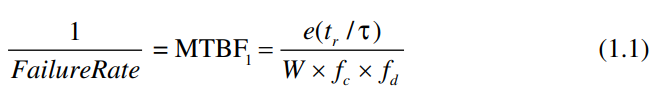

四、计算MTBF

系统之间的平均故障间隔时间(MTBF)是在故障率恒定的特殊情况下故障率的倒数。这提供了有关特定触发器失败频率的信息。对于具有给定时钟频率和异步数据边沿的单级同步器,该边沿在时钟周期内具有均匀的概率密度,通过建立和保持时间窗口与时钟边沿之间的时间之比,再乘以数据边沿频率,可以计算出亚稳态事件的发生率。

图1.4亚稳窗口

其中

tr =允许的解决时间超过器件的正常传播延迟时间

π =触发器的亚稳态(解析)时间常数

W =亚稳态窗口

fc =时钟频率

fd =异步数据边沿频率

常数W和τ与设备的电气特性有关,并且会根据工艺技术节点而变化。因此,使用相同工艺制造的不同设备的W和τ值相似。

如果在不同的分辨时间下测量设备的故障率并绘制图表,则结果将呈指数衰减曲线。如图1.5所示,当以半对数标度绘制时,它成为一条斜率等于τ的直线;因此,线上的两个数据点足以使用等式1.2计算τ的值。

其中:

tr1 = 解析时间1

tr2 = 解析时间2

N1 = tr1处的故障数

N2 = tr2处的故障数

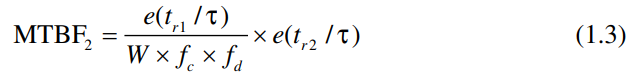

根据公式1.1和1.2,可以通过下面的公式1.3计算两级同步器的MTBF

其中:

tr1=同步器第一级所允许的解析时间

tr2 =接入正常传播延迟时的解析时间

公式1.3中的第一项计算了同步器第一阶段的MTBF,这实际上成为了下一阶段亚稳态事件的发生率。然后,第二项根据tr2的值(同步器外部允许的解决时间)计算亚稳态事件将被解决的概率。这两个项的乘积给出了两级同步器的总体MTBF。以定量的方式,使用上面的公式1.3,如果特定触发器在给定时钟速率和输入转换速率的范围内的平均故障间隔时间(MTBF)为40 s,则使用两个这样的触发器的MTBF 同步输入将是40×40 = 26.6分钟。

五、避免亚稳态

如第二节所示,只要违反建立或保持时间,就会发生亚稳。因此,在以下情况下,信号可能会违反时序要求:

1、当输入信号是异步信号时。

2、当时钟偏斜/偏摆(上升/下降时间)高于容许极限时。

3、当信号越过工作在两个不同频率或频率相同但相位和偏斜不同的域时。

4、当组合延迟使得触发器数据输入在亚稳态窗口中发生变化时

亚稳定性可能会导致过度的传播延迟和后续的系统故障。所有触发器和锁存器均具有亚稳性。这个问题无法消除。但是有可能降低亚稳态的发生率

图1.6 N级同步器

图1.7具有时钟提升电路的多级同步器

Multi-stage synchronizer with clock boost circuitry

在最简单的情况下,设计人员可以通过让时钟周期足够长以解决准稳态以及减少路径中可能传播到下一个触发器中的任何延迟逻辑来避免亚稳态。考虑到大多数现代设计的性能要求,这种方法虽然简单,却并不实用。另一种方法是使用同步器。

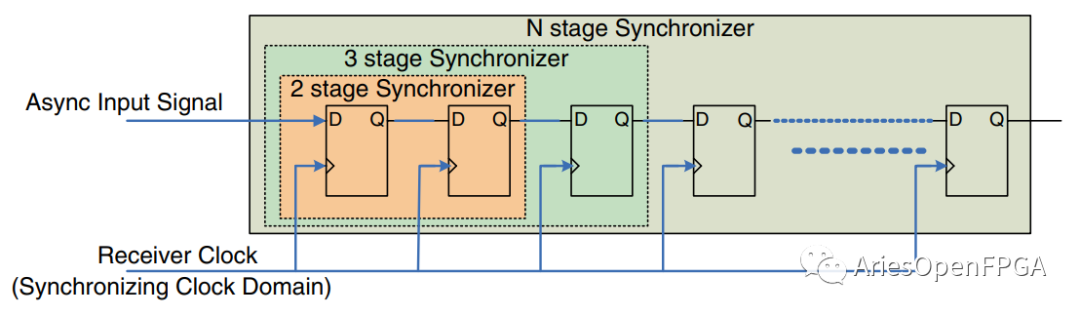

5.1使用多级同步器

避免亚稳态的最常见方法是在一个时钟域到另一个时钟域的信号上添加一个或多个同步触发器。如图1.6所示,这种方法为第一个同步触发器中的亚稳态事件提供了一个完整的时钟周期(第二个触发器的建立时间除外)以解决自身问题。但是,这确实增加了同步逻辑观察输入的等待时间。

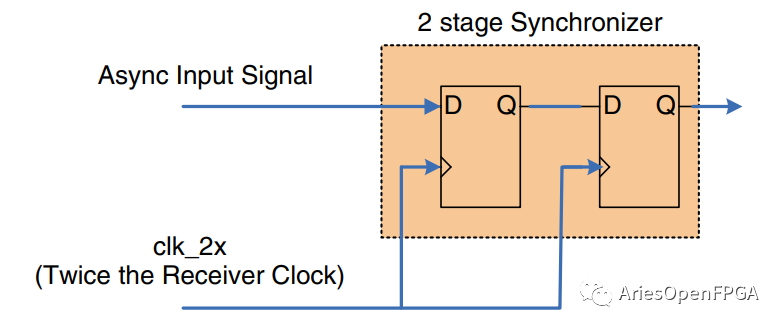

5.2使用时钟升压电路的多级同步器

多级同步器的一个限制是系统响应异步输入所花费的时间更长。解决此问题的方法是使用时钟倍频器的输出为两个同步触发器提供时钟。Altera的FPGA将这种技术称为Clock Boost或Clock Doubler(图1.7)。

这种方法允许系统在一个系统时钟周期内响应异步输入,同时仍能改善MTBF。尽管Clock Boost时钟可能会降低MTBF,但这种影响远不止于两个同步触发器的抵消。这两种方法都不能保证亚稳性不能通过同步器。它们只是降低了亚稳发生的可能性。

六、亚稳测试电路

每当触发器对异步输入进行采样时,小概率的不可预测延迟总会在触发器输出端呈现出来。这不仅发生在输入转换违反建立和保持时间规范时,而且还发生在触发器接收新数据时的小的时序窗口,在这些情况下,触发器会进入亚稳态。

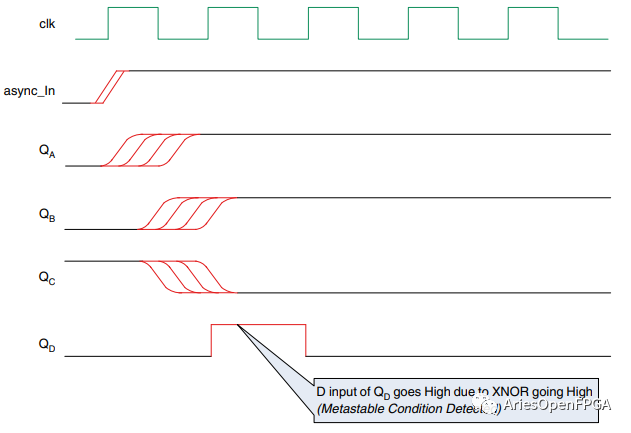

图1.8中描述的测试电路用于确定触发器的亚稳特性。图1.8显示了在时钟“ clk”的上升沿触发的触发器“ FFA”的异步输入“ async_In”。如图所示,触发器“ FFB”和“ FFC”均在时钟的下降沿触发,以便捕获“ FFA”上的亚稳事件。

当互补信号在触发器“ FFB”和“ FFC”的输入上传递时,无论何时“ FFA”上发生亚稳态事件,XNOR门的输出都将变为高电平。此条件在触发器“ FFD”的输出上捕获,指示已检测到亚稳态事件。

该测试电路中所有节点的时序如图1.9所示。由于解析触发器(“ FFB”和“ FFC”)由时钟下降沿提供时钟,因此可以通过更改时钟高电平时间(△t)来控制所需的建立时间。稳定时间tMET可通过以下公式确定

其中tACN是最小时钟周期,它等于解析触发器(FFB或FFC)的tCQ(FFA的时钟到输出延迟)的建立时间tsu。

图1.9亚稳测试电路的时序

减少解析时间或建立时间的方法之一是在建立/保持期间以数据为中心增加抖动。

七、同步器类型

根据等式 1.1,具有异步输入的电路的平均故障间隔时间(MTBF)与可从亚稳态条件恢复的时间呈指数关系。使用同步器创建时间缓冲区,以从亚稳态事件中恢复。

请注意,异步信号绝不能由多个同步器同步。(这样做会冒着使多个同步器的输出产生不同信号的风险)。本节显示了两个同步器方案A和B。

方案A是常规方案,当异步输入信号的宽度大于时钟周期时,其工作效果最佳(图1.10)。

请注意,即使异步输入在设置间隔之外达到稳定条件,它仍将以两个时钟周期的延迟进行计时,否则FF1可能会进入亚稳态。

如果亚稳在少于一个时钟周期内得到解决,则FF2将具有稳定的输入,否则需要更深的级联,如图1.6所示。

图1.10两级同步器的同步器方案A

图1.11两级同步器的同步器方案B

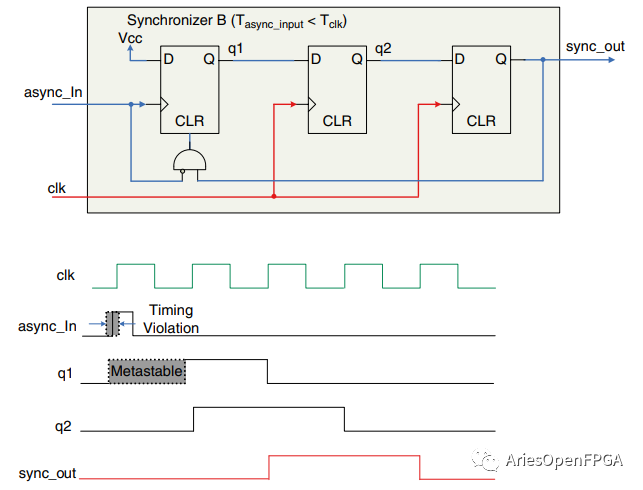

但是,在异步输入的宽度小于时钟周期的情况下,方案A不起作用。在这种情况下,方案B的工作效果最佳,如图1.11所示。

请注意,在同步器方案B的情况下,第一个FF(触发器)的D输入连接到VCC,而异步输入为FF提供时钟。该阶段中的其他两个FF由系统时钟或clk直接提供时钟。短脉冲将驱动q1高电平,该信号将在两个“clk”边沿之后传播到sync_out。因此,这定义了我们的经验法则,总结如下:

当信号必须跨越时钟域之间的边界时,请使用同步器。

如果Clk1《Clk2在时钟域2的输入处使用同步器方案A(如图1.11所示),否则使用同步器方案B。

八、处理亚稳态的建议

(a)使用同步器。

(b)使用更快的触发器(更窄的亚稳态窗口TW)。

(c)使用亚稳态硬化触发器(专为非常高的带宽和减少的采样时间而设计,并针对时钟域输入电路进行了优化)。

(d)级联触发器作为同步器(两个或更多),如图1.6所示。一串N个触发器的概率为PN(P的N次方),其中P是一个触发器发生亚稳态故障的机会。

(e)降低采样率。

(f)避免输入dV/dt低的信号

编辑:jq

-

MTBF

+关注

关注

1文章

30浏览量

13575 -

触发器

+关注

关注

14文章

2000浏览量

61127 -

亚稳态

+关注

关注

0文章

46浏览量

13267 -

同步器

+关注

关注

1文章

98浏览量

14629

原文标题:亚稳态详解

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

双稳态电路的特点和应用

单稳态触发器稳态是什么状态的

单稳态触发器暂稳态由什么来维持

单稳态触发器有几个稳态几个暂稳态

稳态噪声和非稳态噪声的定义 非稳态噪声包括哪些

数字电路中的亚稳态是什么

无稳态是什么意思?单稳态是什么意思?双稳态是什么意思?

什么是单稳态触发电路 单稳态触发电路有哪些特点?有哪些应用

单稳态电路和双稳态电路的区别 单稳态电路的主要功能

单稳态触发器的暂稳态时间与什么有关

两级触发器同步,就能消除亚稳态吗?

复位信号存在亚稳态,有危险吗?

机器人与视觉标定理论详解

详解亚稳态的理论以及使用建议

详解亚稳态的理论以及使用建议

评论