一、操作

1.1、系统的概述

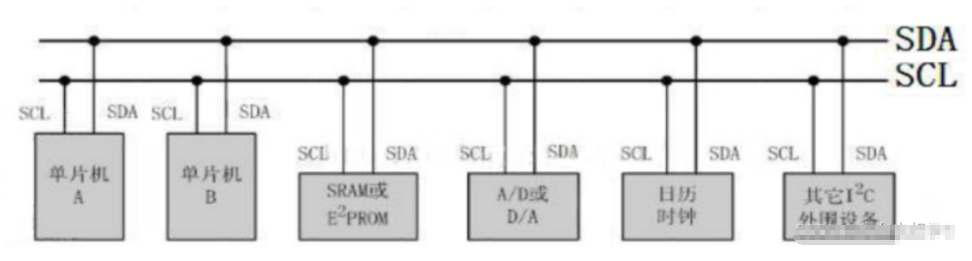

I2C系统使用串行数据线(SDA)和串行时钟线(SCL)进行数据传输。连接到这两个信号的所有设备必须具有漏极开路或集电极开路输出。这两条线上的逻辑“与”功能都通过外部上拉电阻器来实现。

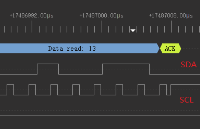

数据在主机和从机之间以字节为单位同步传输到SDA线上。每个数据字节为8位长。每个数据位都有一个SCL时钟脉冲,并且首先发送MSB。每个传送的字节后都有一个应答位。在SCL的高电平期间对每个位进行采样;因此,只能在SCL的低电平期间更改SDA线路电平,并且必须在SCL的高电平期间保持稳定。若SCL为高电平时,SDA线上存在跳变则被解释为命令(请参见START和STOP信号)。

1.2、IIC协议

从宏观的角度讲,IIC协议可以包含以下四个部分:

1、开始信号的产生(START)

2、从机地址传输

3、数据传输

4、停止信号产生(STOP)

1.2.1 开始信号(START)

当总线空闲/就绪时,这意味着没有主机设备正在使用总线(SCL和SDA线均为高电平),主机可以通过发送START信号来启动传输。START信号(通常称为STA-bit)定义为:SCL为高电平时,SDA从高到低的跳变。START信号表示新数据传输的开始。Repeated START是一种启动信号,但没有先产生一个停止信号。主机使用这种方法在不释放总线的情况下,以不同的传输方式(例如,从写入设备到从设备读取)与另一个从机或同一从机通信。

当命令寄存器中的STA-bit置1且RD或WR位置1时,内核产生一个START信号。根据SCL线的当前状态,将生成START或Repeated START。

1.2.2 地址线传输

在START信号之后,主机立即传送的数据的第一个字节是从机地址。这是一个7位的调用地址,后跟RW位(7address+1RW)。RW位向从机发送数据传输方向信号。一个系统中的两个从机不能具有相同的地址。只有地址与主机发送的地址匹配的从机会通过在第9个SCL时钟周期将SDA拉为低电平来返回一个应答位来做出响应。(从机拉低SDA作为ACK)

内核将从地址传输视为写操作。将从设备的地址存储在发送寄存器中,并将WR位置1。然后,内核将在总线上传输从机地址。

1.2.3 数据传输

一旦成功完成从机寻址,就可以按照主机发送的RW位指定的方向逐字节进行数据传输。在第9个SCL时钟周期中,每个传输的字节后都有一个应答位。如果从机发出“无应答”信号,则主机可以产生一个STOP信号来中止数据传输,或者产生一个Repeated START信号并开始一个新的传输周期。

如果作为接收设备的主机未应答从机,则从机释放SDA线供主机产生STOP或Repeated START信号。

要将数据写入从机,将要发送的数据存储在发送寄存器中,并将WR位置1。要从从机读取数据,请将RD位置1。在传输过程中,核心设置了TIP标志(Transfer in progress),指示正在进行传输。传输完成后,将重置TIP标志,设置IF标志(Interrupt Flag),并在使能时产生中断。设置IF标志后,接收寄存器包含有效数据。当TIP标志复位时,用户可以发出新的写或读命令。

1.2.4 停止信号

主机可以通过产生一个STOP信号来终止通信。STOP信号(通常称为P位)定义为SCL为逻辑1时SDA从低到高的跳变。

1.3、仲裁过程

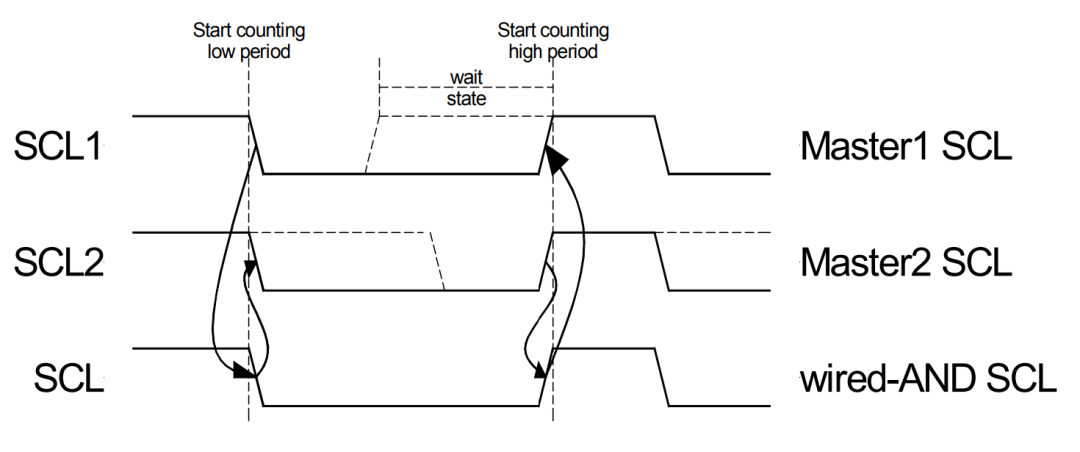

1.3.1 时钟同步化

I2C总线是真正的多主机总线,可以在其上连接多个主机。如果两个或多个主机同时尝试控制总线,则时钟同步过程将确定总线时钟。由于I2C信号采用“线与”连接,从高到低的跳变会影响连接到总线的所有设备。因此,SCL线上从高电平到低电平的转换会导致所有相关设备都将其低电平周期计算在内。一旦设备时钟变低,它将使SCL线保持在该状态,直到达到时钟高状态为止。由于采用“线与”连接,因此SCL线将由具有最短低电平周期的设备保持低电平,并由具有最短高电平周期的设备保持高电平。

1.3.2 时钟伸展

从设备可以使用时钟同步机制来降低传输比特率。主机将SCL拉低后,从机可以拉低SCL为所需的时间,然后释放它。如果从机的SCL低电平周期大于主机的SCL低电平周期,则将延长所得到的SCL总线信号低电平周期,从而插入等待状态。

编辑;jq

-

IIC

+关注

关注

11文章

300浏览量

38326 -

SDA

+关注

关注

0文章

124浏览量

28130 -

SCL

+关注

关注

1文章

239浏览量

17067 -

MSB

+关注

关注

0文章

13浏览量

8260

原文标题:IIC专题原理及应用篇(一)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MCU通过IIC口控制TLV320AIC3204,请问MCU的IIC接口和TLV320AIC3204的IIC接口对接时需要电平转换吗?

使用TAS5805M作为音频功放,但是初始化的IIC驱动一直不成功,求助一份IIC的底层驱动代码

IIC信号线需要增加上拉电阻,是因为IIC的IO是什么

IIC通讯协议解析

电压敏学术研讨委员会暨学习交流专题会议圆满召开

FPGA实现IIC协议的设计

IIC总线为什么是半双工?

【CW32学习笔记】IIC接口-主机发送

解析IIC专题原理及应用篇(一)

解析IIC专题原理及应用篇(一)

评论