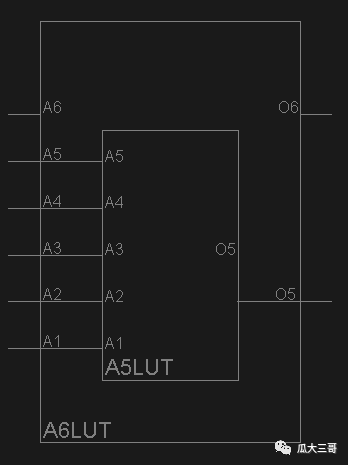

在 7 系列中实现数字电路的与、或、非等逻辑是通过 6 输入的查找表实现的。LUT 有 6 个输入(A1~A6)和 2 个输出(O5~O6)。在一个 Slice 中,四个 LUT 分别是 A,B,C,D。

一个 6 输入 LUT 使用:

A1~A6 输入

O6 输出

两个 5 输入或者更少使用:

A1~A5 输入

A6 输入为高

O5 和 O6 输出

这里小编需要说明的是,这些 LUT 输出相当于真值表值,所以学会数字电路这里理解起来就很方便。

在芯片上表现如下图

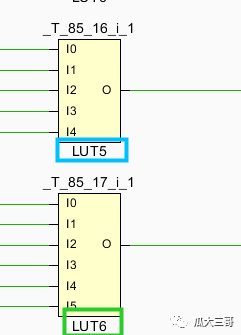

实际工程中综合后网表中表现如下图

当 LUT6 作为两个 5 输入 2 位输出时,A6 被强行写为1,MUX 选择一个 LUT5 的输出结果到 O5,另一个 LUT5 的输出结果到 O6。

当 LUT6 作为 6 输入,1位输出时。一个 LUT5 存放 A6 = 0 时的结果,另外一个 LUT5 存放 A6 = 1 时的结果,通过 MUX 可以组成 LUT6 输出 O6。

除了基本的 LUT 之外, Slice 还包含三个选择器:F7AMUX, F7BMUX, 和 F8MUX。

F7AMUX 用来产生 7 输入的功能,它的输入来源于 LUT A 和 LUT B。

F7BMUX 用来产生 7 输入的功能,它的输入来源于 LUT C 和 LUT D。

F8MUX 用来产生 8 输入的功能,它的输入来源于 F7AMUX 和 F7BMUX 。

编辑:jq

-

数字电路

+关注

关注

193文章

1630浏览量

80897 -

LUT

+关注

关注

0文章

50浏览量

12597 -

Mux

+关注

关注

0文章

38浏览量

23471

原文标题:Look-Up Table(LUT)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

解析数字电路的与、或、非等逻辑是通过 6 输入的查找表实现

解析数字电路的与、或、非等逻辑是通过 6 输入的查找表实现

评论