1 引言

如今,随着集成电路工艺发展到深亚微米的阶段,处理器体系结构的设计研究正朝着多 核的方向发展。Intel、IBM、SUN 等主流芯片产商已经在市场上发布了自己的多核处理器。 目前多核处理器的发展尚处于起步阶段,有很多问题还有待解决。其中,一个十分重要的方 面就是设计高效的片上通信架构。多个内核上同时执行的各个程序之间可能需要进行数据 共享与同步,因此多核处理器的硬件结构必须支持各个CPU 内核之间的通信。一般说来, 异构多核处理器和同构多核处理器在通信机制的设计上有着不同的考虑。异构多核处理器通 常是针对嵌入式系统的应用,主要存在着总线、存储控制器、共享存储区等通信机制。

异构多核处理器系统的几种主要通信机制,事实上都可以通过一个共享存储区来实现,例如邮箱、消息、信号量实际上都是以共享存储区作为传播载体。同时,也考虑到 SystemC 的设计方法可以支持设计者在不同层次上建模减小了代码量和工作量,提供了更高的工作效 率。因此本文在采用共享存储器通信机制的同时,基于SystemC 提出且建立事务级多核通 信模型,并利用MP3 解码程序实例证明了本模型有效的实现了多核间的通信。

2 SystemC 通信总线模型

2.1 SystemC 简介

SystemC 由C++衍生而来,在C++基础上添加硬件扩展库和仿真库构成,从而使SystemC 可以建模不同抽象级别的包括软件和硬件的复杂电子系统[4]。他的最基本的结构单元是模块 (module),模块可以包含其他模块或过程(process)和方法(method),过程如同C 语言中的函 数用以实现某一行为模块,通过接口(port) 与其他模块通信接口之间用信号(Signal) 相连。 一个完整的系统由多个模块组成,每个模块包含一个或多个过程和方法,过程是平行工作的。 基于SystemC 的设计方法支持设计者在不同层次上建模减小了代码量和工作量提供了更高 的工作效率,也就是说利用SystemC 与传统的方法相比可以更为高效快速地进行仿真。

2.2 模块细化及基于SystemC 的通信总线行为级建

模 一个典型的片上系统模型框架通常包括总线、总线仲裁器、微处理器、数字信号处理器 (L6P)、存储器和其他专用集成电路(ASIC)。这样一个复杂的系统,传统的设计办法是全部 使用C/C++进行描述以进行系统级建模和验证,然后将硬件部分的描述手工翻译为 VHDL/Verilog HDL,等硬件描述语言进行描述。等硬件全部实现后再进行软件的设计与实现。在引入SystemC 作为建模语言的情况下,整个系统可以方便地用一种语言进行描述、 建模、仿真、细化,直到最终实现。

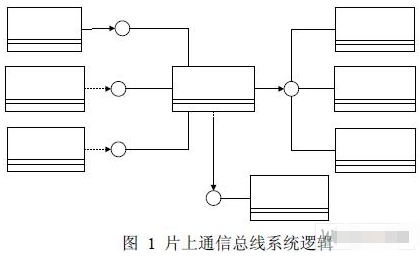

在使用 SystemC 建立片上总线行为级模型时,根据总线一般模型中各个模块的行为特 性,进行了进一步的模型细化,得出片上总线行为级模型的SystemC 模块结构图,如图1 所示。在模型细化的过程中,总线主设备被划分为直接型主设备、阻塞型主设备和非阻塞型 主设备;总线从设备被划分为快速存储器、慢速存储器和代表ASIC 的通用串口;通信总线和 仲裁器模块保持不变。

总线采用分层通道的方式实现,实现了直接型接口、阻塞型接口和从设备接口。在某些 时钟的上升沿,总线收集到来自各个主设备的从设备读写请求,并将这些请求加入请求队列。 在时钟的下降沿,总线将请求发送给总线仲裁器,由总线仲裁器根据一定的仲裁规则进行仲 裁,从请求队列中选择出合适的主设备请求并通过从设备接*由总线从设备进行服务。

3 基于异构多核的通信模块设计与实现

3.1 设计原理

按照上文中提到的总线架构,多核处理器作为通信总线的主设备而共享存储区作为总线 的从设备形成了整个系统模型,但考虑到异构多核与同构多核相比存在一个问题:即由于不 同内核的应用程序采用的是不同的交叉编译器,因此高级语言所指定的内存空间是无法做到 一致的,即便是直接写汇编程序指定内存地址,由于操作系统分配给不同模拟器的程序空间 是不同的,也无法做到共享存储。也就是说,无论是高级语言编程,还是汇编语言编程,都 要解决二进制代码和内核模拟器之间的通信。因此上文中提到的基于SystemC 的通信总线 就需要针对不同的异构多核组合进行相应的修改,缺少通用性,违反了模块设计封装化原则。

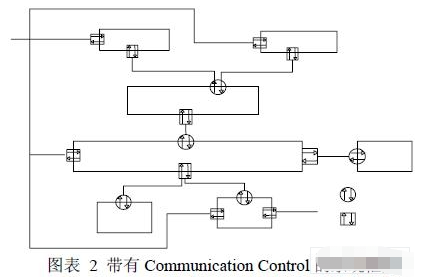

经过不断的探索和比较,本文最终采用了一种从方法学角度和可扩展性角度来看,都比 较合适的方法: 在各个处理器与通信总线之间添加一个通信控制模块(CMCCtrl-- Communication control)如图2 所示。

该模块用来专门处理各个核之间的通信指令,对其进行解释翻译,并将最终行为直观的 告诉总线,达到核间通信的目的。新架构设计按照SystemC 交易级建模(TLM)原则,为以后 多核功能的扩展性提供可能性。

3.2 通信机制

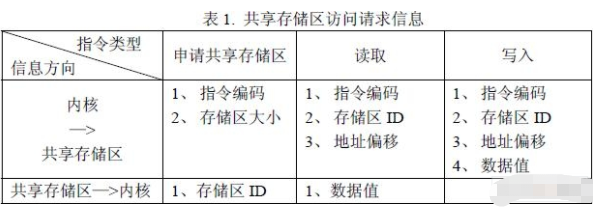

为了异构多核通信的实现,需要向多核仿真器的每个模拟器内核扩展三条访问共享存储 区的指令,分别是:申请空间、读取和写入。

在内核代码中对共享存储区访问指令进行译码之后,需要对共享存储区发出操作请求, 与操作请求一起发送的是操作的信息,对于申请、读取和写入三种操作,各自的操作信息如 下表所示:

当 CMCCtrl 受到接收到来自Core1/Core2 的访问请求,模块触发。同时随着请求一起接 收下来的其他信息,包括指令编码、请求的数据类型、地址偏移等等。CMCCtrl 对这些请求 信息进行分析,当判断出核间需要数据通信后,将需要的信息提取发送至总线模块。具体模 块描述如下:

SC_MODULE(CMCCtrl)

{ sc_inout isCore1, isCore2; //来自Core1/Core2 的访问请求,是本模块的触发信号

sc_out core1_latency, core2_latency; //返回给Core1/Core2 的延时信息

sc_inout data_value; //需要传递的数据

sc_port bus_port; //通信总线模块接口

/*返回给Core1/Core2 的应答信号,表明CORE1/Core2 获得了共享存储区的访问权,并

且可以继续执行下一个周期的操作*/

sc_inout ackCore1, ackCore2;

/*随着isCore1/isCore2 请求一起接收下来的请求信息,包括指令编码、请求的数据类型、

地址移等等*/

sc_inout data_type, array_capacity, data_index, data_id;

/*随着is Core1/isCore2 请求一起接收下来的,表明当前Core1/Core2 运行的周期数,用

于进行内核调度判断和访存冲突分析*/

sc_in core1_cycle, core2_cycle;

/*对isCore1 或者isCore2 的上升沿敏感的响应函数,它被定义为线程类型,是CMCCtrl

类的实现函数。函数内部需要对两个内核的访问请求进行判断、控制,并调用相应的其

它成员函数。*/

void Controller();

//对于每一个write_shm_data 请求,将数据写入指定的共享存储区空间

void WriteShmDataHandler(struct InstBuffer *inst);

//对于每一个read_shm_data 请求,将数据写入指定的共享存储区空间

void ReadShmDataHandler(struct InstBuffer *inst);

……

SC_HAS_PROCESS(CMCCtrl);

// constructor

CMCCtrl (sc_module_name _name){……}

};

4 MP3 解码程序的多核测试

为了更加充分进行验证,并展示多核通信模块在实际应用中的价值,本文选择了MP3 解码程序进行基于多核系统的移植,并验证仿真结果以及仿真效率。

MP3编码的主要方法是在频域上对音频文件内容进行编码压缩,而解码过程是还原频域 的内容再变换成原始的时域音频信号。按照ISO/IEC11172-3标准,MP3解码算法分为同步与 校验、Huffman解码、比例因子解析、反量化、重排序、立体声处理等十个部分。

在考虑应用程序的多核移植时,可以是数据划分也可以是任务划分的。对于MP3代码, 如果采用数据划分式,则可以在不同的处理器内核上解不同的数据帧。而如果采用任务划分 方式,则可以将解码的不同过程在多个内核之间形成流水作业,采用共享存储区进行不同流 水级之间的数据传递。显然后者需要更多的核间通信,更适合于验证其性能,因此,本文采 用了按照任务划分的方式进行代码的多核移植。

在测试中,我们采用ARM+PISA的双核系统,因此需要将MP3解码程序按照功能划分为 两部分,分别放在两个内核上运行,形成流水线。本文所采用的MP3解码软件在ARM开发 套件(ARM Design Suit)软件仿真平台上测试的结果表明:合成多项滤波器部分占用了大 约50%的计算量。根据这个结论,本文粗略地对应用程序在双核之间进行任务划分:其中 一个内核运行计算量最大的合成滤波,另外一个内核实现Huffman解码、比例因子解析、反 量化等步骤。两个内核通过系统提供的通信控制模块进行通信并保持同步。

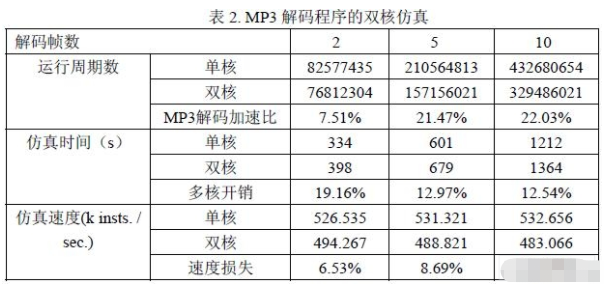

表2是这一测试的统计结果。统计数据提供了两方面的信息:

1)MP3解码程序的双核加速比,由统计结果中的“运行周期数”反映;

2)多核仿真器在进行MP3解码仿真时的仿真效率,由“仿真时间”和“仿真速度”两 项统计结果反映。

5 总结

无论考虑单位计算性能的能耗因素,还是对于提高处理器性能,多核体系结构尤其是异 构多核体系结构都是当前的热点研究方向。本文主要论述了面向异构多核处理器的片上通信设计。对于处理器的内核间通信,采用了共享内存技术。

本模型充分体现了SystemC的语言优势,对进一步了解和探讨异构多核处理器结构、核 间通信、异构多核低功耗设计等方面打下一定基础。

本文作者创新点: 提出了一种基于SystemC的异构多核通信架构模型,并通过添加控制 模块解决异构多核间通信通用性问题。

责任编辑:gt

-

处理器

+关注

关注

68文章

19349浏览量

230377 -

芯片

+关注

关注

456文章

50968浏览量

425046 -

存储器

+关注

关注

38文章

7514浏览量

164036

发布评论请先 登录

相关推荐

【米尔NXP i.MX 93开发板试用评测】1、异构核心通信的技术内容

典型的支持多核处理器的RTOS功能解析

创龙带您解密TI、Xilinx异构多核SoC处理器核间通讯

MPU进化,多核异构处理器有多强?

【玩转多核异构】处理器对共享外设和资源的调配方法

基于OKMX8MP-C板的多核异构处理器对外设和内存资源的使用方法

多核异构处理器对共享外设和资源的调配方法

多核处理器片上存储系统研究

基于异构多核处理器和共享内存技术实现片上通信设计

基于异构多核处理器和共享内存技术实现片上通信设计

评论