Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125M驱动,伴随时钟是由125M经过Pll相位移动-90度。

设置输出时钟时,参考时钟选择相移的那个,发现不起作用,没有路径。

如果选择系统时钟,分析后是系统时钟的最大最小延时,没有相位移动后的信息,这是什么问题?

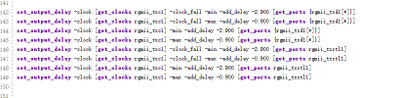

伴随时钟创建的Create_generated_clock中的Set_output_delay如下:

Txc1 是锁相环移动相位后直接送到输出管脚,Rxc1是驱动数据的。

数据输出路径以及对应的Clock的连接Schematic截图

Txc是Rx经过锁相环再经过oddr生成的

数据输出是Rxc驱动Oddr打出来的

软件认为这个时钟没有路径,这个问题在ISE上也遇到过,软件时钟始终不认伴随时钟

A1

ISE约束和Vivado的约束用法不同,Create_generated_clock的source指定的net是哪一段,改为用get_pins指定的ODDR的C pin试试。Report_clocks结果查一下你的clock约束都生效了吗?

Q2

指定Obuf的O管脚和Edit Constraints重新编辑后,约束成功了,请问原因是什么?create_generated_clock在set_output_delay约束的签名,有时候把锁相环输出的bufg改成no buffer但是生成的网表里仍然有,关闭再打开就没了,但时序分析路径却有这个bug。

A2

是不是synthesized design没有reload?如果synthesized design 已经是打开的情况下,修改设计重新synthesize,已经打开的synthesized design会提示需要reload,否则是修改之前的结果

如果发生约束没有约束上的问题,可以查一下messages窗口里的critical warning或warning,看是否有提到关于这条约束的问题。

也可以在synthesized design或者implemented design的tcl console里,report_timing用-from -to指定路径起始点来report下相应path看是如何分析的,可以从分析结果看下是path不存在还是约束有问题。

如果用edit constraints重新编辑并保存就好了,很可能是原来手写的约束哪里有问题

原文标题:本周一问 | Vivado 的XDC设置输出延时

文章出处:【微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

Xilinx

+关注

关注

71文章

2167浏览量

121550 -

Vivado

+关注

关注

19文章

812浏览量

66605

原文标题:本周一问 | Vivado 的XDC设置输出延时

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

VIVADO的调试窗口IAL监测到AFE5816输出电压大了一倍,怎么解决?

U50的AMD Vivado Design Tool flow设置

Vivado使用小技巧

延时开关怎么调时间长短

延时开关上l和a是什么意思

延时继电器工作原理及应用实例

如何设置三菱变频器的输出输入频率

Vivado编译常见错误与关键警告梳理与解析

详解Vivado非工程模式的精细设计过程

Vivado的XDC设置输出延时问题

Vivado的XDC设置输出延时问题

评论