随着摩尔定律的逐渐失效,缩小芯片尺寸的挑战日益艰巨。但随着新工艺和技术接连涌现,芯片设计规模仍在持续拓展。其中一种方式就是采用3DIC,它将硅晶圆或裸晶垂直堆叠到同一个封装器件中,从而带来性能、功耗和面积优势。由于它能够同时实现极端、异构和同构的集成,3DIC适合支持计算密集型工作负载,并提供了 2D 架构所不具备的密集性和可扩展性。

3DIC设计面临哪些挑战?

3DIC给AI、5G、数据中心、大型网络系统、高性能计算等领域带来变革的同时,也面临着不少挑战。从2D架构升级为3D架构,设计人员往往习惯于沿用自己熟悉的一套既定方法、工具和工作流来开发 SoC。这种思维定式导致设计人员在高度碎片化的环境中创建2.5D和3DIC设计,其中充斥着大量单点工具解决方案。目前,设计人员依然只能执行以人工操作为主的评估,由于缺乏综合性的分析和反馈,这项任务既繁琐又易出错。

另一项挑战在于,在整个设计流程中,各参与团队的工作流效率和效力,这涉及架构、设计、实施、IP创建/集成、封装等团队。比如,在以往的2D环境中,将完成的芯片级设计转交给封装团队,这是一个相对简单的步骤。然而对于3DIC而言,这一环节有更多的反复,因为得出的设计可能达不到更加严格的封装要求。

拥有超高收敛性环境的一体化3D设计应运而生

现有的各种单点工具只能解决复杂的3DIC设计中细枝末节的难题,更加高效的解决方案是采用统一的平台,将系统级信号、功耗和散热分析集成到同一套紧密结合的解决方案中。

新思科技通过3DIC Compiler为多裸晶片集成提供了统一的平台,为3D可视化、路径、探索、设计、实现、验证及签核提供了一体化的超高收敛性环境。该平台建立在新思科技Fusion Design Platform高度可扩展的通用数据模型之上。该平台在提高效率的同时,还可以扩展容量和性能,以支持实现数十亿个裸晶间互连。该平台提供全套自动化功能的同时,还具备电源完整性、注重优化散热和降噪,从而减少迭代次数。

3DIC Compiler可以让用户切实体验到裸晶芯片在先进节点表现的巨大设计生产力优势,周转时间从几个月缩短为仅仅几小时。此外,新思科技与Ansys达成合作,以 Ansys芯片封装协同仿真工具为3DIC Compiler提供内部设计支持,从而提供全面的信号和电源完整性分析。

原文标题:为解决3DIC芯片设计难题,3DIC Compiler应运而生!

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

458文章

51419浏览量

428636 -

IC

+关注

关注

36文章

5995浏览量

176509

原文标题:为解决3DIC芯片设计难题,3DIC Compiler应运而生!

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

将2.5D/3DIC物理验证提升到更高水平

产业"内卷化"下磁性元件面临的机遇与挑战

芯和半导体邀您相约IIC Shenzhen 2024峰会

天马微电子受邀出席DIC EXPO 2024

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

天马斩获“DIC国际显示技术创新大奖”

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

维信诺斩获2024 DIC AWARD 7项大奖

京东方携创新显示技术亮相DIC 2024

天马携多款创新型显示产品强势亮相DIC EXPO 2024

新思科技与台积公司深度合作,推动芯片设计创新

全光网应用面临的挑战

人工智能芯片在先进封装面临的三个关键挑战

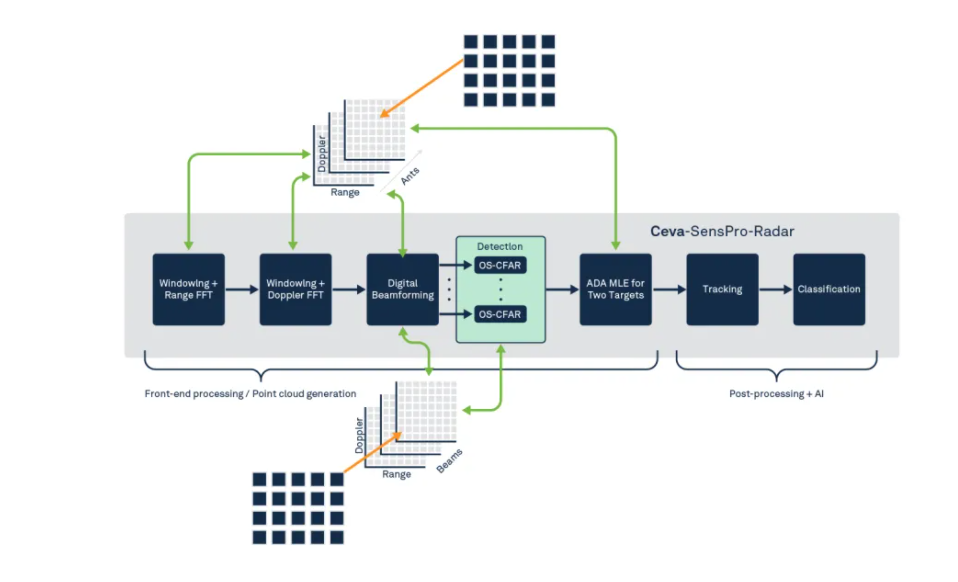

汽车雷达系统设计面临的挑战

现在3DIC设计面临哪些挑战?

现在3DIC设计面临哪些挑战?

评论