无线定位技术是利用无线信号来判定某一半径范围内无线信号发射终端物理位置的一种方法。移动通信网络中移动终端的定位方法可分为两大类:一类是基于手机的定位方法,通过在每个移动终端(如手机)内部安装微型GPS接收器进行定位。另一类是基于网络的定位方法。这种方法与基于移动终端的定位方法正相反,该方法根据移动终端发出的信号到达基站的参数,如到达时间(TOA)参数、到达角度(DOA)参数等进行定位。基于网络定位的方法需要用到阵列天线,阵列天线传感器接收到的无线信号经过前端预处理进行放大、取噪,然后进行模数转换,最后DSP对接收数据进行处理得到方向估计。

因为TMS320VC5402(以下简称C5402)内部没有集成A/D,因此在数据采集时需要使用A/D转换芯片,A/D芯片与C5402的接口设计成为一个重要的问题。为了充分利用C5402所提供的多通道缓冲串口资源,简化系统设计,本系统利用两片C5402来完成四路数据采集,大大提高了串口工作效率。TMS320C54x系列DSP芯片只有同步串口,通常只能用于与具有同步通信接口的外设进行通信。本系统中采用TI公司的的异步通信芯片TL16C550C完成数据的串/并、并/串变换,实现DSP与PC机的高速串行通信。本文在实际经验的基础上,给出了两片DSP组成的无线定位模拟系统,分别介绍了系统中串行A/D TLV1572、异步串行通信芯片TL16C550C的工作原理,同时分析了系统独立工作的程序装载原理和可行性。

系统主要器件和原理介绍

串行A/D芯片TLV1572

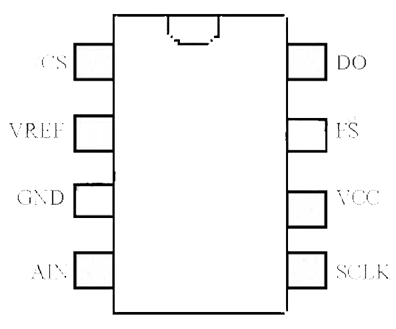

TLV1572是TI公司生产的高速十位串行A/D转换芯片。TLV1572采用的是8脚的SOIC封装,如图1所示。TLV1572所要求提供的供电电压在3V-5V之间,TLV1572的最小参考电压为2.7V。在5V供电时,最高转换速度为1.25MSPS,在3V供电时最高转换速度为625KSPS。为了使其达到最大的转换速率,所提供的时钟分别为20MHz和10MHz。TLV1572可以通过3或4个串行口线直接与DSP或其它数字微处理器串口相连,不需要外加逻辑,但是转换速度受SCLK供给时钟的限制。TLV1572与DSP的多通道缓冲串口通过/CS、SCLK、DO和FS四条线相连,此时DSP的CLKR产生移位脉冲,FSR产生帧同步信号,并分别提供给TLV1572。当TLV1572与其它串口微处理器相连接时FS必须提供高电平,通过/CS、SCLK、DO三条线来完成数据传输。当/CS为高时,A/D芯片各管脚处于三态状态。在/CS由高变低时,TLV1572检测FS引脚的状态来确定工作模式,若FS为低则为DSP模式,若FS为高则为其它微处理器模式。

图1 TLV1572引脚图

当TLV1572工作在DSP模式时,必须保证在/CS变低时,FS为低电平,并且要锁存一定时间。/CS为低时,DO跳出三态状态,但是直到FS为高时芯片才脱离休眠状态。TLV1572在每个时钟SCLK的下降沿检测FS的状态,一旦检测到FS为高,TLV1572开始采样。在FS的下降沿,A/D芯片通过移位时钟将数据移到DO上。在6个前导0传送之后,DSP可以在时钟的下降沿得到A/D转换的数据,如图2所示。在最低位移出之后,A/D芯片自动进入休眠状态,直到FS下一次有效。如果FS在16位传输完成后立即有效,则A/D开始新的数据转换,此时A/D为连续转换。若FS在TLV1572转换数据的过程中变高,则A/D芯片被复位,开始新的数据转换周期。因此可以通过设置FS改变数据传输的位数。

异步通信芯片TL16C550C

TL16C550C是TI公司的异步通信芯片,具有与DSP的连接硬件简单,使用经济、可靠的优点。其主要特点如下:管脚与TL16C450兼容;可由软件设定16字节的FIFO以减少CPU中断;波特率发生器可编程;具有可编程的串行数据发送格式;数据位长度为5、6、7、8;具有偶校验、奇校验或无校验模式;停止位长度为1、1.5、2;采用44引脚PLCC封装。

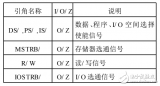

TL16C550C内部共有11个寄存器,这些寄存器分别用于实现通信参数的设置,对线路及MODEM的状态访问,数据的发送和接收以及中断管理等功能。在编程过程中,可由A0、A1、A2 三条片内寄存器选择线和线路控制寄存器(LCR)的D7位(DLAB)一起访问或控制TL16C550C的任何一个寄存器。表1给出了访问这些寄存器时DLAB和A0、A1、A2的状态。因为接收和发送缓冲寄存器的DLAB、A0、A1、A2各位都相同,因此还必须通过读写信号来加以区分。

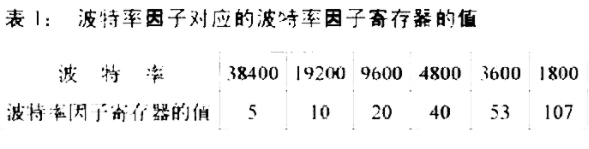

因为接收/发送缓冲寄存器和中断使能寄存器分别与波特率因子寄存器的低位和高位相同,要通过DLAB加以区分,可以任意选择写入波特率因子的高字节和低字节的顺序,写入前必须置LCR的DLAB位为1。写入波特率因子后应将D7置为0,以便访问其他寄存器。在外接晶振为3.072MHz时,几种常用的波特率所对应的波特率因子寄存器的值如表1所列。

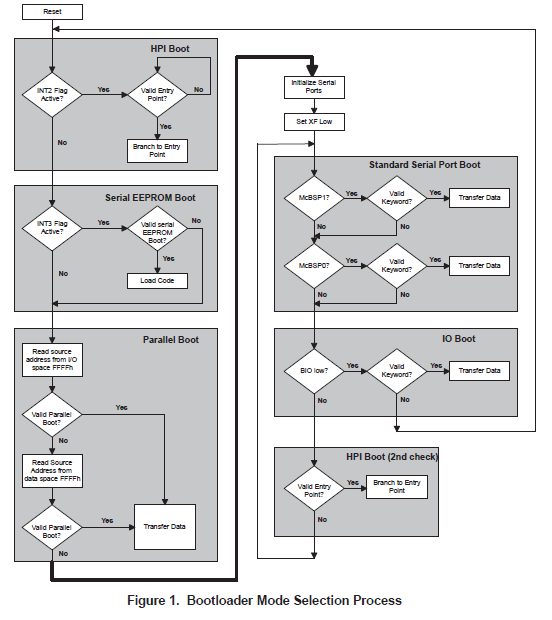

C5402的Bootloader原理

C5402上电后,首先检查MP/MC引脚的状态:如果为高电平,说明DSP处于微处理器工作模式,从外部程序存储器0FF80h地址开始执行用户程序;若为低电平,DSP被设置为微计算机模式,从片内ROM的0FF80h地址开始执行程序。在C5402的0FF80h地址处存放着一条跳转至0F800h处执行DSP自行引导装载(Bootloader)程序的指令。当C5402执行Bootloader程序时,将会按HPI装载模式→串行EEPROM装载模式→并行装载模式→标准串行口装载模式 →I/O口引导装载模式的顺序循环检测,以决定执行哪种启动模式。

对于以C5402为核心的数字信号处理系统来说,并行引导装载模式被认为是最适用的。因为HPI引导装载模式、标准串行口引导装载模式和I/O口引导装载模式只适用于由其它处理器为C5402提供运行代码的多处理器系统中,串行EEPROM引导装载模式只支持价格偏高的SPI端口EEPROM,而并行引导装载模式可采用的并行EEPROM和Flash种类很多,有的价格比较低,操作起来比较简单。在不自己编写Bootloader程序的情况下,并行引导装载模式最大只能装载32K字的程序或数据。若程序数据大于32K,此时需要自己编写一个并行装载的内核程序,通过片内的装载程序将编写的内核程序传送到片内DRAM中,然后再运行装载内核程序,将大于32K的程序数据送到片外的SRAM中。在有两个或两个以上的C5402或具有标准串口功能的多微处理器的系统中,若为每一个微处理器都配置一个并行的Flash来存储程序,会很浪费资源,占用总线。而利用一片Flash,主机利用并行装载,然后主机通过HPI装载模式对其它C5402进行装载,这样就可以节省大量资源。

系统硬件结构及原理分析

系统硬件原理图

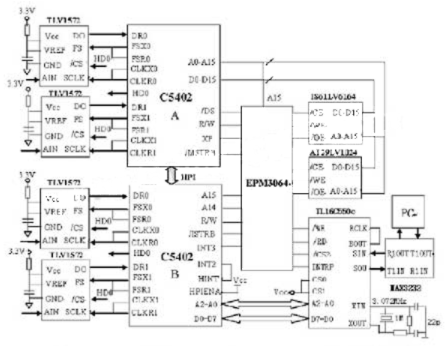

本系统主要完成无线信号的采集、采样信号的处理得到方向估计及与PC机通信,系统的硬件原理如图2所示。

图2 CPLD中的VC5402与TL16C550C的系统逻辑图

数据采集与通信

为了达到与C5402很好的匹配,A/D电源和参考电压都接了3.3V。A/D的FS接DSP的FSX和FSR,使数据输入的帧同步信号由DSP产生。SCLK接DSP的CLKX和CLKR,这样数据的输入和输出时钟均来自DSP。C5402与各自两片A/D进行数据传输时,设置串口中断工作在00模式,即串口数据到达触发中断,这样CPU可以根据A/D传输数据产生相应的串口中断RINT0或RINT1。当两个串口的数据同时到达,即同时申请中断时,C5402的CPU会根据中断优先级响应RINT0中断,然后再响应中断RINT1。为了保证数据通信的可靠性,避免数据冲突,在响应RINT1中断的过程中,串口0无中断请求。 两片C5402(A,B)是通过HPI口进行数据交流的,其中C5402(A)作为主机,C5402(B)工作在HPI 模式。两片DSP分别计算自己的数据的自相关函数Rxx,由C5402(A)将数据送到C5402(B)中,进行互相关函数Rxy计算,然后通过ESPRIT方法计算出方向。估计完方向后,C5402(B)通过TI公司的异步串行芯片TL16C550C将估计结果传给PC机进行网络定位,或下一步处理。

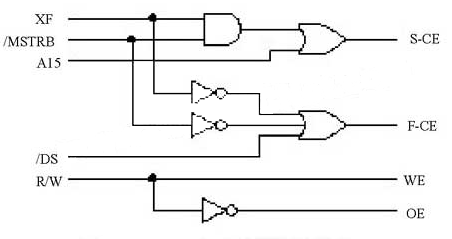

TL16C550C能以16MHz的速度读写数据,读写信号的脉宽很窄,使用一般的串口微处理器误码率较高,而TL16C550C能够很好的与DSP匹配。这里VC5402以19200的波特率与PC机通信, 当XIN、XOUT端外接3.072MHz晶振时,波特率因子寄存器的低位的值应为0AH,高位值为00H。C5402与TL16C550C之间的逻辑控制通过CPLD来完成,其内部逻辑如图3所示。

图3 CPLD中的VC5402与TL16C550C的系统逻辑图

由于RS-232-C电路电平与CMOS电平不同,因此RS232驱动器与CMOS电平连接时必须经过电平转换,本系统采用MAXIM公司的MAX232来完成这一功能。

系统独立工作的程序装载过程

本系统的程序装载分为两部分:C5402(A)自身的并行装载和C5402(B)的HPI装载。

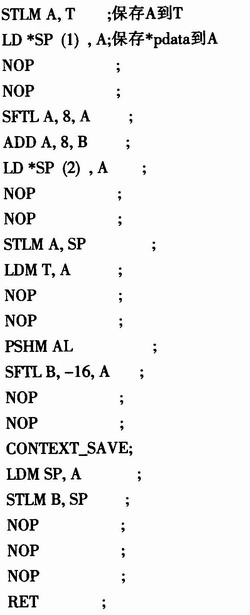

C5402(A)与Flash AT29LV1024和SRAM IS61LV6164之间的逻辑如图4所示。C5402(A)上电复位装载时,由于Bootloader程序在初始化时设置XF为高电平,在系统进入并行引导装载模式后,C5402(A)从数据寻址为0FFFFh单元(A15=1,选中Flash)中读取将要载入的程序存储区首地址和并行装载数据流。此时,C5402可以将 Flash地址08000h-0FFFFh单元中的数据读到C5402对应于0000h-7FFFh寻址区的片内DARAM和片外SRAM中。Bootloader程序结束后用户程序的第一条语句为RSBX XF,置XF引脚为低电平, Flash始终不选通。这样,SRAM的高32K区域(08000h-0FFFFh)被释放出来,可以作为C5402(A)运行时的数据区或程序区使用。C5402(A)装载进来的程序数据主要分三部分:给C5402(B)的装载程序,自身的运行程序及C5402(B)的运行程序。

图4 VC5402与存储器的逻辑图

在C5402(A)进行并行装载的过程中,C5402(B)在判断是哪种装载模式。因为C5402(B)的HINT和INT2连在一起,在DSP上电初始化时将07FH单元清0,同时HINT置0,这样导致了INT2的IFR的相应标志位有效,C5402(B)查询到INT2的标志位有效后,判断是HPI装载模式。C5402(A)在进行完并行装载后,首先运行装载程序,将C5402(B)运行程序数据传送C5402(B)中,最后将C5402(B)的程序入口地址写到07FH单元,表明HPI装载结束。

系统软件设计

系统的软件设计主要包括,多通道缓冲串口的初始化,串口中断服务程序,并行装载程序设计,TL16C550C的初始化及HPI设计等。

程序设计应注意的问题

(1)McBSP工作在数据接收中断方式,因此全局中断和串口中断的相应位应该合理设置。同时,在设置中断向量表时,使中断向量表的位置与处理器模式状态寄存器PMST中的中断向量指针IPTR相对应,使IPTR的9位地址指向128字的中断向量所在的程序页,同时,中断向量表要严格按照C5402规定的格式编写,否则不能正确地产生需要的中断结果。

(2)要实现DSP数据采集系统的脱机独立运行,程序装载十分关键。C5402(A)进行并行装载,要求AT29LV1024中的程序数据流严格按照并行装载的格式,依次给C5402(B)装载程序、C5402(A)自身执行程序,C5402(B)的程序装载到片内DRAM和片外SRAM中。

(3)注意到系统设计中,C5402(B)的HPI口既用来进行程序装载,又作为两片DSP通信接口,为了避免混乱,在C5402(B)的程序中应将IFR中INT2的相应位清零,最好在IMR中屏蔽INT2。

(4)为了实现两路A/D和C5402之间的时序匹配,避免数据冲突,需要注意C5402采样率发生寄存器SRGR1中CLKGDV位的设置,使C5402工作时钟周期大于两个串口中断的响应时间。

TL16C550C的软件流程

TL16C550C 初始化程序主要完成波特率及其它工作寄存器的设置。这里设置TL16C550C工作模式为8位数据位,2位停止位,奇校验状态。TL16C550C的软件设置流程如图5所示。

图5 TL16C55C工作的软件流程(略)

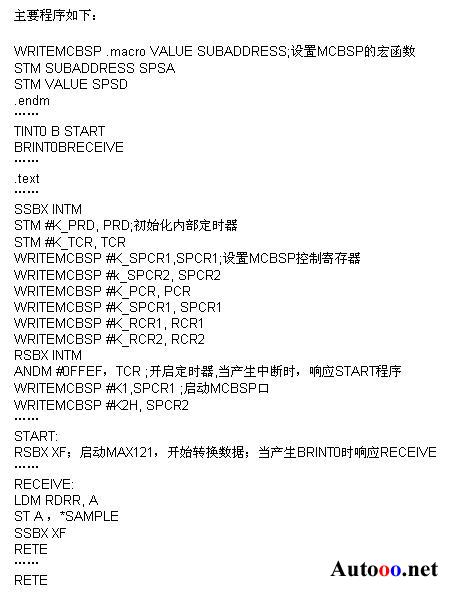

串口接收的部分初始化程序

下面根据多通道缓冲串口的特性和两路串行A/D工作的要求,主要介绍一下串口接收的软件设计和串口部分关键设置。

;=====初始化串口0========

stm #0, SPSA0

stm #0000h, SPSD0 ; #0000H SPCR10

stm #1, SPSA0

stm #0000h, SPSD0 ; #0000H SPCR20

stm #2, SPSA0

stm #0040h, SPSD0 ; #0040H RCRC10 每字16位

stm #3, SPSA0

stm #0040h, SPSD0 ; #0040H RCR20 每帧一段,每段一字

stm #6, SPSA0

stm #000fh,SPSD0 ; #0009H SRGR1 时钟周期 CLKG=“6”.4MHz

stm #7, SPSA0

stm #300fh, SPSD0 ; #3010H SRGR20 帧周期为16个CLKG

stm #0eh,SPSA0

stm #0a04h, SPSD0 ; #0A04H PCR0 FSX, CLKX输出,FSR,

CLKR输入

;=====初始化串口1======

串口1的初始化程序参见串口0

;=====启动接收========

stm #0,SPSA0

stm #0001h, SPSD0 ;启动串口0接收

stm #1,SPSA0

stm #00c0h, SPSD0 ;内部产生时钟产生FSG

stm #0,SPSA1

stm #0001h, SPSD1 ;启动串口1接收

stm #1,SPSA1

stm #00c0h, SPSD1 ;内部产生时钟产生FSG

;==串口0接收中断子程序===

.sect “brint0”

host_brint0:

rsbx intm ;关中断

ldm drr0,A

stl A,*ar4+ ; 接收

:::

其它处理程序

rete

结束语

本文利用两片DSP,根据TM320C5402多通道缓冲串口的特点,提出了由四个阵列天线传感器阵元组成的DOA估计硬件设计方案,并给出了系统独立工作的硬件原理图和软件设计的部分关键程序。并行装载模式和HPI装载模式同时使用,有效利用了系统资源,减小成本,同时TL16C550C的使用实现了DSP与PC机的高速串行通信。

责任编辑:gt

-

处理器

+关注

关注

68文章

19244浏览量

229596 -

dsp

+关注

关注

553文章

7984浏览量

348687 -

无线

+关注

关注

31文章

5447浏览量

173222

发布评论请先 登录

相关推荐

HPI方式自举在TMS320VC5402 DSP芯片上的实现

在TMS320VC5402处理器上怎么移植μC/OS-II操作系统?

怎样去设计TMS320VC5402与模拟芯片TLC320AD50C的接口?

基于TMS320VC5402 的DSP基本系统的设计

MAX121与TMS320VC5402在高速数据采集中的接口

μC/OS-II在TMS320VC5402上的移植

TMS320VC5402和TMS320UC5402引导加载程序的特点和操作详细概述

TMS320UC5402和TMS320VC5402数字信号处理器硅勘误表详细分析概述

TMS320VC5402 数字信号处理器

基于TMS320VC5402处理器实现无线定位模拟系统的设计

基于TMS320VC5402处理器实现无线定位模拟系统的设计

评论