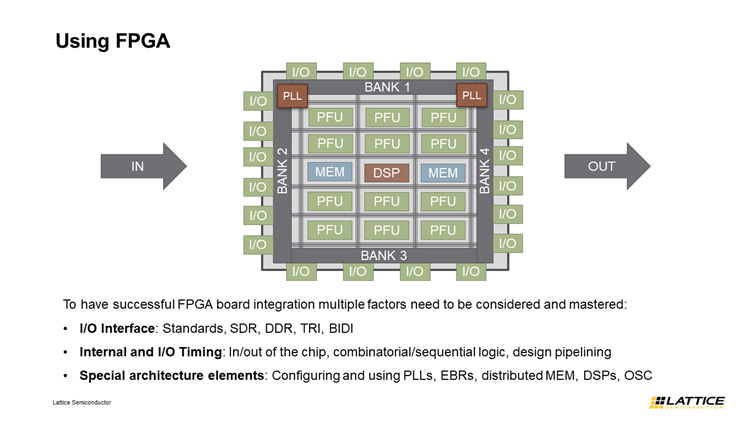

近年来,伴随国内芯片市场迅猛发展,芯片的验证、仿真、测试需求也随之增大,且复杂度大大提升。在此情况下,国内市场大规模芯片验证平台短缺以及性能不足的问题日渐凸显。 2019年8月,赛灵思推出最大容量 FPGA —— Virtex UltraScale+ VU19P。其拥有 350 亿个晶体管,具备有史以来单颗芯片最高逻辑密度和最大I/O 数量,可以支持未来最先进 ASIC 和 SoC 技术的仿真与原型设计。与此同时,还广泛支持测试测量、计算以及网络等相关应用。

高端 FPGA 新标杆显著提升开发效率

作为全球第一代使用 FPGA 芯片的企业之一,新致华桑电子始终致力于将最先进的 FPGA 技术应用于其 PHINEDesign FPGA 原型开发平台。该平台的前三代均基于赛灵思 FPGA 平台而开发。

在赛灵思 VU19P 推出之初,新致华桑便加入产品早期试用计划,并将其应用到第四代原型验证平台的研发设计中。2020年底,新致华桑基于赛灵思 VU19P 的第四代 PHINEDesign 平台——NE-VU19P-LSI应运而生。

新致华桑 NE-VU19P-LSI 将一些 ASIC 原型或大规模 SoC 开发的验证效率提升高达了 30%。对于需要大规模验证的客户,新平台可以节省近50%的资源分区工作量,从而大大缩短验证周期,加快客户的产品上市时间。

新一代 NE-VU19P-LSI 平台具备诸多领先特性

•总计超1800个 I/O,通过 FMC 标准连接器接出,可兼容赛灵思等各大厂商标准子卡,为用户提供了丰富扩展接口选择;同时新致华桑也为客户配备了适用于原型验证的各种FMC子卡。•48路高速 GTY 收发器,最高可达25Gbps。可通过 FMC 或者 SLIMSAS 扩展。保证了高速 SERDES 的性能,同时接口形态更便于多系统的级联扩展,而不会造成管脚的冗余。•电压可调的 FMC I/O,可适配多种外部接口调试。•可扩展多路 DDR4/DDR3 等存储卡,速率可达 FPGA 标称2400Mbps。•丰富的全局时钟与复位资源,可支撑各种频率的应用场景。能够满足多时钟域的验证需求,又能够满足多颗互联时的时钟同源要求。•灵活的上位机管理软件,提供界面化直观便捷操作。•同时提供命令行执行方式。

自2014年以来,赛灵思便与新致华桑展开紧密合作,以全球最顶尖的 FPGA 持续助力新致华桑为国内用户带来最先进的 FPGA 验证平台。在未来,双方将继续协作,为当今爆发式增长的 5G、医疗、消费电子等领域的相关 IC 设计提供强大支持。

原文标题:保障高效 IC 设计的秘诀

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1630文章

21761浏览量

604405 -

芯片

+关注

关注

456文章

50967浏览量

424903 -

IC

+关注

关注

36文章

5965浏览量

175809

原文标题:保障高效 IC 设计的秘诀

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Triton编译器如何提升编程效率

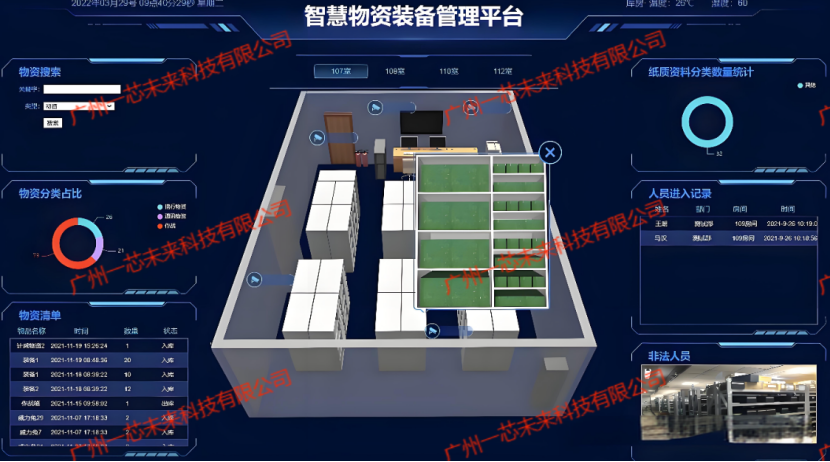

RFID技术赋能民兵装备管理,仓储效率显著提升

正点原子fpga开发板不同型号

数字孪生如何提升产品开发效率

中高端FPGA如何选择

工业触摸显示屏在提升生产效率、降低成本等方面具有显著优势

Cognizant与Google Cloud深化合作,提升软件交付效率

fpga开发是什么意思

fpga开发板是什么?fpga开发板有哪些?

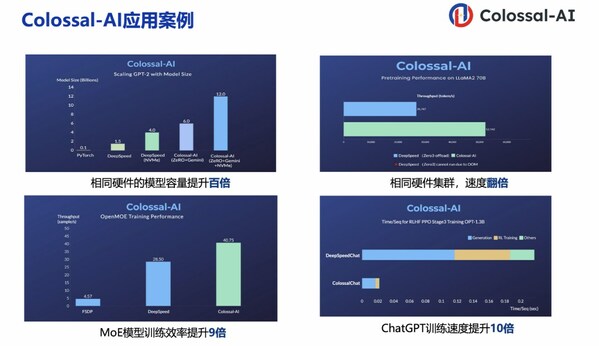

潞晨科技Colossal-AI + 浪潮信息AIStation,大模型开发效率提升10倍

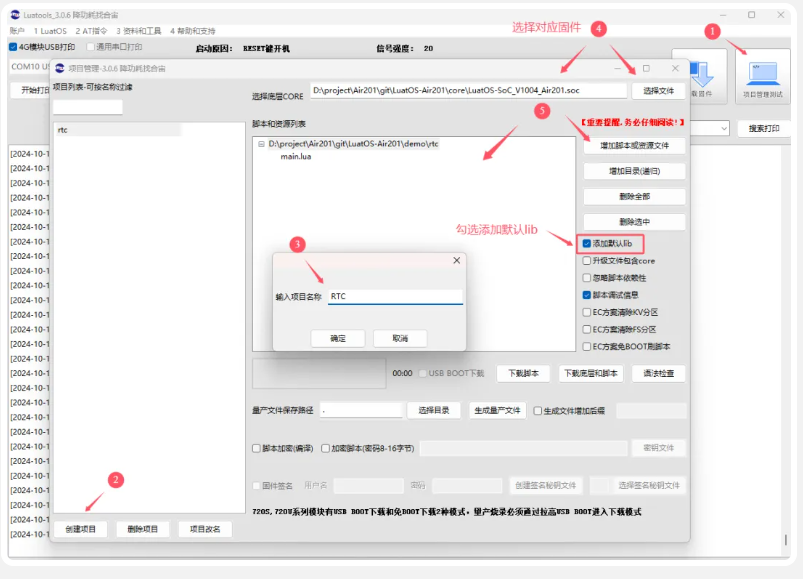

Lattice Insights 简化FPGA设计和开发

高端FPGA新标杆显著提升开发效率

高端FPGA新标杆显著提升开发效率

评论