伴随着导航系统功能日益多样化、软件算法愈加复杂和集成度要求更高的趋势,在大规模可编程器件上设计、验证和测试导航SoC芯片成为解决方案之一。导航系统SoC芯片设计的要求主要有:

①安全性。芯片的所有功能模块运行正常,运行机制透明,可靠性强。

②可配置性。根据应用要求对硬件进行裁减和配置,达到最佳的功能、功耗和面积比。

③高运算能力。具备在特定时间内完成复杂算法的运算能力。

SoC芯片的核心是实现运算和控制功能的微处理器。LEON是一款基于SPARC V8架构的开源微处理器IP软核,在VHDL源代码基础上,结合具体需求加入定制的运算单元和外设接口建立SoC系统。在配置灵活的LEON核上运行Embedded Linux,提供SoC调试和测试的基本平台。

1 软硬件平台构建

1.1 LEON软核架构简介

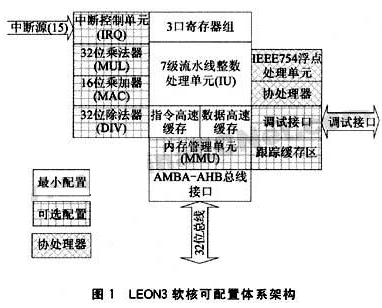

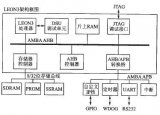

LEON核心是一个与SPARCV8兼容的整数处理单元IU(Integer Unit),LEON2是5级流水线,LEON3是7级流水线。LEON包含整数硬件乘法和除法单元、双协处理器接口(FPU浮点处理单元和Co-processor协处理器),分离的指令和数据总线(Harvard结构)。LEON通过高速的AMBA-AHB总线,指令缓存和数据缓存分别和内存控制器及高速的外部接口相连传输数据。低速的AMBA-APB总线实现片上外设的接口,例如定时器、串口、网络接口等。LEON3软核可配置体系架构如图1所示。

1.2 LEON在SoC芯片开发应用中的优势

LEON软核最突出的优势是其良好的可配置性和可移植性,以及遵循GPL许可证协议的开源性。这些特性保证导航系统SoC芯片的安全性,提供良好的性能和灵活的解决方案,也决定了在LEON上进行嵌入式操作系统移植的特殊性。

1.2.1 开源性

基于GPL许可证协议,LEON非容错版本软核IP提供VHDL源代码,仅是容错版本的LEON软核需要商业授权。源代码公开是实现导航系统SoC芯片设计安全性的前提,同时也使研究者和开发者从根本上研究软核的细节从而定制满足具体应用的软核成为可能。与全部源代码开放的LEON相比,Altera的NIOS软核等其他软核仅提供若干接口,无法在更深的软核层次上进行设计和优化。

1.2.2 优异的可配置性

LEON软核通过集成一套丰富的接口和运算单元IP库,根据具体要求来达到性能、功耗和面积的平衡和优化的目的。

①软核IU可配置参数包括流水线的深度、地址和数据高速缓存(Cache)。另外,常用指令及指令序列可以根据定制的硬件进行优化;在设计或配置新运算单元后能够对指令集进行扩展。在导航系统SoC芯片设计中,通过配置LEON的整数硬件乘除法单元以实现较高的运算性能;而在其他某些使用软件乘除法,即满足要求的应用中无需配置,以降低功耗和优化芯片面积。

②外围设备接口硬件通过挂载AMBA总线来实现。LEON3的AMBA-AHP总线上能够灵活选择集成opencores的以太网控制器和GRETH以太网控制器中的任意一个。针对导航系统中常见的1553总线接口设备,在LEON中通过配置GR1553单元完成1553总线到AMBA-AHB总线的转换,为1553总线设备的集成提供了方便。

③硬件加速单元(如特定加密算法、数字信号处理单元和浮点处理单元)根据需求集成。

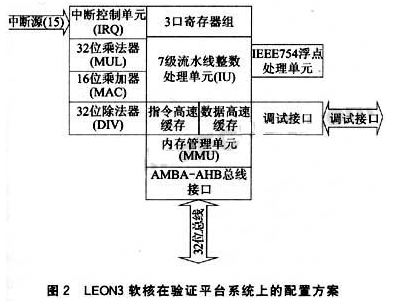

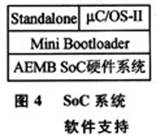

优异的可配置性带来了硬件设计极大的灵活性,也为嵌入式操作系统的移植带来了一定难度(特别是在扩展了指令集的情况下)。考虑到进行性能测试的完整性和灵活性,LEON3软核在本项目中的配置方案如图2所示。(详细配置参数未列出)

1.2.3良好的可移植性

LEON软核通过层次度分明的VHDL模型实现。通过VHDL中特定的配置接口,LEON核的关键参数(例如修改Cache的大小和组织方式,乘法器的生成,速度、芯片面积的调整以及容错方案的选择)都能够灵活设置和移植;而唯一使用专用技术的模型是内存宏模块。这一部分的设计采用了加上中间交互层接口的方式,因此移植的工作仅需重新编写中间交互层接口。导航系统中包括单次滤波在内的大量算法经过硬件实现后需集成在LEON中,根据LEON特定的配置接口即可实现集成和SoC系统移植。在本硬件平台的设计中,针对特定硬件开发板,通过修改顶层module文件设置以及更新引脚配置,即可完成硬件设计的移植工作。

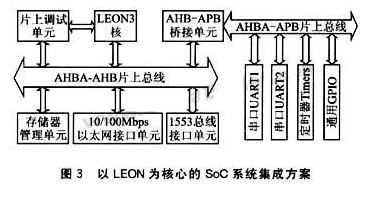

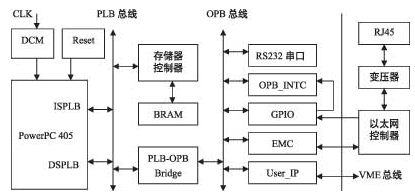

目前,LEON在研究领域被广泛应用,特别是作为软核嵌入在可编程器件中,作为构建SoC芯片的控制和运算中心。LEON软核的容错版本也已经用在了空间站上。在本导航系统SoC芯片项目中,选择了开源且配置灵活的LEON硬件平台和Linux软件平台,并且在初期测试中表现出良好的性能。在本验证平台上,SoC系统需要以太网接口、1553总线接口、串口、通用I/O口以及调试单元,具体配置方案如图3所示。

1.3 Linux系统的移植和调试

近年来Linux凭借其开源、性能优异、软件资源丰富的优势,在嵌入式平台上得到了广泛的应用。在LEON上运行的操作系统目前已经有RTEMS、eCOS、VxWorks和嵌入式Linux。选择嵌入式Linux的主要原因,是由于Linux的开发平台搭建得比较完善,在工具链、内核移植、驱动程序以及应用程序的各层上都有很好的支持;使用Linux开发能够大大加快开发的进度,并满足多数应用的指标。目前,对LEON提供良好支持的Linux发行版有Snapgear。由于LEON软核优异的可配置性和可移植性,在LEON上进行Linux的移植工作与普通定制的嵌入式微处理器相比,有很多特殊点和难点,主要表现在两个方面。

(1)配置和编译内核

编译内核的目的在于,生成在目标CPU上运行的内核。由于LEON自身硬件的可配置性,Linux的源代码中也需要加入与硬件核相关的选项进行配置。若LEON软核配置IP,例如硬件加速单元、加密单元或外设接口,则Linux内核中需加入驱动程序。因此,内核的配置分为两类,一类是配置LEON软核自身的设置,另一类是配置目标板上的其他外围设备,例如内存系统、外设接口等。与一般的定制嵌入式CPU(如ARM体系的CPU)相比,前一类配置是LEON独有的。这种配置的灵活性为软硬件平台的定制提供了极大的方便。例如,Snapgear Embedded Linux根据具体需求配置硬件乘除法指令和浮点运算单元FPU;在不需要进行浮点运算的应用中,配置LEON硬件就不需配置浮点单元,相应Linux的配置中取消FPU,进而节省硬件资源和软件的开销。

项目中实际采取的LEON软核配置方案为:LEON核选择LEON2MMU或LEON3MMU,时钟频率为50MHz,配置硬件整数乘除法指令和FPU对应的浮点操作指令。外围设备配置的串口的起始波特率为38 400 bps,另外,还配置了只读存储区ROM和随机存取器RAM。

(2)调试内核

LEON软核平台调试工具有:TSIM、GRSIM和GRMON。

TSIM:SPARC架构处理器通用软件仿真器,用于软件仿真ERC32-和LEON微处理器。

GRSIM:LEON平台软件仿真器,支持多处理器平台(MP)。

GRMON:LEON平台硬件仿真调试器,支持基于GRLIB软核IP的SoC设计的硬件调试。

TSIM作为软件模拟的VHDL模型,调试过程中常见的启动选项设置如下:

-freq:设置TSIM模拟LEON处理器硬件的工作频率,LEON3默认为50 MHz。

-fpm:配置模拟FPU模块。

-nfp:针对无FPU的模拟硬件平台关闭FPU。

-nov8:针对无硬件乘除法硬件平台关闭硬件乘除法指令。

-pr:指定使用性能观察器。

在TSIM-LEON平台上进行程序的测试和调试过程中,Profiling(性能观察器)能够显示程序各个分支函数以及宏在实际运行中占用的资源,从而为程序的进一步优化提供必要参考,例如某测试程序在程序运行完毕后使用pro命令得出的结果:

Program exited normally

tsim>pro

function rario(%)

_start 99.99

_hardreset_real 99.99

main 99.82

processl 92.90

__muldf3 56.44

__adddf3 31.14

…

宏_muldf3和_adddf3在程序运行中占用了大量时间,需进一步优化。经测试证明,通过在LEON中集成FPU消除了宏_muldf3和__adddf3,从而大幅提高浮点运算性能。

2 LEON数学运算性能及算法测试

在LEON软核系统上移植成功Linux后,通过特定测试程序验证LEON在数学运算上的性能,以确定是否满足项目开发的需求。测试中对比ARM9 SC32410,分析LEON以及其集成FPU配置的性能,并根据测试结果对软硬件配置进一步优化。由于LEON硬件配置十分灵活,因此在测试中采用了多种平台,编译程序的选项也有对应的设置。中断响应、功耗等虽然也是处理器性能的重要方面,但本文尚未涉及。

2.1 测试平台

(1)硬件测试平台

硬件测试平台如表1所列。

TSIM仿真器通过主机的浮点机制来进行浮点运算仿真,因此仿真器的浮点精度与主机平台相关。仿真器的时间精度与MeikoFPU相同,集成FPU的LEON3相当于集成MeikoFPU的LEON3。

(2)软件测试平台

①LEON2和LEON3在Linux 2.6.11下运行。

②直接使用gcc编译生成程序加载到LEON上并运行,无操作系统。

③SamsungS3C2410在Linux 2.4.18下运行。

(3)不同硬件测试平台上测试程序说明

不同的硬件平台和软件平台的搭配需在编译程序过程中指定特定选项(通过Makefile管理):

①一msoft-float选项。LEON平台上若未集成FPU,则进行浮点运算必须指定该选项,此时所有浮点运算转化为软件模拟实现,代价是运行时间大大增加,优势是能够节省硬件资源(加入FPU后LEON的LE的使用率是无FPU情况下的近2倍)。

②-mv8选项。LEON平台上配置硬件整数乘除法构件时需要指定该选项。

③sparc-linux-gcc和sparc-elf-gcc编译器。对于LEON平台,若在Linux系统上运行测试程序,则需用sparc-linux-gcc进行编译,程序使用动态链接库完成链接;若直接在LEON硬件上加载运行,则需用sparc-elf-gcc:进行编译,程序使用静态链接库完成链接。

④arm-linux-gcc:编译器。ARM9的S3C2410编译器为arm-linux-gcc。

⑤-O3优化选项。LEON和ARM的微处理器通过指定该选项进行程序算法优化。

2.2测试项目及说明

测试项目1:整型数组与浮点数组的加法、乘法及乘加运算。每种类型的运算都循环50 000次,以验证LEON各种平台和ARM9的MCU在数学运算上的性能,并分析加入Linux系统后程序运行性能的变化。

测试项目2:单次滤波算法,程序每一次运行包含12 791次浮点乘法和13 595次浮点加法,以验证在导航系统的滤波算法中LEON在多种配置下的性能。

测试程序采用clock()系统调用获取算法开始运行和结束运行的时间,并以算法的运行时间作为衡量系统效能的唯一标准。

2.3测试总结

LEON平台灵活的软硬件配置在多项测试中表现优异,总结如下:

①与主流ARM9微处理器在数学运算上性能相当。

②嵌入式Linux操作系统平台相对于无系统平台有一定资源开销,根据具体应用合理选择软件平台是否需要嵌入式Linux系统。

③指定-mv8和-03选项后程序性能提升显著,根据具体应用合理选择是否配置整数硬件乘除法器。

④LEON硬件配置FPU后浮点运算性能提高一个数量级,代价是综合需要的逻辑资源增长一倍,在权衡性能和可编程器件资源后合理选择配置方案。

结合导航系统SoC芯片高速数据处理的需求,设计方案定型为LEON+FPU,在测试中能够满足系统的运算吞吐量指标要求。

可配置FPU对LEON数学运算性能的提升极为有效,特别是在运算密集型的SoC设计中。LEON3的GRFPU相对于其他常见微处理器的FPU有较大优势。表2为若干处理器核FPU单元完成浮点运算指令需要的处理(延迟)时钟周期数对比情况口。

时钟周期数说明:括号外数字是指令处理周期数,即硬件流水线中完成该指令的周期;括号内数字是指令延迟周期数,即该指令进入流水线至从流水线中输出结果所需要的时钟周期数。

3 结论

作为硬件VHDL代码开源的SPARC架构软核IP微处理器,LEONX(包括LEON2和LEON3)良好的可移植性和可配置性使其成为建立片上系统微处理器的一个优选方案。采用Snapgear Embedded Linux的方案能够提供一个从内核、库文件到常用应用程序的验证原型。然而,LEON硬件配置上的改变、升级需要驱动程序的支持,定制的软件也需要自主开发。另外,在LEON平台上移植并运行良好的实时操作系统有RTEMS和eCOS,根据实际的需求可以灵活选择这些软件开发平台。

通过详尽的对比测试,LEON软核的性能优异,在导航系统SoC芯片原型设计中得到验证。测试为基于LEON开源可配置软核的嵌入式系统开发的软硬件配置方式提供了有益的参考,特别是集成浮点处理单元FPU的方案。随着可编程器件规模的超大型化,实现高性能且配置灵活的开源SoC硬件系统及软件平台的优势日益明显,为制造ASIC提供前期原型论证提供极大方便。

责任编辑:gt

-

处理器

+关注

关注

68文章

19723浏览量

232747 -

soc

+关注

关注

38文章

4298浏览量

220982 -

微处理器

+关注

关注

11文章

2355浏览量

83572

发布评论请先 登录

相关推荐

基于AVR 8位微处理器的FSPLC微处理器SOC设计

SoC验证平台的FPGA综合怎么实现?

怎么设计集软核处理器的嵌入式设计平台?

求一种基于FPGA的微处理器的IP的设计方法

基于IP复用设计的微处理器FSPLCSOC模块

LEON处理器结构特点

基于LEON3开源软核处理器的动态图像边缘检测SoC设计

在FPGA中利用IP核实现SOC系统中的串口收发接口的设计

基于ARM微处理器的嵌入式TCP-IP协议的实现与应用

基于LEON开源微处理器IP软核实现SoC系统基本平台的构建

基于LEON开源微处理器IP软核实现SoC系统基本平台的构建

评论