作者:Rajeev Kumar,Harpinder Singh

串行总线协议PCIe、ASI和sRIO的比较

电路板间以及背板上的数据通信越来越受到关注。由于下一代计算机、控制和通信系统的设计都是为日益提高的性能需求所驱动的,建立在共享多点并行总线协议和非标准小型封装及机架上的传统系统正在被小型模块化系统所取代。

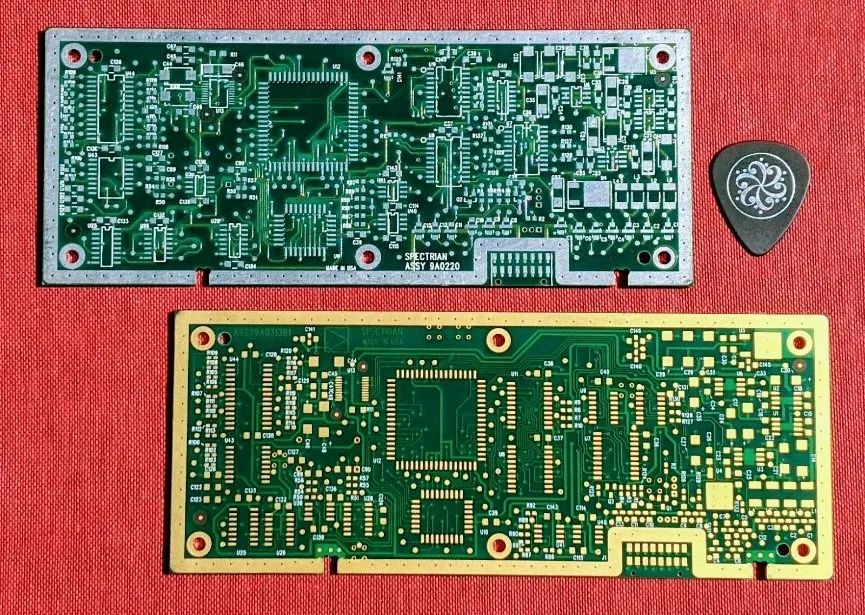

点对点的串行总线协议正在取代多点的并行总线协议。PCIe(PCI Express)和sRIO(Serial Rapid I/O,串行快速I/O)等片间串行总线互连正用于高速高密度的模块设计,甚至更小的嵌入式设计也能受益于这些新的串行互连。

背板的总线互连是建立模块化系统的关键。新的设计需要低延迟的互连,某些情况下,还需要互连具有多种QoS功能以使子系统紧密耦合。一些经销商开发了专用的背板协议,但是,随着ASI(Advanced Switching Interconnect,高级交换互连)的发展,专用背板会越来越少。

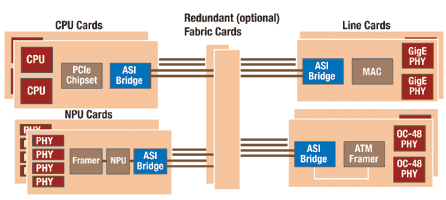

串行互连的构架

无处不在的PCI/PCI-X加载/存储外设互连总线协议使用了深度优先的层次树将I/O设备和CPU相连,PCIe是其后继者。所有设备共享一个公共存储器和I/O地址空间,数据包基于存储器和I/O地址传递。

主机CPU经主桥(或称根联合体)与I/O设备相连,或转为形成层次树。PCIe的使用正在猛增,它被广泛应用于PC、服务器、存储器和电信系统。

sRIO同样是串行加载/存储总线协议,它针对基于DSP的嵌入式应用。sRIO有一个使用邮箱或队列的信息设备,并用设备地址扩充了基于存储器地址的路由。

sRIO与PCIe的主要区别在于它具有支持点对点通信的能力;SerDes采用×1和×4的缩减的连接宽度,速率为3.125Gb/s;此外,sRIO还有原子操作等附加的数据包定义。

sRIO的其他特性包括:简单的地址分配路由、小数据包头和基于邮箱的信息机制。通过延伸这一特性就发展成了快速结构(Rapid Fabric)。

为将控制系统、计算机和通信背板整合,ASI提供了可扩展的互连。它用三层堆栈结构使物理数据传输和同步,它也使用了PCIe的物理层和数据链路层,并进行了少许的增强。

传输层提供了基于路径的路由机制,支持背板特性,并将应用空间扩展至包含路由器等通信系统。在ASI定义中包含了PI(协议接口),它为网络以及传统的或经销商定义的开隧道(tunneling)提供了传输服务。

PI网络服务基本规范包括设备管理(PI-4)、事件/错误处理(PI-5)、组播(PI-0)和拆分与重组的通用传输(PI-2),以及网络管理。ASI配套规范定义了简单排队和简单加载/存储等附加的数据运动模型。

图1 ASI构架和基于路径的路由

ASI基于路径的路由简化了交换机设计,同时也通过免除对交换机路由表的支持缩短了延迟。图1显示了典型的基于背板的ASI系统及其基于路径的路由。

总线协议的对比

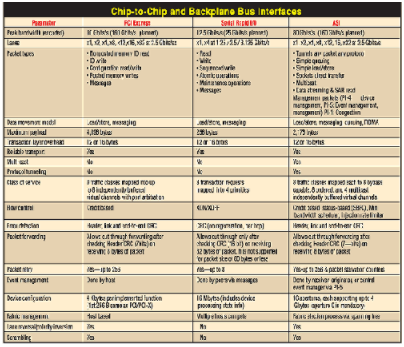

表1总结了片间和背板总线接口的关键特性。基于标准的高速串行互连和标准小型模块化设计指出了下一代计算机与通信系统设计的方向。

表1 三种总线接口特性的对比

PCIe可能是大部分CPU和端点设备的选择;sRIO有望成为用于无线基础设施上线卡DSP的指导性方案;而ASI则提供了丰富的支持高性能背板互连的特性。

责任编辑:gt

-

计算机

+关注

关注

19文章

7440浏览量

87785 -

服务器

+关注

关注

12文章

9046浏览量

85238 -

路由器

+关注

关注

22文章

3711浏览量

113609

发布评论请先 登录

相关推荐

器件高密度BGA封装设计

应用于高密度电路板的表面粘着式自复式保险丝

高速高密度PCB设计的关键技术问题是什么?

高速高密度PCB 设计中电容器的选择

高速高密度PCB的SI问题

用于高速高密度模块设计的点对点串行总线协议

用于高速高密度模块设计的点对点串行总线协议

评论