来源:内容由半导体行业观察(ID:icbank)编译自「seekingalpha」,谢谢。

在科技行业,在硬件方面最受关注的公司是英伟达、苹果、高通和AMD等芯片公司,或英特尔、三星和台积电这些芯片制造公司。虽然半导体制造设备的供应商鲜为人知,但其中还有一家颇有名气的公司,那就是来自荷兰的 ASML。

ASML 生产用于制造从逻辑到 NAND(用于 SSD、闪存等)和 DRAM 等几乎所有芯片的光刻设备。这些工具使用光在晶圆上“打印”特征、制造晶体管等。多年来,该行业一直使用 193 纳米波长的“深紫外光 (“DUV”) 光刻技术”。大约在 2000 年代中期,这项技术扩展到“浸没式光刻”:这项技术在透镜和晶片之间使用水。这将NA(breaking index)从大约 1.0 提高到大约 1.35,从而将工具的分辨率提高了类似的量。

业界预估,在 32nm 节点及以下节点(早在十多年前),光刻机光源步长将从 193nm 跃升至 13.5nm 光,后者称为极紫外或 EUV,这将大大提高分辨率,以继续摩尔定律的惊天缩放。NA 从 1.35 下降到 0.35 可以部分抵消波长的这种改善。

然而,与商用DUV 工具的约 300WPH 相比,早期的 EUV 工具的吞吐量极低,仅为每小时 10-40 个晶圆的订单(“WPH”)。这种低吞吐量意味着该工具在商业上不可行。这导致了多年的延误,因为 ASML 投资解决这些问题。

与此同时,为了继续微缩,业界发明了(昂贵且复杂的)“多重图案化”方案:这些技术多次曝光晶圆以创建一个特征,需要多个(同样昂贵的)“掩模”。(掩膜定义了“印刷”在晶圆上的特征,作为芯片的模板。)顺便说一句,这也是英特尔在 14 纳米和 10 纳米中遇到大量良率问题的原因之一。

最终,在过去几年中,这些 EUV 工具已经实现了商业化,台积电 5nm 是第一个旨在在多层上广泛使用 EUV 的节点。该节点自 2020 年开始量产。

总之,从 DUV(193nm 光)到 EUV(13.5nm 光)的过渡对延续摩尔定律起着重要作用。而ASML 是世界上唯一一家可以提供 EUV 工具的公司。

EUV设备的需求

虽然有多家 DUV 光刻工具供应商,但正如所指出的,只有一家企业拥有 EUV光刻机,那就是ASML。这意味着 ASML 作为该工具的唯一供应商发挥着至关重要的作用,其EUV设备的平均售价 (“ASP”) 远超过 1 亿美元(具体而言超过 1.4 亿美元),并使 ASML 成为股市中真正的赢家。它在过去几年推动了后者的收入和收益,EUV 现在几乎占其超过 100亿收入的一半。

ASML 宣布,其在 2020 年出货了 31 台 EUV 工具。虽然这表明 EUV 现已达到成熟,但仍低于其 35 台出货计划。(如果我没记错的话,由于从 2019 年到 2020 年初有 4 种工具已经下滑,所以计划确实是 39 次出货。)然而,未能达标的部分原因是英特尔有据可查的 7nm 延迟:这减少了 ASML四个单位的出货量。此外,实体清单也给台积电带来了问题,其前 5 大客户之一(华为)在几个季度内消失了。

正如 ASML 的首席执行官所解释的那样,这两个问题导致该公司预计需求低于预期,因此转向其供应链以减少 2021 年的产量。

ASML 首席执行官表示:这只是对去年第二季度和第三季度发生的事情的反映,你知道,我们的主要代工厂客户显然回来说,听着,我们的 N3 主要客户现在被列入黑名单。

所以,我们不能发货。因此,我们需要调整 EUV 系统的 2021 年展望,随后另一位客户表示,嗯,我们将推迟路线图,这也意味着这将推迟一年,这实际上导致了一种情况我们实际上减少了 EUV 计划系统 2021 的数量,因为客户说,这是两个原因。他们是两个大客户。

然而,从那时起发生的事情可能是众所周知的:半导体短缺。首先,台积电宣布了 2020 年 280美元的巨额资本支出指引,以应对对其领先工艺技术的需求激增。后来进一步增加了到300亿美元,并且在三年内的总体预期为1000亿美元。

虽然半导体晶圆厂肯定需要其他工具,但显然资本支出的大幅增加将成比例地使 ASML 受益。

其次,英特尔自 7 纳米延迟以来的演变也有记录。特别是,英特尔新任 CEO 特意将“全面拥抱 EUV”作为让 7nm 重回正轨的关键原因,修订后的 7nm 工艺流程包含两倍的 EUV 层数。这显然也有利于英特尔未来对 EUV 的需求。例如,虽然上面的引用谈到了四个系统,但最近 ASML 实际上只谈到了两个系统。显然,英特尔在 EUV 上的支出将在 2022 年及以后增加。

为了满足所描述的需求,ASML 此前曾表示将在 2021 年提高其生产能力,最多可生产 45-50 个 EUV 工具。然而,鉴于供应链的交货时间较长以及上一节所述的问题,ASML 无法及时对 EUV 需求的增加做出反应。因此,ASML 很可能在 2020 年仅提供约 40 个设备。

有人指出,这将导致 ASML 连续第四年或第五年无法达到其年度交付目标,但当然只是讨论了对此的提醒。

尽管如此,预计 ASP 的增加也将带来进一步的增长,路线图上有几个升级的工具,这将带来改进,例如更高的 WPH 吞吐量。ASML 预计其即将推出的工具将与其公司毛利率以及低两位数的 ASP 增长(从约 1.4 亿美元的水平)达到平价。2023 年工具实际上将在毛利率上交叉。

还有一些因素可以带来额外的增长。例如,服务收入取决于曝光的晶圆数量,直到最近,这对于 EUV 来说仍然很低。为此,ASML 表示,每个 EUV 工具基本上都会成为其 ASP 每年 5-6% 的经常性收入来源。

此外,未来将有更多晶圆(芯片中的层)使用 EUV 进行曝光,因为目前只有十几个最关键的层使用 EUV 进行曝光。(这就是英特尔“全面拥抱 EUV”的意思。)最后,DRAM 内存行业有望在未来也采用 EUV。

基于客户对先进节点不断增长的 EUV 需求,据预计,ASML今年将比去年增长约 30%,相当于 2021 年 EUV 系统收入约为 58 亿欧元。

因此,尽管 EUV 交付量低于预期,但考虑到 ASP 的增长,ASML 仍预计 2021 年 EUV 将增长 30%。此外,鉴于成熟工艺晶圆厂的半导体短缺,ASML 现在也预计其非 EUV 业务需求强劲。例如,台积电史无前例地宣布将扩充28nm 晶圆厂产能。

到 2022 年,当上述供应问题基本得到解决时,ASML 现在预计将出货 55 个 EUV 系统。尽管如此,ASML 表示,即便如此,它也可能会受到其供应链的限制,因为需求可能会超过 55 个系统的供应。

EUV 路线图,High-NA EUV是下一步

ASML 目前出货 NXE:3300C 型号,售价 1.3 亿美元,可达到 135WPH。但是,通过附加选项,ASP 增加到上面提到的约 1.45 亿美元。

ASML 将在今年推出 NXE:3300D 型号,它能够达到 160WPH,ASML 预计 ASP 将增加 10% 以上,相比之下约为 1.45 亿美元的水平。它将把 EUV 带到 ASML 的公司毛利率。

NXE:3300E 型号将在 2023 年实现到来,该型号能够达到 220WPH,这是生产力的另一项非常强劲的改进。因此,这将是 ASP增加的另一个来源 (ASML 指出,尽管 E 型号的 COGS(销售成本)较高,但毛利率仍会增加,因为它与更昂贵的 》 3 亿美元的“High NA EUV” EXE:5000 工具共享一些部件。)

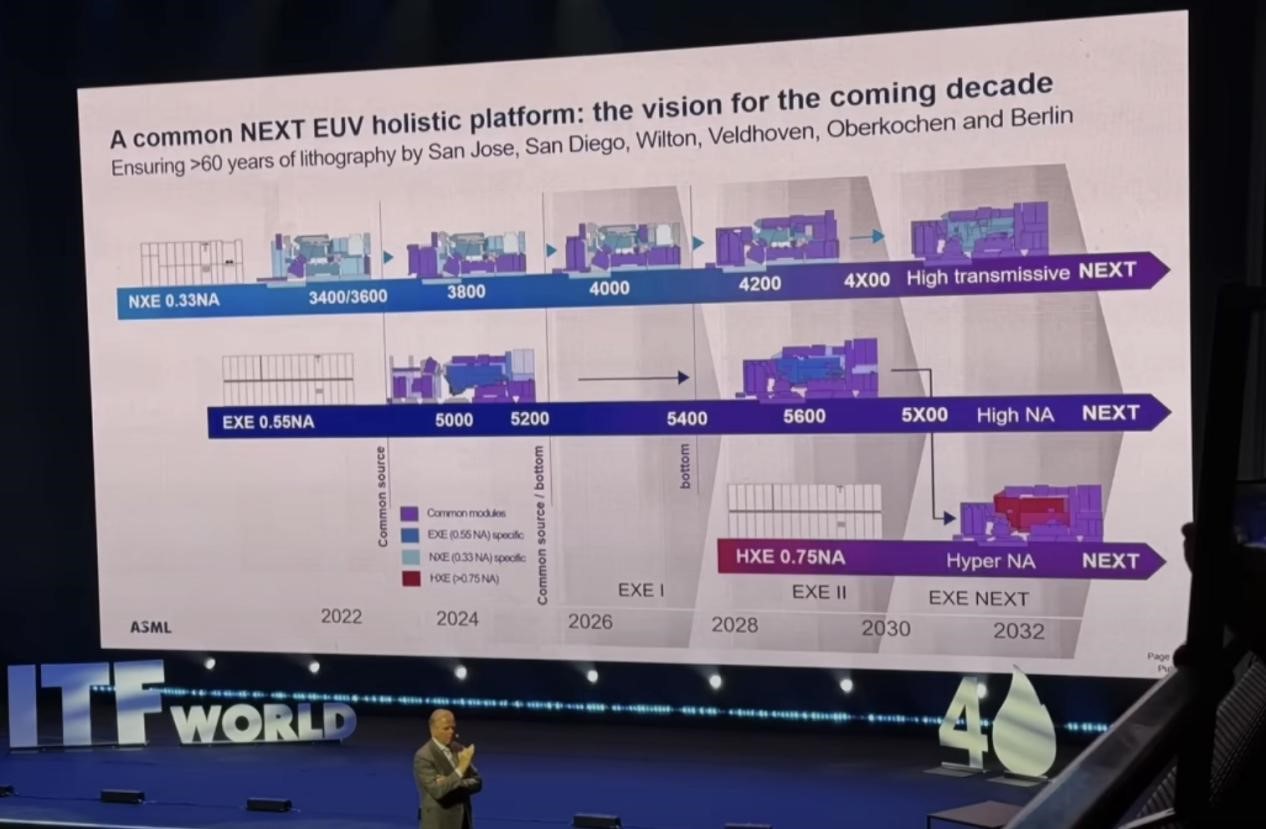

尽管如此,正如 EXE:5000 工具所表明的那样,EUV 并不是光刻缩放的最后选择。多年来,ASML 一直致力于开发 EUV 之外的下一代工具。

如上所述,虽然与之前的 DUV 工具相比,EUV 的波长显着降低,但 EUV 的NA确实从 1.35 大幅下降到 0.35。(不谈物理,破指数是光和光学领域的一种现象。)因此,几年前ASML开始研发下一代工具来解决这个问题,称为High NA EUV,参考到工具将具有的更高的 NA 数。此工具会将这个指标增加到 0.55。好处是这进一步提高了分辨率。

这将是一种更昂贵的工具,其成本超过一架飞机,预计成本超过 3 亿美元。因此,即使在最初引入 EUV 之后,ASML 的长期增长前景仍然稳固,因为在逻辑和 DRAM 中越来越多的 EUV 采用、更高的 ASP 以及下一次升级到更昂贵的High NA EUV。

然而,最近在 1 月第四季度财报发布期间,一个警告变得清晰起来。看来High NA光刻已经推迟了几年。

此前,预计High NA 将在 2023 年推出。例如,英特尔一直在呼吁开发High NA 生态系统以避免延误。

因此,开发High NA设备势在必行。“在持续改进 0.33 的同时,我们需要开发 0.55,”英特尔研究员兼芯片巨头的光刻硬件和解决方案总监Mark Phillips在最近的一次演讲中说。“英特尔拥有强大的工艺节点路线图,需要持续 EUV 光刻开发的分辨率和 EPE(边缘放置误差)优势。需要High NA EUV 以避免 0.33 NA mask splits,消除mask splits的累积 EPE,减少工艺复杂性并降低成本。我们需要生态系统准备好在 2023 年之前为其提供支持。”

在此次活动中,Phillips对光刻师和掩模制造商发表讲话,呼吁采取行动,以保持High NA EUV 走上正轨,并解决技术差距,即掩模和抗蚀剂。High-NA 一直是 2023 年的目标,但根据过去的事件,它有可能下滑。目前的 EUV 在投入生产之前已经晚了几年。

然而,ASML 宣布,它现在预计High NA 设备将在 2025 年或 2026 年(由其客户)进入商业生产,这意味着最多延迟三年。

我们正在与客户就Hihg NA 量产的路线图时间保持一致,目前估计在 2025-2026 年的时间范围内。

为满足这一时间表,我们将于今年开始集成模块,并计划在 2022 年拥有第一个合格系统。我们计划在 2023 年在客户现场首次安装第一批系统,并计划提供关于我们的 High-NA 的更详细的更新今年投资者日期间的计划。

因此,这对行业和 ASML 来说都是一次挫折。对于业界来说,这意味着要继续缩小晶体管的尺寸,他们将不得不使用那些最初为“DUV 浸没式光刻”而开发的“多重图案化”技术。虽然目前多重图案在行业中已经成熟,但它仍然是一种昂贵的技术。将此与昂贵的 EUV 工具相结合可能会给晶圆成本带来压力。

不过,对于 ASML 而言,多重 EUV 图案实际上可能会进一步增加对其当前 EUV 工具的需求。因此,这实际上可能会部分抵消High NA EUV 延迟带来的(假设)收入影响。

对于拥有多年视野的长期投资者来说,延迟应该无关紧要,就像之前很久的 EUV 延迟目前不再重要一样,因为 ASML(终于)从 EUV 获得了数十亿美元。

原文标题:EUV光刻机路线图

文章出处:【微信公众号:半导体科技评论】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

456文章

50984浏览量

425119 -

光刻机

+关注

关注

31文章

1153浏览量

47468 -

EUV

+关注

关注

8文章

607浏览量

86074

原文标题:EUV光刻机路线图

文章出处:【微信号:半导体科技评论,微信公众号:半导体科技评论】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

今日看点丨 2011亿元!比亚迪单季营收首次超过特斯拉;三星将于2025年初引进High NA EUV光刻机

ASML拟于2030年推出Hyper-NA EUV光刻机,将芯片密度限制再缩小

阿斯麦(ASML)与比利时微电子(IMEC)联合打造的High-NA EUV光刻实验室正式启用

今日看点丨ASML今年将向台积电、三星和英特尔交付High-NA EUV;理想 L9 出事故司机质疑 LCC,产品经理回应

ASML创下新的EUV芯片制造密度记录,提出Hyper-NA的激进方案

Rapidus对首代工艺中0.33NA EUV解决方案表示满意,未采用高NA EUV光刻机

台积电A16制程采用EUV光刻机,2026年下半年量产

台积电张晓强:ASML High-NA EUV成本效益是关键

ASML发货第二台High NA EUV光刻机,已成功印刷10nm线宽图案

英特尔突破技术壁垒:首台商用High NA EUV光刻机成功组装

阿斯麦(ASML)公司首台高数值孔径EUV光刻机实现突破性成果

安霸发布5nm制程的CV75S系列芯片,进一步拓宽AI SoC产品路线图

Intel和ASML宣布全球第一台High-NA光刻机“首光”

Prevayl的下一步是什么

EUV路线图,High-NA EUV是下一步

EUV路线图,High-NA EUV是下一步

评论