图:中国工程院院士、浙江大学微纳电子学院院长吴汉明

无独有偶,6月份,在台北电脑展上,AMD总裁兼首席执行官苏姿丰博士展示了全新的 3D chiplet 技术,将引领高性能计算前沿技术突破。AMD 正在与台积电合作开发的第一个使用 3D 垂直缓存的芯片,苏博士拿着一枚由 Ryzen 5900X 为原型开发的芯片,展示这项技术的初步成果。

图片来自AMD

3D堆叠技术早就用在闪存上,今天AMD把这个技术带在CPU上,突破性将AMD芯片架构以3D堆叠技术相结合,可以提高超过2D芯片200倍的互联密度,与现有的3D封装解决方案相比密度也可达到15倍以上。

图片来自AMD

这块就是采用3D堆叠技术的锐龙5900X处理器的原型设计,左边的芯片上有一块6mm*6mm的正方形SRAM与CCD结合在一起,在拥有双CCD的12核或16核锐龙处理器上就一共拥有192MB的L3缓存。在加入了3D垂直缓存后,12核的Zen 3锐龙处理器在同频下《战争机器5》的平均帧率提升了12%,整体游戏性能提升了15%。

3D Chiplet封装技术有何魔力?这个封装技术因何诞生?最新的进展是怎样的?笔者集合台积电、日月光、长电科技等芯片代工、芯片封装领域的明星企业最新观点和产品进展,和大家做深入分析。

3D IC 时代加速到来,台积电计划2022 年 3DFabric 专用晶圆厂正式启用

在近期举行的2021年技术论坛上,台积电CEO魏家哲感叹2021年全球数字化转型以惊人的速度进行,无论是办公、教育、娱乐都需要大量高速运算,疫情令全球更多人意识到半导体对全球经济的重要性。

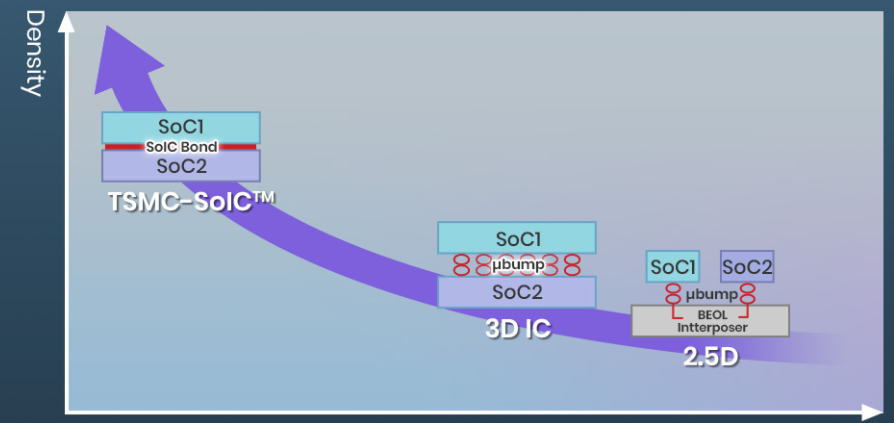

魏家哲表示,2D微缩已经不足以支持系统整合需求,由于台积电前瞻性投资和研发部门的努力,3DIC技术已经是一条可行的道路,同时满足系统效能、缩小面积以及整合不同功能的需求。

图片来自TSMC网站

在AMD发布的3D chiplet背后,是台积电的先进半导体工艺技术和先进封装技术。在今年的ISSCC中,台积电展示了SOIC技术,这次台积电为该技术商用起名(3DFabric),并且公布了互联密度相关的数据,其互联密度相比传统的基于bump的3DIC技术可以提升16倍,该数据与AMD这次在Computex发布的相关数字(相比3DIC互联密度提升15倍)也大体相符。台积电认为,高算力芯片除了在先进制程上推进外,先进的封装技术是进一步扩大密度的关键,3D封装技术是前进的最佳途径。目前,台积电3D IC技术包括Cowos、InFO、SoIC。

台积电业务开发资深副总张晓强指出,InFO_B 封装技术是 InFO 系列的新技术,基于 InFO_PoP 多年量产经验下,可以有效增加包装的芯片尺寸,而这对手机产品非常重要。特别是对于5G移动平台,TSMC具有InFO POP,用于移动应用,用于RF前端模块(FEM)应用的InFO Antenna-in-package(InFO_AiP)以及用于RF前端模块(MUST)的多堆栈(MUST)、基带调制解调器。

而InFO_oS 封装技术的特点,考虑主要针对 HPC 应用的封装技术,利用 InFO 把不同逻辑芯片整合起来,让 InFO 能力从一个 reticle 增进到 2.5 个 reticle size,能够在一个模块上整合更多更大的芯片,这对未来 HPC 应用有非常积极的作用。

此外,台积电还开发了业界第一个高密度小芯片的堆叠技术,已经开发了Chip-on-wafer、wafer-on-wafer两种不同技术,能够堆叠异构芯片和同构芯片,大幅度提升系统效能,缩小产品尺寸。

日月光推出了晶圆级 FOWLP技术

近日,在南京半导体大会上,日月光集团副总经理郭桂冠指出,随芯片复杂度日益提升,测试更耗时、耗力,使用不同封装技术进行异质芯片整合是新时代的发展趋势。

在郭桂冠看来,晶圆成本和良率是业界一直关注的焦点。“如果我们一律追求3纳米、5纳米,在良率上付出的成本极大,如果用Chiplet不需要集合成非常大的芯片,可以离散式分成几个小芯片做整合的话,良率得以大大提高。”

“我认为,除了SOC单芯片之外,2.5D甚至结合2.5D、3D高性能的计算芯片,同样SIP会带出异质系统整合的需求。9月你会看到更多的产品已经应用到扇出型就是双层结构SIP的概念。”郭桂冠表示,笔者在展台也看到日月光带来了2.5D和3D封装的成品展示。

5G对封装厂带来哪些机会?郭桂冠认为,5G不仅仅是快速传输,还有高效能技术,这部分有更快的反应速度,我们定义叫HPC。日月光针对SIP封装有两个明显的趋势:一是从单面变成双面,厚度会增加,厚度的增加远远超过实际应用。苹果厚度就是0.75,在座的手机壳厚度都远远超过,这部分随着时间演进一方面不断缩小;二是开始增加很多异形键,可以是和外面天线连接的接触片。好处是不用依赖基板,另外一个好处是线宽间距做得更优化。

日月光推出了晶圆级 FOWLP (Fan-out Wafer-Level Package) 技术,推出面板级 FOPLP (Fan-out Panel-Level Package) 的则有日月光、力成、三星等等,竞争相当激烈。

长电科技两大核心技术实现异构集成

中国半导体行业协会副理事长、长电科技董事兼首席执行长郑力表示:“后摩尔时代半导体器件成品制造技术和价值远超封测字义范畴,目前从先进封装到芯片成品制造的产业升级趋势明显,长电两大核心技术可以实现异构集成。同时,协同设计优化芯片成品集成与测试一体化趋势非常重要。”

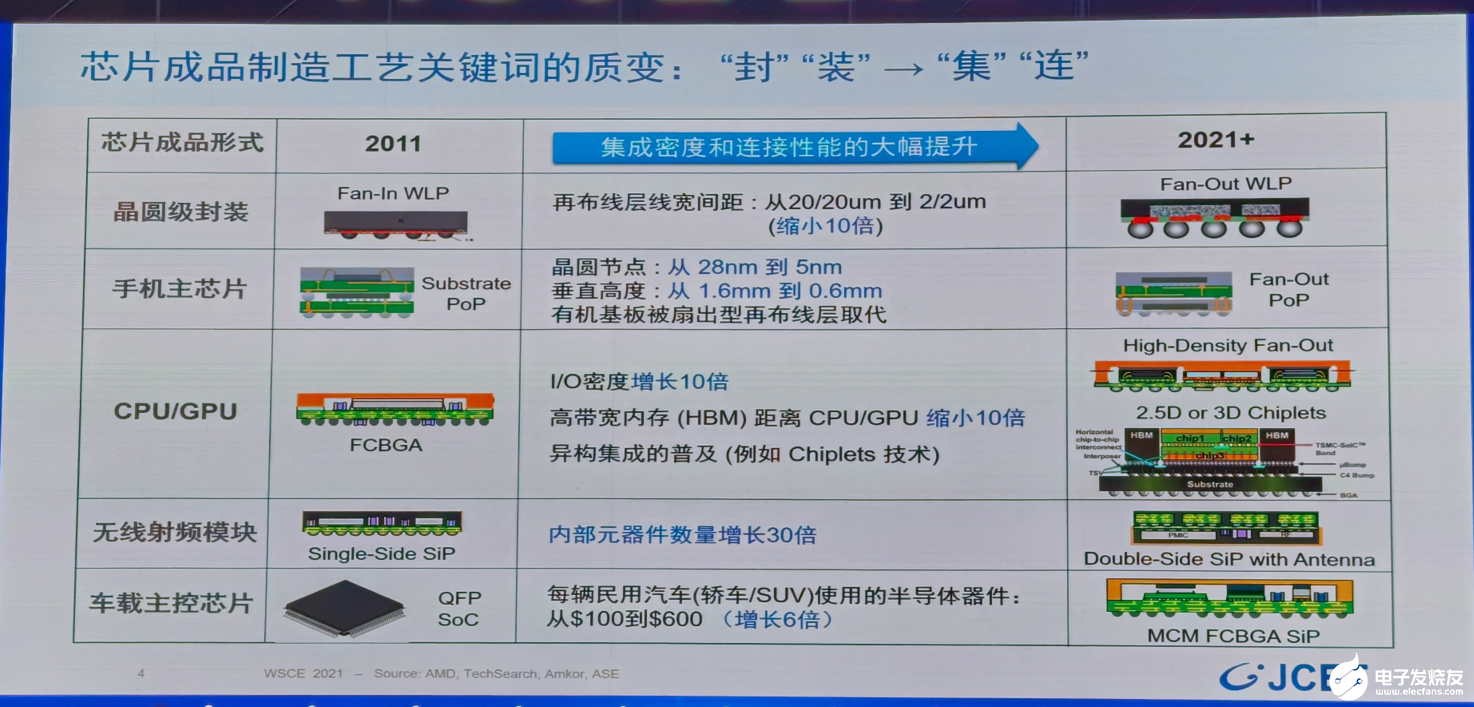

郑力分析说,目前,晶圆级封装的再布线层线宽间距已经从20/20um发展到2/2um,缩小了10倍,几乎与手机主芯片制程演进是同样的速度,从2011年的28nm进入到今天的5nm;手机主芯片的晶圆节点也从28nm发展到5nm,从有机基板变为扇出型再布线层,垂直高度从1.6nm到0.6nm;CPU、GPU的I/O密度增长10倍,集成高带宽的存储器,还有异构集成技术加入;无线射频模块内布元器件数量增长30倍。用一句话概括,先进封装在技术向前发展到异构集成,微系统集成阶段时实现了质的飞跃。

上周AMD在台北电脑展展示的2.5DChiplet、3D Chiplet等异构集成,密度提高300倍,台积电、Intel,国际半导体的头部企业都在积极布局半导体的异构集成应用。

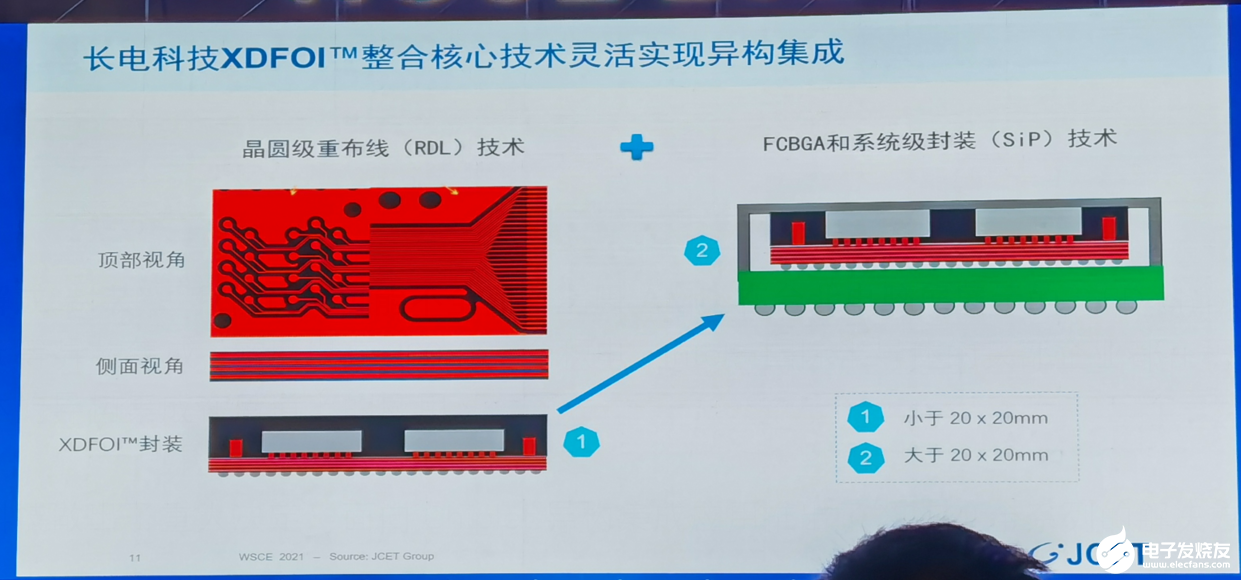

先进芯片成品制造技术正在发生颠覆性突破,长电科技也在异构集成技术赛道上不断换挡提速。针对Chiplet异构集成应用,长电科技推出了XDFO全系列的解决方案,包括2D Chiplet、2.5D Chiplet和3D Chiplet,可适用于移动通信、汽车、医疗和人工智能等应用。

基于设计需求,长电科技的无硅通孔扇出型晶圆级高密度封装技术,可在硅中介层(Si Interposer)中使用堆叠通孔技术(Stacked VIA)替代硅通孔技术(TSV)。该技术可以实现多层RDL再布线层,2×2um的线宽间距,40um极窄凸块互联,多层芯片叠加,集成高带宽存储和集成无源元件。

长电科技在扇出型技术积累接近10年,在结合高密度SIP技术,面向未来推出2.5D chiplet、3D chiplet等产品解决方案,可灵活实现异构集成。郑力透露,这些产品在2022年、2023年都有面向量产的项目和解决方案。

郑力强调说:“除了在技术和工艺上不断突破,要实现低成本、高性能、环保优质的集成电路产品制造,还需要通过系统级电性能、结构、热仿真模拟与系统设计,这就使得芯片成品集成测试一体化成为一种潮流。长电科技要和IP、设计企业、EDA企业合作,芯片主体的协同设计要做起来。”

小结

中国科学院院士毛军发院士指出,异质集成电路特色突出:一是可以融合不同半导体材料、工艺、结构和元器件或芯片的优点;二是采用系统设计理念;三是应用先进技术比如IP和小芯片Chiplet;具有2.5D或3D高密度结构。异质集成电路优点明显:首先,实现强大的复杂功能、优异的综合性能,突破单一半导体工艺的性能极限;二是灵活性大、可靠性高、研发周期短;三是三维集成可以实现小型化、轻质化;对半导体设备要求相对比较低,不受EUV光刻机限制。

台积电、日月光、长电科技的最新实践和技术演进,相信能给未来5G高性能计算、AI和IoT芯片的落地带来更多助力,也是中国芯片弯道超车的可能路径之一。

本文由电子发烧友原创,作者章鹰,微信号zy1052625525,转载请注明以上来源。如需入群交流,请添加微信elecfans999,投稿发邮件到huangjingjing@elecfans.com.

-

amd

+关注

关注

25文章

5468浏览量

134173 -

台积电

+关注

关注

44文章

5637浏览量

166523 -

长电科技

+关注

关注

5文章

352浏览量

32505

发布评论请先 登录

相关推荐

后摩尔时代,先进封装如何实现华丽转身?台积电领衔的三大企业放大招

后摩尔时代,先进封装如何实现华丽转身?台积电领衔的三大企业放大招

评论