传统的工业数据采集设计通常需要对模数转换器 (ADC) 之前的模拟前端 (AFE) 进行复杂的滤波处理。模拟滤波器的主要目的是衰减不需要的带外信号,进而防止这类信号在所需的目标信号上发生混叠,因此,模拟滤波器又称为抗混叠滤波器 (AAF)。混叠频段中不需要的信号和噪声可能源自驱动放大器、电源切换引入的杂散,甚至是意外的干扰因素(干扰器)。

混叠频率大小直接取决于 ADC 采样速率,数据转换器在给定瞬时带宽下的工作速度越快,混叠频段距离所需的信号就越远,越容易进行滤波处理。根据这一现象,在精度非常高的系统中,设计人员通常使用具有高过采样率和抽取滤波器的 Σ-Δ ADC。

在手机基站中,将 3GPP 的射频直采频段从 1GHz 增至 6GHz,提高了每秒千兆取样率 (GSPS) 数据转换器的使用率。由于 3GPP 频段的瞬时带宽只是此采样率的一小部分,因此,使用过采样 GSPS 转换器的全新架构也放松了对模拟射频滤波器的要求。

使用逐次逼近寄存器 (SAR) ADC 的各种工业应用(例如,电能质量分析、声纳或采样率在 1MSPS 到超过 10MSPS 之间的工业雷达)也可以使用精密 Δ-Σ 和 GSPS ADC。高速 SAR ADC 的全新 ADC35xx 和 ADC36xx 系列具有一个集成式数字滤波器,因此工业应用可利用这一过采样和抽取设计技术来降低对外部模拟滤波器的要求。

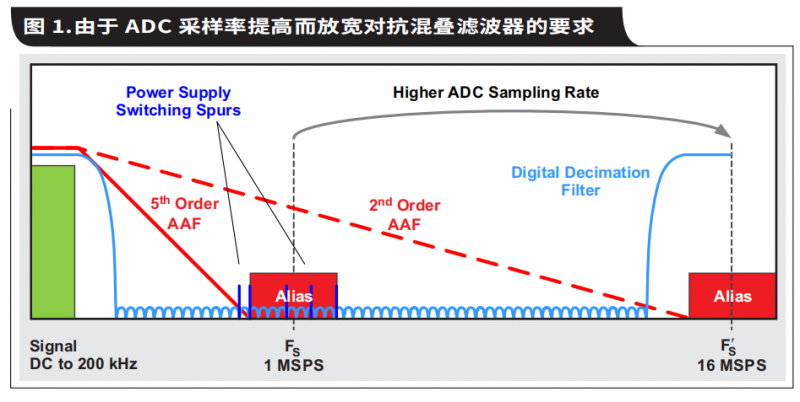

对于图 1 所示的示例,假设直流输入信号为 200kHz,ADC 采样率为 1MSPS。实现约 300kHz 的通带和 40dB 左右的混叠抑制大概需要一个五阶滤波器。如将 ADC 采样率从 1MSPS 增至 16MSPS,混叠频段就会从 800kHz 推远至 15.8MHz,所以将抗混叠滤波器替换为二阶滤波器。此外,混叠频段还会偏离此频区(600kHz 至 2MHz),此频区中通常包含由电源的开关稳压器产生的杂散。

内部数字滤波器

下面主要介绍了内部数字滤波器的三种作用。

1.衰减混叠频段信号

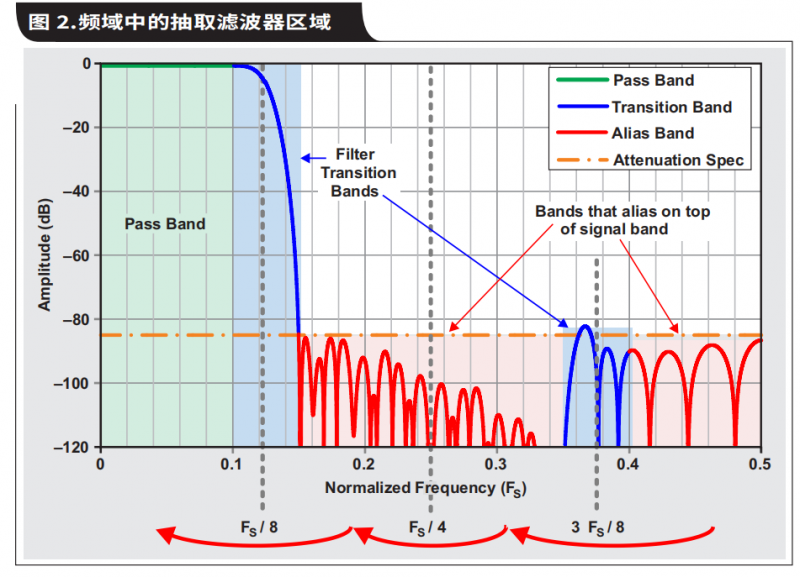

在频域中常用的数字抽取滤波器是数字低通滤波器。该滤波器包括三个不同的频域:通带、多过渡带和混叠带,如图 2 所示。在本图中,混叠带中的任何信号都会在通带上发生混叠,但会衰减 85dB 左右或以上。所有三个混叠带都围绕 FS/8、FS/4 和 3 FS/8进行镜像。

2.降低输出数据速率

下游处理器可能很难处理较高的过采样率。而且,在过采样配置中,大部分频谱都只包含不需要的分量,传输这些分量会造成不必要的能量消耗。数字滤波器会丢弃样本并降低输出数据速率。

目标频段不在低频率范围内时,数字混频器会对信号进行降频转换,然后再进行低通滤波,从而更大程度地降低输出速率。

3.提高 SNR

数据转换器的信噪比 (SNR) 是通过对 ADC 整个奈奎斯特区域的底噪进行积分运算来计算的。理论上,每个数字抽取因子 2 都会使 ADC SNR 增加 3dB。实际上,在带内噪声成为主要噪声前,ADC SNR 的增加幅度很接近 3dB。

在之前的示例中,ADC 采样率从 1MSPS 增至 16MSPS。增加抽取因子为 16 的数字滤波器会将输出速率降至 1MSPS,而将 ADC SNR 提高多达 12dB (4 × 3dB)。

噪声频谱密度 (NSD) 是数据转换器噪声性能的另一个量度。它将 SNR 和带宽考虑在内,通常用于比较不同的数据转换器。例如,SNR 为 82dB 的 16MSPS ADC 的 NSD 为 –151dBFS/Hz [82dB + 10 × LOG (8MHz)]。在抽取因子达到 16 后,SNR 会增加 12dB(从 82dB 增至 94dB),而 NSD 会保持在 –151dBFS/Hz [94dB + 10 × LOG (0.5MHz)]。

了解抽取滤波器

以下多项权衡因素决定了数字滤波器的架构和滤波器抽头的数量:可编程系数和固定系数、最大带通纹波、最小阻带衰减、延迟和功耗。例如,滤波器滚降越快,阻带衰减越多,就会需要更多的滤波器抽头,从而导致较高的功耗和较长的延迟。滤波器系数决定滤波器提供低通、高通,还是带通频率响应。

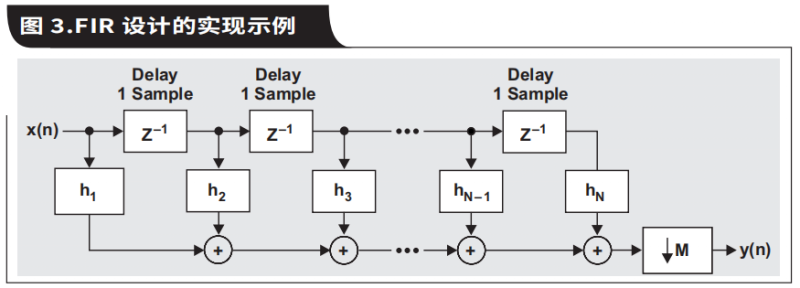

将数字滤波器与高速数据转换器集成时,ADC 设计人员通常使用有限冲激响应 (FIR) 半带低通滤波器,因为这种滤波器的设计本质上非常节能。半带意味着抽取因子为 2,其他每个系数均为 0,并且这些系数无需任何计算。非零系数关于脉冲响应中心对称。

图 3 显示了常规 FIR 的实现方案。在具有 7 个抽头/系数 (N = 7) 的半带实现中,除了 h4 之外的所有偶数抽头(h2、h6)都为 0,从而将 7 个乘法减少至 5 个。如果抽取因子较高,会连接半带滤波器。理论上,低通、高通或带通滤波器可以与 ADC 相集成,但是,低通滤波器是更实用的选择,尤其是在添加复频混频器以构建数字调谐器时更是如此。

请注意,数字滤波器位于模数转换之后。因此,数字滤波器无法防止接收器的干扰导致 ADC 达到饱和状态。但是,仍有必要使用外部滤波和可调节的增益来防止 ADC 过载。

复频抽取 - 数字调谐器

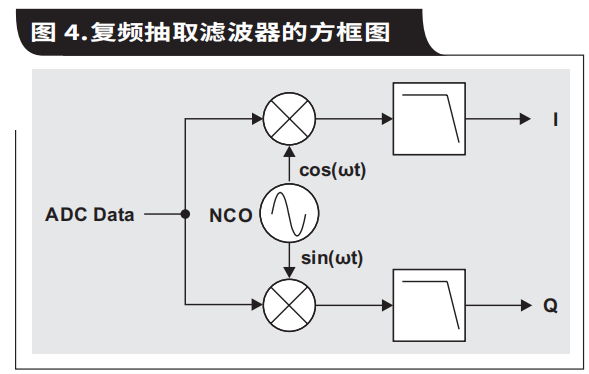

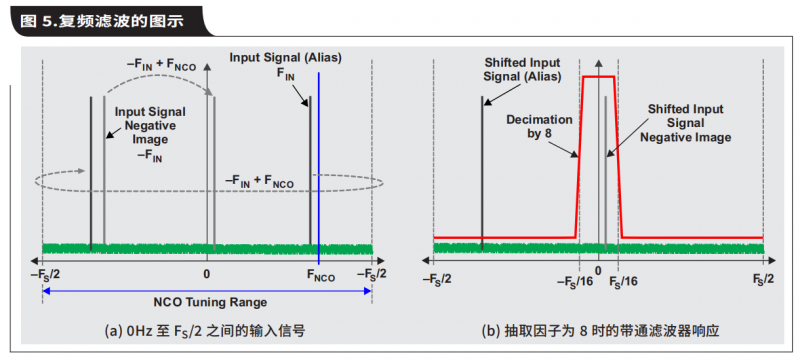

添加复频混频器 [对 I/Q 输出使用 cos(ωt) 和 sin(ωt)] 可将两个数字低通滤波器转换为可调节的数字带通滤波器,如图 4 所示。该混频器将数控振荡器 (NCO) 用作本振 (LO)。“I”路径和“Q”路径都相当于此频域中的低通滤波器。正弦、余弦之间的相位差消除了正/负频率。数字混频器会将正或负奈奎斯特区域中的任何频率转换为 0Hz,从而实现功能强大的可调带通滤波器,同时还替代了传统的模拟混频器。

0Hz 和 +FS/2 之间的输入信号 (FIN)。该输入信号 (–FIN) 的负频率介于 0Hz 和 –FS/2 之间。输入信号及其负频率都与 NCO 频率(在此示例中为 +FNCO)混合。在 –FIN 旋转至正奈奎斯特区域时,+FIN 旋转至负奈奎斯特区域。此示例显示了在 0Hz 下、抽取因子为 8 时带通滤波器的响应,会传递与 NCO 频率 (FOUT = –FIN + FNCO) 混频的 –FIN 频率。

实际示例

在时域应用中,数字低通滤波器可以去除输入信号上的高频噪声。对脉冲形状的波形进行采样时,低通滤波器将移除较高阶的谐波,从而降低脉冲的边沿速率。

综上所述,在雷达等频域应用中,集成式抽取滤波器可提供强大的功能。图 6 进一步说明了分别在 FS = 65MSPS 下、使用复频抽取因子 8 和 NCO 频率 5.5MHz 对输入信号 FIN 进行采样的结果。

结束语

为了减小印刷电路板的尺寸并降低物料清单成本,设计人员希望使用数字逻辑/知识产权 (IP) 替换模拟电路。具有集成式数字滤波功能的高速 SAR 数据转换器(如 ADC35xx 和 ADC36xx 系列)非常适合各种各样的工业应用。与 Δ-Σ 转换器相似,得益于较高的过采样率和集成式数字滤波功能,这些 ADC 也放宽了对模拟滤波器的限制。复频混频器还可以去除模拟混频级,从而进一步简化了模拟前端信号链。

编辑:jq

-

滤波器

+关注

关注

162文章

8491浏览量

186570 -

寄存器

+关注

关注

31文章

5622浏览量

130589 -

adc

+关注

关注

100文章

7973浏览量

557325 -

GSPS

+关注

关注

0文章

58浏览量

17791

原文标题:如何通过具有内部数字滤波器的高速 ADC 简化 AFE 滤波

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

输入引脚上数字滤波器的用例介绍

屏蔽电源滤波器的分类

AD7341/AD7371:高速语音带调制解调器的理想滤波器解决方案

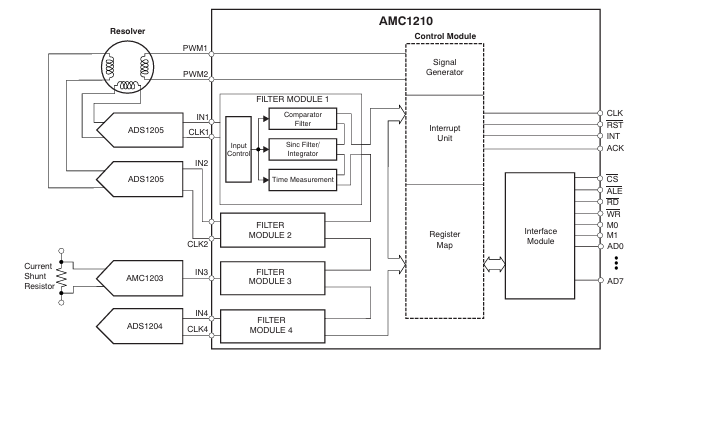

深入剖析AMC1210:多功能数字滤波器的卓越应用

深入解析AMC1210:适用于电机控制的多功能数字滤波器

应用于ECG和BioZ AFE电路的EMI滤波器分析与设计准则

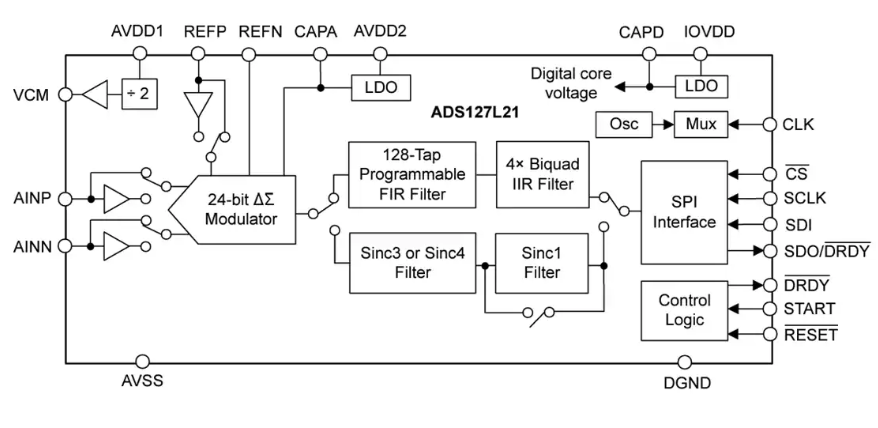

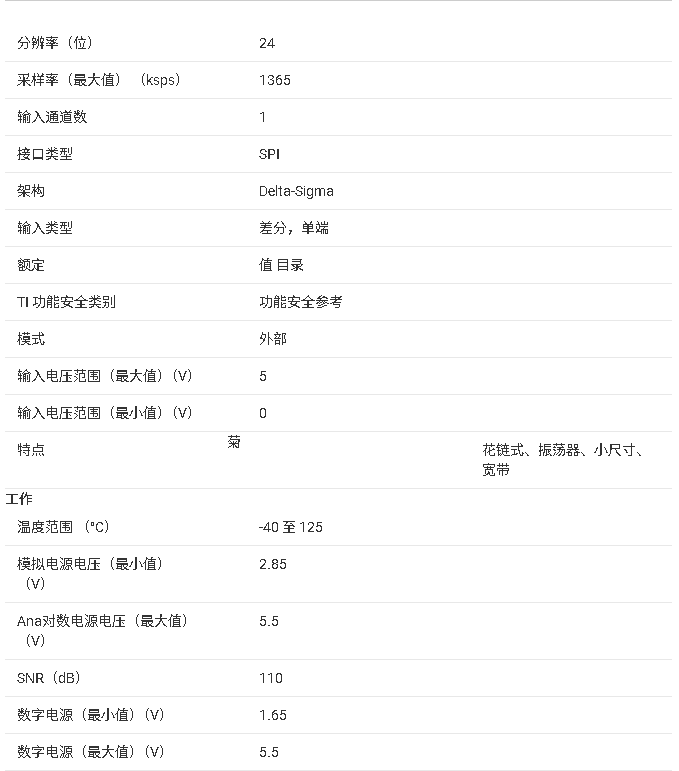

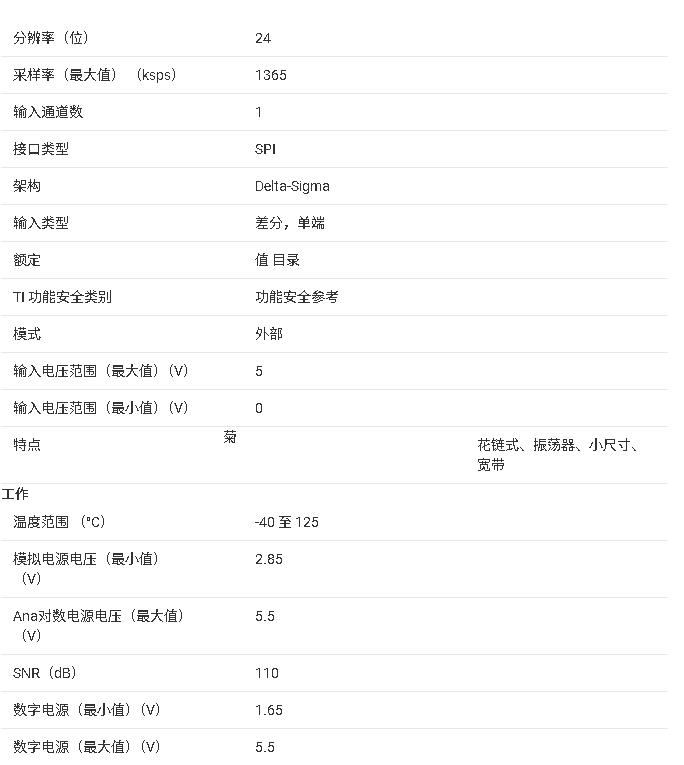

德州仪器ADS127L21高精度24位ΔΣ模数转换器技术解析

Texas Instruments ADS127L21B宽频Δ-ΣADC数据手册

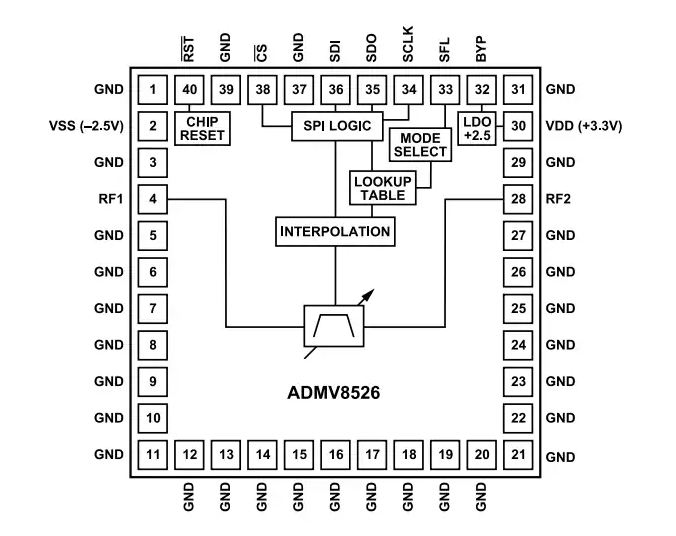

Analog Devices Inc. ADMV8526数字可调谐滤波器数据手册

怎么用具有内部数字滤波器的高速ADC简化AFE滤波呢

怎么用具有内部数字滤波器的高速ADC简化AFE滤波呢

评论