1 引言

随着internet技术的发展,在许多领域都引起了飞跃性的变化。嵌入式系统应用领域中一个新的趋势就是开始在嵌入式设备上集成网络通信功能,比如网络监控、网络数据采集系统等,以便于通过网络与远程设备进行信息的交互和增强系统的互连性,仅仅需要一根网线就可以轻轻松松完成系统的互连。

目前市场上的嵌入式处理器的种类很多。altera公司推出了第二代片上可编程嵌入式软核处理器nios ii,再配上其低成本、高性价比的fpga器件,使得嵌入式系统的开发变得越发方便。再者由于nios ii可配置和fpga器件可编程的特点,与专用硬件相比灵活性得有很大的优势,从而使得fpga器件在现代电子设计中得到广泛的应用。

2 系统设计

2.1 nios ii简介

nios ii嵌入式软核处理器是altera公司推出的第二代片上可编程的软核处理器,nios ii是可配置的,用户可以根据自己的实际需要进行处理器的配置,以达到资源的合理使用,其性能可以超过200dmips。nios ii采用哈佛结构,具有32位指令集,32位数据通道和可配置的指令及数据缓冲,而且支持用户自定义指令(最多256个)以扩展cpu指令集,提升系统的性能,为可编程片上系统(sopc)设计提供了一套完整的解决方案。nios ii提供了三种内核:nios ii/f是一种高性能的内核,速度最快但消耗的资源最多;nios ii/e是低成本内核,速度最慢消耗的资源最少;nios ii/s是一种性能和成本折中的内核。本设计采用的是nios ii/s内核。

nios ii的优势就在于其灵活性,可以根据用户的需求进行灵活的配置和裁剪。基于nios ii软核的系统设计利用altera公司提供的系统设计工具sopc builder和集成开发环境niosii ide可以进行软硬件协同设计,很大程度上缩短开发周期,在系统开发的任何阶段要都可以很方便的对系统进行修改。fpga器件丰富的逻辑资源,结合nios ii强大的处理能力,将为嵌入式系统设计提供有效的解决方案。

2.2 系统设计

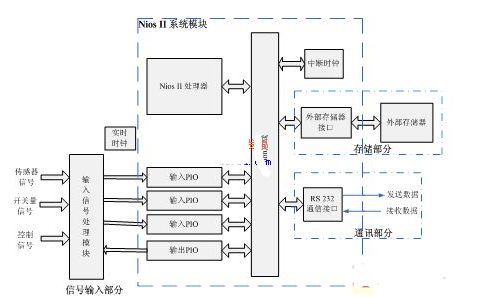

图 1 系统模块图

系统模块图如图1所示。设计采用了altera公司的cyclone ii系列芯片。在其中配置niosii软核处理器控制外围设备和协议栈的运行。而且添加了一个计算校验和的用户指令(cal_checksum)。

片上ram用作内存运行程序;flash使用了sharp公司的lh28f160s3t-l13a,用来存储程序和配置信息,系统上电后,先将程序从flash中拷贝到片上ram运行;网络接口芯片使用smsc公司的10/100m以太网接口控制芯片lan9c111,所以在sopc builder中配置系统时,需要加上altera免费提供的lan9c111接口控制器,嵌入式设备通过lan9c111就可以接入以太网,与网络上的其他设备进行网络通信;sdram选用micron公司的mt48lc8m16a2,用来缓存网络数据,其中sdram控制器使用altera免费提供的sdram控制器。

要提高系统的性能,一方面是提高处理器的处理能力;另一方面就是将用软件处理比较费时间的模块使用硬件模块来实现。经过分析发现,在网络协议栈的运行过程中,最耗费时间的是校验和的计算,尤其是当数据量非常大的时候。为此,专门用硬件定制了一个用户指令校验和计算指令(cal_checksum),对数据校验和的计算实现硬件加速,作为一个指令添加到niosii系统中,在协议栈程序中调用来缩短计算校验和的时间,提高处理速度,达到提升系统性能的目的。

2.3 校验和计算指令(cal_chkusm)

在上面的分析中已经提到过,在整个协议栈的处理中,最耗时间的就是数据校验和的计算,特别是当数据长度很大时。所以在设计中将数据校验和的计算采用硬件模块来实现,作为niosii的一个用户自定义指令,以提高校验和计算的速度。在协议栈的移植过程中,将数据的宽度修改为16位,方便最后将16位校验和的计算结果添加到相应的域。

校验和的计算需要很多个时钟周期才能完成,所以校验和计算指令使用了multi-cycle用户指令结构。multi-cycle用户指令的端口操作有:固定长度和可变长度。因为网络传输的数据长度是不断变化的,所以校验和计算指令选择可变长度操作,这也影响到端口信号的选择。

multi-cycle用户指令结构的信号有:reset,clk,clk_en,start,dataa[31:0],datab[31:0],done,result[31:0]。其中除了reset,clk,clk_en三个信号外,其他信号都是可选的,要根据具体的应用选择。本设计中校验和计算指令用到了start,dataa[31:0],done,result[31:0]。start信号作为数据有效信号,dataa[31:0]为数据输入信号,当校验和计算完成时done信号有效,通知cpu读取result端口上的数据,因此计算校验和指令逻辑必须确保当done信号有效时,result端口上的数据有效。

在sopc builder中添加校验和计算指令,然后重新产生系统,再在quartusii中更新并编译,在ide的重新编译一次工程,系统库中的“system.h”文件包含校验和计算指令的宏定义如下:

#define alt_ci_cal_chksum_n 0x00000000

#define alt_ci_cal_chksum(a) __builtin_custom_ini(alt_ci_cal_chksum_n,(a))

用户只需要在源文件中将计算校验和部分使用上面的宏做相应的替换就可以,对用户来说这再简单不过了,就像是调用一个子函数。由此可见,基于niosii软核处理器开发的嵌入式系统,具有一般嵌入式处理器不能比拟的优势。

3 软件设计

协议栈使用了现在在嵌入式应用领域已经很成熟的uip。如果使用altera提供的lwip协议栈,那么就得考虑其在嵌入式操作系统上的移植,这样无疑会增加系统软件设计的复杂度和代码量。

设计的关键部分是uip协议栈在nios ii上的移植。针对niosii的特点,将uip做适当的修改,使niosii处理器的处理能力得到充分发挥,提高系统的性能。uip原来是针对8位处理器的,现在将其修改为16位,这样理论上处理能力就提高了一倍,系统的性能也就提升了一倍。

根据tcp/ip模型结构,数据链路层和物理层使用网络接口芯片lan9c111完成;网络层和传输层协议解析在niosii中由嵌入式tcp/ip协议栈实现;应用层由用户根据需要编写。各个模块合起来共同完成网络通信功能。

3.1 底层驱动程序的编写

lan9c111芯片的底层驱动是由altera免费提供的,可以调用这些底层驱动来完成初始化、通信建立、监听等通信功能。这些底层驱动函数是已经封装好的,用户不需要了解其细节就可以编写网络通信程序,但是为了进行高级的开发,必须对整个程序的工作机制有一定的了解。

几个主要的底层驱动函数来完成启动、复位和初始化phy、以太网packet的收发及中断处理函数等工作:

static void r_lan91c111_enable():用于启动芯片工作,使能发送和接收。

int nr_lan91c111_reset():对芯片尽心复位。

static int r_lan91c111_init_phy( ):完成物理层芯片的初始化。

int nr_lan91c111_set_irq():设置芯片的中断

上层的通信程序调用这些函数实现网络接口的控制,通信功能的实现以此为基础。

3.2 通信软件的实现

通信软件完成设备之间通信的主要功能,主要是uip协议栈的。传输层实现了tcp和udp,这在软件设计时就需要做不同的考虑,不同的数据传输需求要求使用不同的传输层协议,比如,实时性要求高的传输应用就要求使用无连接的udp协议;对实时性要求不高并且要保证数据传输的可靠性的应用使用面向连接的、可靠的tcp协议可以保证传输的可靠性。

程序框架如下:

main()

{

netif_init(); // 网络接口初始化

uip_init(); // 协议栈初始化

arp_table_init(); // arp 表初始化

netconn_new() // 建立新的连接

netconn_bind() // 绑定端口号

netconn_listen() // 侦听端口

while(1)

{

if (收到数据){

…… // 处理接收的数据

}

else if(发送数据){

…… // 发送数据

}

else

…… // 返回准备下次处理

}

}

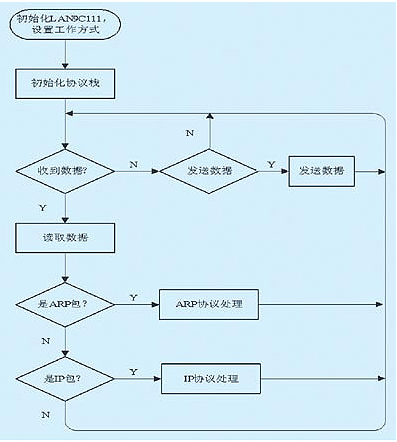

图2是软件处理流程。

图2 通信软件流程图

4 结束语

采用niosii进行系统设计,由于sopc builder工具的强大系统开发功能再加上niosii ide集成开发环境,使得系统的设计变得简单方便、可扩展性强,并且系统软件的设计与系统设计同时进行,大大缩短开发周期。在该网络平台的设计中,使用了嵌入式领域非常成熟的uip,并且是开放源代码的,所以对uip的移植非常的方便,只是对其进行修改以最大限度的发挥niosii处理器的特点,再加上简单灵活的用户自定义指令,对系统性能的提升起到很大作用。这个系统已经在硬件上经过了验证,可以进行可靠、稳定的网络通信,并已经应用于一个要求远程网络通信功能的数据处理机系统。

责任编辑:gt

-

处理器

+关注

关注

68文章

19404浏览量

231070 -

嵌入式

+关注

关注

5092文章

19176浏览量

307454 -

数据采集

+关注

关注

39文章

6245浏览量

113997

发布评论请先 登录

相关推荐

Cyclone II FPGA和Nios II嵌入式处理器的优势

嵌入式软核Nios Ⅱ串口直接读写寄存器有哪些编程方法?

怎么设计集软核处理器的嵌入式设计平台?

Nios II入门起步-创建一个嵌入式处理器系统

Nios II嵌入式设计包详解

基于Nios II的嵌入式开发模式的搭建方案

基于nios ii嵌入式软核处理器的嵌入式系统设计解决方案

基于nios ii嵌入式软核处理器的嵌入式系统设计解决方案

评论