本文将回顾基本ECL反相器/缓冲器的操作,然后我们将研究该逻辑系列的一些最重要的特性。

发射极耦合逻辑(ECL)是基于BJT的逻辑系列,通常被认为是可用的最快逻辑。ECL通过采用相对较小的电压摆幅并防止晶体管进入饱和区来实现其高速运行。在1960年代后期,当标准TTL系列提供20ns栅极延迟而CMOS4000系列具有100ns或更多延迟时,ECL提供了令人难以置信的仅1ns延迟!

本文将回顾基本ECL反相器/缓冲器的操作,然后我们将研究该逻辑系列的一些最重要的特性。

发射极耦合逻辑

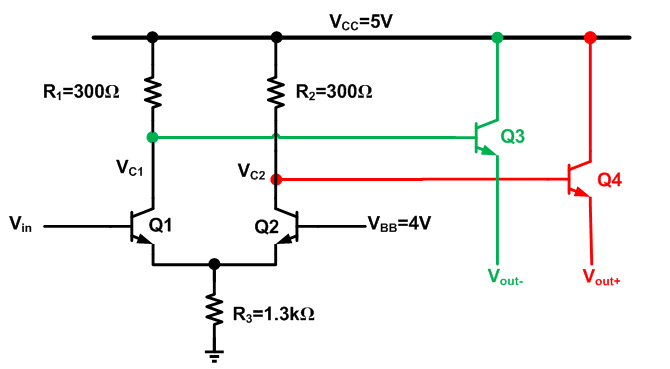

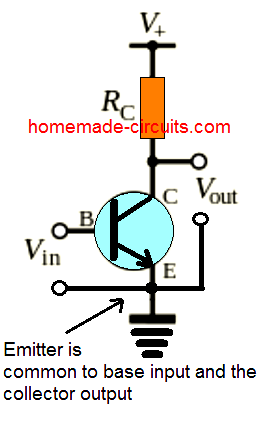

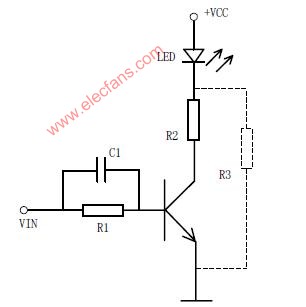

发射极耦合逻辑是一个高速双极逻辑系列。为了熟悉这个逻辑,让我们检查一个ECL反相器/缓冲器,如图1所示。在这个图中,伏一世nVin是门的输入,伏○你吨-Vout−是颠倒的版本伏一世nVin和伏○你吨+Vout+是的补充伏○你吨-Vout−。在这个特定的例子中,伏○你吨+Vout+可以被认为是输入的缓冲版本。而且,伏乙乙VBB是合适的电压(图1中的4V)。让我们将逻辑高电平和逻辑低电平分别定义为4.4V和3.6V,并检查图1中电路的操作。

图1.ECL反相器/缓冲器

假使,假设伏一世nVin为逻辑高(4.4V),因此Q1的发射极将约为4.4-0.6=3.8V。因此,Q2的基极-发射极电压将为0.2V。此基极-发射极电压不足以导通Q2。因此,电阻器R2会将Q2的集电极上拉至Vcc=5V。

计算集电极电压伏C1Vc1,我们应该注意到流过R3的电流,即3.8伏1.3克Ω=2.92米一种3.8V1.3kΩ=2.92mA,将通过Q1。因此,我们得到伏C1=5伏-300Ω×2.92米一种=4.12伏Vc1=5V−300Ω×2.92mA=4.12V(为了简化计算,我们假设集电极电流等于发射极电流)。射极跟随器Q3和Q4将充当缓冲器,将Q1和Q2的(直流电平偏移)集电极电压传递到ECL门的最终输出,伏○你吨-Vout−和伏○你吨+Vout+.假设Q3和Q4的基极-发射极电压为0.6V,我们得到伏○你吨+Vout+=4.4V和伏○你吨-Vout−=3.52V。如您所见,对输入应用逻辑高会在伏○你吨+Vout+和非常接近定义的逻辑低(3.6V)的电压电平伏○你吨-Vout−。因此,图1的电路用作反相器/缓冲器。

如果我们将逻辑低电压(3.6V)施加到栅极的输入端,Q2将开启,而Q1将关闭。这将导致逻辑高伏○你吨-Vout−和非常接近逻辑低(3.61V)的电压电平伏○你吨+Vout+.

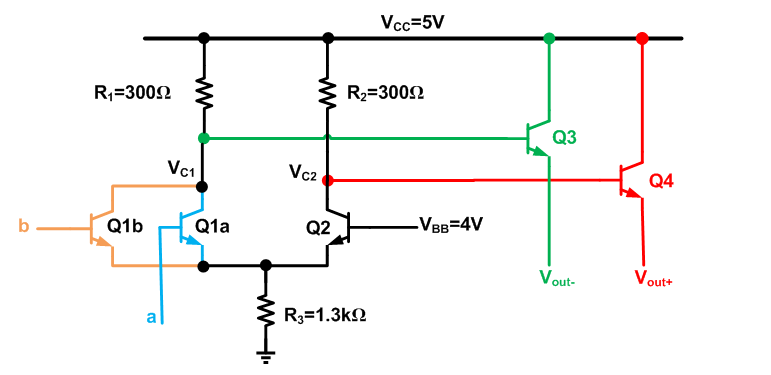

现在您已经熟悉了ECL反相器/缓冲器,您应该能够验证图2的电路是否实现了a和b的OR函数或a和b的NOR函数,具体取决于正负输出如何被使用。

图2

低电压摆幅

如您所见,ECL门的逻辑高电平和低电平之间的电压差远小于CMOS或TTL逻辑门的电压差。这种低电压差减少了从逻辑高电平转换到逻辑低电平所需的时间,反之亦然。因此,ECL逻辑提供了更高频率的操作。

避免饱和

除了逻辑电平之间的低电压差之外,还有另一种机制对ECL门的高速运行有显着贡献。诀窍是防止双极晶体管进入饱和区。关闭饱和双极晶体管需要去除或重新组合晶体管基区中产生的一些载流子。

如果我们对饱和BJT的输入应用从高到低的转换,晶体管输出不会改变,直到基极中的电荷被移除。这为用作开关的BJT的操作引入了额外的延迟,称为存储时间。存储时间过后,晶体管脱离饱和,晶体管的输出开始响应输入。

如果选择了合适的电阻值,ECL逻辑可防止晶体管进入饱和状态。例如,在图1中,R1、R2和R3的选择使得Q1和Q2的集电极电压不能低于约4.1V。根据上述讨论,Q1和Q2的最大发射极电压约为3.8V。因此,这两个晶体管的集电极-发射极电压总是大于伏C(米一世n)-伏乙(米一种X)VC(min)−VE(max)=4.1V-3.8V=0.3V。这比大约0.2V的集电极-发射极饱和电压大。因此,Q1和Q2不能进入饱和区。

如上所述,ECL通过正确选择电阻值避免了存储时间问题。由于存储时间在其他逻辑系列中占传播延迟的很大一部分,因此有几种其他方法可以减少这种不希望的影响。

正参考ECL

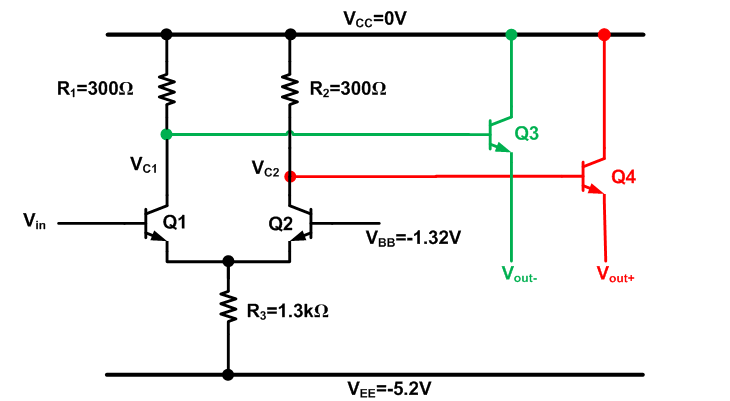

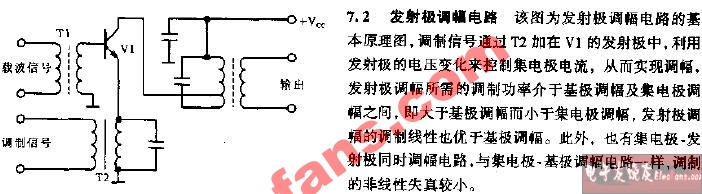

值得一提的是,旧的ECL系列使用负电源电压,如图3所示。这就是为什么使用正电源电压的图1等ECL门被称为正参考ECL或PECL(发音为“peckle”)。

图3

抗噪性是早期ECL门使用负电源的主要原因。正如对ECL反相器/缓冲器的分析所示,ECL门的输出电压取决于伏CCVCC.例如,逻辑高等于伏CC-伏乙乙VCC−VBE,在哪里伏乙乙VBE是射极跟随器的基极-发射极压降。逻辑低是伏CC-伏乙乙-伏G一种吨电子VCC−VBE−Vgate,在哪里伏G一种吨电子Vgate是逻辑高电平和逻辑低电平之间的电压差,由电阻值决定。因此,任何噪音伏CCVCC将直接影响ECL门的输出电压。

与稳定的低噪声电源电压相比,实现稳定的低噪声接地节点通常更容易。早期的ECL系列使用负电源,接地用作栅极输出电压的参考;这导致更好的抗噪性。然而,PECL之所以流行,是因为它更容易与其他逻辑系列(如TTL)接口。

如果使用负电源,则需要在设计的整个基于ECL的部分中分布干净的接地。使用正参考ECL时,应将相同的考虑应用于电源分配。例如,如果系统中同时使用TTL和ECL,建议为两个逻辑系列使用单独的电源平面,以便TTL开关瞬变不会影响ECL操作。

功耗

在图1中,我们看到改变输入的逻辑状态会使电流流过Q1或Q2。然而,应该注意的是,流经Q1和Q2的总电流对于逻辑高输入和逻辑低输入几乎相同。因此,ECL电路第一级的功耗几乎是恒定的。

在电压转换期间,CMOS逻辑门会引起电源电压的瞬态干扰。ECL的一个主要优点是输入级(即Q1和Q2)的电流控制行为不会像CMOS开关那样引起干扰。

然而,这种噪声性能是以消耗更多静态功率为代价的。请注意,CMOS栅极仅在电压转换期间消耗功率,而由Q1和Q2形成的差分对(见图1)几乎总是消耗大约4伏1.3克Ω≈3米一种4V1.3kΩ≈3mA从伏CCVCC.

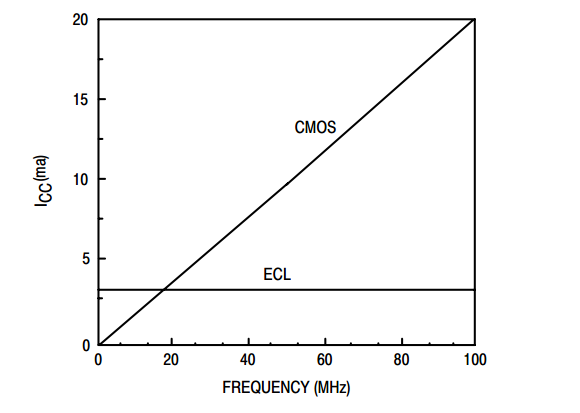

如果我们关注静态功耗,ECL是一个高功率逻辑系列。但是,如果我们考虑动态功耗,ECL可以比CMOS更高效,尤其是在工作频率增加的情况下。如图4所示。

低于20MHz,ECL比CMOS消耗更多的电源电流,但当我们超过这个频率时,ECL变得更有效率。这就是ECL是高频时钟分配的有吸引力的解决方案的原因。

最后要注意的是,射极跟随器(见图1)必须提供大输出电流来为负载电容充电,因此它们会导致电源电压出现明显的瞬态偏差。因此,在某些情况下,建议使用两根独立的电源线:一根用于输入级,一根用于射极跟随器。这可以防止由射极跟随器产生的电源干扰污染ECL差分对。

概括

ECL被认为是一个非常高速的逻辑系列。它通过采用相对较小的电压摆幅并防止晶体管进入饱和区来实现其高速运行。

使用正电源电压的ECL实现被称为正参考ECL或PECL。抗噪性是早期ECL门使用负电源电压的主要原因。后来,PECL开始流行,因为它的逻辑电平与TTL等其他逻辑系列的逻辑电平更兼容。

ECL的静态功耗相对较大,但其整体电流消耗在高频时低于CMOS。因此,ECL在时钟分配电路和其他高频应用中特别有利。

责任编辑人:CC

-

耦合

+关注

关注

13文章

586浏览量

101029 -

发射极

+关注

关注

0文章

36浏览量

10119

发布评论请先 登录

相关推荐

射极耦合逻辑(ECL)基础知识详解

共发射极放大器的特性和偏置,共发射极放大电路应用

一文汇总发射极耦合逻辑的基础知识

一文汇总发射极耦合逻辑的基础知识

评论