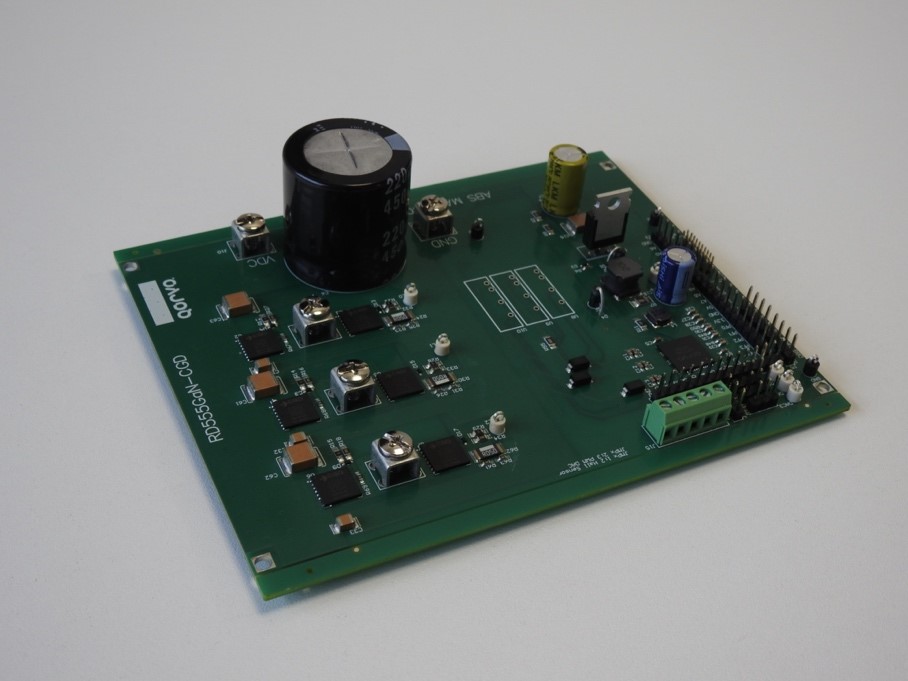

目前,在高功率与高频应用领域,氮化镓(GaN)越来越受到重视,无论是国际大厂,如Qorvo、英飞凌、NXP、Cree、日本住友等,还是中国本土产商,如三安光电、海特高新(海威华芯)、苏州能讯和英诺赛科等,都在这方面不断加大投入力度,以求占得市场先机。

最近,中国本土厂商在GaN晶圆厂建设的脚步不断提速,例如,就在上周,英诺赛科(苏州)半导体有限公司宣布其8英寸硅基氮化镓芯片生产线一期第一阶段产能扩展建设项目量产。预计2021年实现产能可达6000片/月。项目全部达产后预计将实现年产能78万片8英寸硅基氮化镓晶圆。据悉,该项目主要建设从器件设计、驱动IC设计开发、材料制造、器件制备、后段封测以及模块加工的全产业链宽禁带半导体器件制造平台。

无独有偶,就在不久前的4月份,中国本土另一家化合物半导体大厂赛微电子发布了关于与青州市人民政府签署《合作协议》的公告,赛微电子拟在青州经济开发区发起投资10亿元分期建设聚能国际6-8英寸硅基氮化镓功率器件半导体制造项目,一期建成投产后将形成5000片/月的6-8英寸氮化镓晶圆生产能力,二期建成投产后将形成12000片/月的6-8英寸氮化镓晶圆生产能力。

可以看出,以上两家本土企业都在大力发展硅基氮化镓技术,该技术也是众多新兴企业的首选。

硅基氮化镓是潜力股

目前,在氮化镓外延片方面,主要有两种衬底技术,分别是GaN-on-Si(硅基氮化镓)和GaN-on-SiC(碳化硅基氮化镓)。相比较而言,GaN-on-SiC性能相对较佳,但价格明显高于GaN-on-Si。GaN-on-Si的优势是生长速度较快,也较容易扩展到8英寸晶圆。虽然GaN-on-Si性能略逊于GaN-on-SiC,但目前工艺水平制造的器件已能达到 LDMOS 原始功率密度的5-8 倍,在高于2GHz的频率工作时,成本与同等性能的LDMOS 出入不大。另外,硅基技术也将对CMOS工艺兼容,使GaN器件与CMOS工艺器件集成在一块芯片上。这些使得GaN-on-Si成为市场的潜力股,而且主要应用于电力电子领域,未来有望大量导入5G基站的功率放大器 (PA)。

由于像Qorvo、Wolfspeed(Cree)等传统大厂都比较倾向于采用GaN-on-SiC方案,使得该技术成为了目前市场的主流。但是GaN-on-Si凭借其先天优势,正在被越来越多的厂商采用。

与GaN-on-SiC相比,GaN-on-Si方案最大的优势就是衬底成本低,也更容易向8英寸大尺寸晶圆转移,以提升成本效益和投入产出比。此外,其与CMOS具有较好的兼容性,可以利用现有硅晶圆代工厂已有的规模生产优势,实现产品的规模量产和快速上市。而从应用发展角度来看,5G通信对射频元器件的需求正在快速增加过程中,需要大批量、低成本的GaN射频芯片,而这也给GaN-on-Si提供了发展契机。

具体来看,GaN-on-Si器件工艺能量密度高、可靠性高,晶圆可以做得很大,目前在8英寸,未来可以做到10英寸、12英寸,晶圆的长度可以拉长至2米。GaN-on-Si器件具有击穿电压高、导通电阻低、开关速度快、零反向恢复电荷、体积小和能耗低、抗辐射等优势。理论上相同击穿电压与导通电阻下的芯片面积仅为硅的千分之一,目前能做到十分之一。

与传统LDMOS工艺相比,GaN-on-Si的性能优势很明显,它可提供超过70%的功率效率,将每单位面积的功率提高4到6倍,并且可扩展至高频率。同时,综合测试数据已证实,GaN-on-Si符合严格的可靠性要求,其射频性能和可靠性可媲美甚至超越GaN-on-SiC。

GaN既可以用于基站,也可以用于手机当中,目前来看,Macom, Ommic、三安光电,英诺赛科等厂商在重点研发基站用GaN-on-Si射频和功率芯片(包括Sub-6GHz和毫米波两大频段);而在手机等终端应用方面,台积电,英特尔、格芯和意法半导体等晶圆大厂正在重点进行这方面的GaN-on-Si芯片工艺研发。

硅基氮化镓技术革新

GaN,特别是本文重点关注的GaN-on-Si技术,在高频、高功率的应用场合才能充分发挥其效能,而从5G的发展情况来看,目前处于Sub-6GHz阶段,正在向毫米波进发,因此,未来不断壮大的毫米波市场,才是GaN-on-Si大施拳脚的地方。

从器件类型来看,毫米波GaN-on-Si晶体管大部分是HEMT(高电子迁移率晶体管),其在器件异质结结构、栅电极、源漏欧姆接触:、表面钝化等方面,较之于传统的硅技术,都有更高的要求。目前,业界在这方面都取得了进展,如采用CMOS兼容工艺制造80nm的GaN-on-Si HEMT等。

然而,GaN-on-Si技术存在着多种不足和技术挑战,如热阻、射频损耗、应力、位错密度和可靠性、大尺寸材料生长和CMOS兼容工艺制造等,业界正在努力解决这些问题。

像其他横向功率器件一样,硅基氮化镓HEMT的击穿电压随其栅极到漏极距离的增加而增加,松下公司则利用125μm的栅极到漏极的距离,实现了超过10kV的击穿电压。但是,其衬底不是硅,而是蓝宝石。

此外,麻省理工学院团队将GaN HEMT外延层从硅衬底转移到玻璃上,以试图提高横向器件的击穿电压,从大约600V增加到了1.5kV,实验证明硅衬底是导致栅极到漏极距离超过一定值的HEMT击穿电压饱和的根本原因。但是,改用玻璃不是一个很好的解决方案,玻璃的导热系数很低,并且与硅CMOS代工厂不兼容。Imec的一个研究小组则通过局部去除硅衬底获得了成功,实现了3kV的击穿电压。

另外,为了避免与使用玻璃或去除衬底相关的问题,新加坡-麻省理工学院研究与技术联盟,南洋理工大学和麻省理工学院的团队使用硅上绝缘体上氮化镓(GaN-on-insulator (GNOI)-onsilicon),通过使用晶圆键合在硅衬底和器件层之间插入附加的绝缘体,避免了对厚GaN外延层的需求。这种方法具有许多优势,例如:可以去除因为许多位错和较差的导热性而使性能受限的原始过渡层,从而提高器件的可靠性和散热能力;在高温GaN生长之后,可以用一种具有良好硬度的新衬底替换原来的易碎硅衬底,这样可以降低晶圆通过产线时破裂的可能性,提高了良率。

下面看一下异构集成。在与CMOS工艺集成方面,GaN-on-Si具备先天优势。原因自然是因为衬底都是硅,具体不在此赘述。

然而,在异构集成方面,GaN-on-Si同样存在着技术挑战,如热兼容性问题(GaN微波、毫米波电路发热量高,会引起周围Si-CMOS器件的阈值电压漂移、漏电增大等问题),电磁兼容性问题(GaN电路工作时的偏压比较大,电场耦合到CMOS区域,以及射频电路工作时的电磁场分布效应、电磁波辐射等),以及工艺兼容性问题和可靠性问题。

目前,业界正在进行着GaN-on-Si与CMOS集成工艺流程开发工作,以解决以上难题。如开发8英寸GaN与硅CMOS晶圆键合技术;解决GaN和硅CMOS器件和电路制造流程中的工艺兼容问题,包括GaN大晶圆翘曲、易碎、金属污染、高温退火退化等挑战;开发出了GaN-on-Si CMOS单片集成工艺流程,以及GaN器件的模型和PDK等。

结语

GaN在高频(毫米波)射频和功率应用中的前景广阔,而GaN-on-Si凭借其低成本,易于集成等优点,具有很大的发展潜力。而在中国本土,GaN-on-Si则更受欢迎,依托这一巨大市场,相信该技术在不久的将来必定会结出丰硕的果实。

责任编辑:haq

-

半导体

+关注

关注

335文章

27826浏览量

223843 -

GaN

+关注

关注

19文章

1974浏览量

74459 -

毫米波

+关注

关注

21文章

1934浏览量

65074

原文标题:中国企业发力,助攻半导体“潜力股”飞升

文章出处:【微信号:半导体科技评论,微信公众号:半导体科技评论】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

中国半导体设备业:本土企业强势崛起,全球布局步伐加快

格罗方德在马耳他晶圆厂扩建封装测试设施

2025年半导体行业将启动18个新晶圆厂项目

国际汽车芯片大厂计划将部分生产转向中国,本土产业迎来机遇!

Rapidus计划建设1.4nm工艺第二晶圆厂

挑战英伟达:聚焦本土GPU领军企业崛起

英特尔加码俄亥俄州晶圆厂投资,总额飙升至280亿美元

RISC-V在中国的发展机遇有哪些场景?

麦格纳为中国本土汽车制造商提供可重构座椅系统

英飞凌马来西亚居林晶圆厂建设进展顺利

CGD推出高效环保GaN功率器件

CGD为电机控制带来GaN优势

中国本土厂商在GaN晶圆厂建设的脚步不断提速

中国本土厂商在GaN晶圆厂建设的脚步不断提速

评论