以太网数据传输硬件设计实现

系统方案设计

1.1 设计思想

本文研究的是基于FPGA的以太网的MAC层数据处理,目的是能广泛应用于多种嵌入式网络设备的前端设计,如网络视频监控设备、IP数字电视设备、家庭智能设备等。根据FPGA的可重复擦写编程的特点,采用FPGA可以方便对设备的升级和维护。本文为了设计能满足于各种不同的以太网网络环境,和增强系统的可移植性,采取了一系列的措施。

首先,考虑到以太网高速而又庞大的数据量,尤其是载有音视频流的1000M网络,以及开发的成本问题,我们引入了一种针对普通产品开发的Xilinx芯片——Spartan系列。FPGA具有并行执行的特点,相对于其他器件在数据处理上具有明显的速度上的优势,同时Spartan系列FPGA拥有几百Kb甚至几千Kb的块RAM资源,可用于数据的缓存,完全可以满足于1000M以太网数据量的要求。在FPGA的系统设计开发中,常常会采用某些具有特定功能的IP核以提高系统开发的效率,减少成本。考虑到开发周期和设计要求,本系统设计方案采用Xilinx公司的Tri Mode Ethernet MAC IP核实现对MAC数据的主要处理工作,该IP核支持多种工作模式,同时用户可以根据要求实现自定义配置。其次,为了实现网络的IP地址和MAC地址的自动映射,本系统还增加了对ARP数据包的解析和ARP应答功能的设计。除此之外,为了提高系统的通用性,物理芯片需能够支持1000/100/10M以太网、双工/半双工工作模式以及1000M光纤的接入。

1.2 系统功能

根据以述的设计思想,为了满足大部分设备对以太网的MAC数据处理的需求,确定了本系统设计的功能如下:

(1)支持10M/100M/1000M以太网;

(2)支持双工/半双工;

(3)CRC校验和帧长度校验;

(4)MAC地址滤波;

(5)支持ARP解析;

1.3 系统总体结构设计

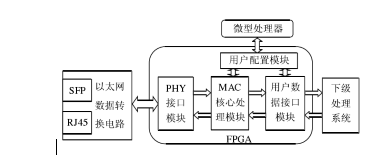

根据上述技术指标及设计思想,图3-1给出了本系统的总体结构框图。本系统可分为五大模块:以太网数据转换电路、PHY接口模块、MAC核心处理模块、用户配置模块和用户数据接口模块。

图3-1系统总体结构框图

(1)以太网数据交换电路

以太网数据交换电路,主要功能是实现双绞线或光纤电缆的以太网物理层数据与MAC层数据的转换,为FPGA提供处理的MAC数据源和送出FPGA的上传MAC数据,是传输介质和FPGA数据交流的桥梁。

(2)PHY接口模块

PHY接口模块,可分为接收PHY和发送PHY接口两个子模块,实现接收数据和发送数据的同步。

(3)MAC核心处理模块

根据以上设计思想,MAC数据的核心处理模块直接采用Xilinx的Tri Mode Ethernet MAC IP核,可以完成MAC地址滤波、数据CRC和长度校验、封装MAC数据帧格式等基本功能,对接受的数据进行相应的好坏标记和对上传的数据进行封装标记。

(4)用户配置模块

用户配置模块主要是实现主控系统正确地完成对IP核寄存器和系统地址信息(IP地址和MAC地址)的配置,同时实时地监控IP核的工作状态。该模块可分为I2C接口和IP核配置两个子模块,I2C接口子模块采用400Kb/s的I2C总线协议,模拟从设备I2C时序;IP核配置子模块模拟IP核HOST配置时序,以实现对IP核寄存器的配置。

(5)用户数据接口模块

用户数据接口模块涉及对通过IP核处理后的接收数据帧和待上传的数据包两部分数据的处理以及ARP功能的实现,可分为接收数据用户接口、上传数据用户接口、ARP解析与应答三个子模块。

芯片的选取

2.1 物理层芯片选择

以太网物理层的处理工作大多数直接采用专业的物理层芯片来完成,完成数据的物理层编解码和收发功能。目前,物理层芯片的生产商以国外为主,如Marvell、NS、Broadcom公司等,其主流产品为100/10M和1000M物理层芯片,随着以太网的速率的提高,万兆物理层芯片也被广泛应用于光纤以太网。国内对芯片的研发起步比较晚,华为、中兴、天津中晶微电子等企业近些年也推出了不少的产品,但是技术还有待发展。

88E1111芯片是Marvell公司Alaska系列的一款千兆以太网收发器,主要应用于10Base-T、100Base-TX、1000Base-T的以太网,采用CMOS工艺,能实现基于CAT5非屏蔽双绞线标准的以太网物理层数据的收发。88E1111支持多种MAC接口模式,有GMII/MII、RGMII、SGMII、TBI和RTBI,是一款应用广泛的以太网物理层芯片。

88E1111芯片采用了Marvell公司的VCT(Virtual Cable Tester,虚拟电缆测试仪)功能,可以使用时域反射技术远程测试电缆故障,减少了设备应答和服务请求的次数,同时还能通过VCT检测线缆潜在的问题和线缆的开路、短路或阻抗不匹配问题,准确度能达到一米。另外,88E1111芯片具有先进的混合信号处理能力,可以以1Gbps的速率完成自适应均衡、消除反射或串扰、数据恢复、误码纠正等功能,是一款抗噪声能力强的低功耗以太网物理层芯片。

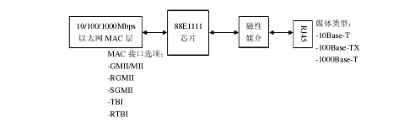

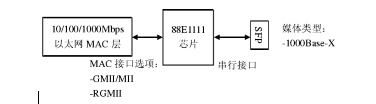

88E1111芯片中嵌入了一个可选的1.25GHzSERDES(并串转换/串并转换器),可以直接与光纤收发器连接,实现1000Base-X光纤标准与1000Base-T双绞线标准传输媒体的转换。通过选择,88E1111可以通过RJ45接口接入1000Base-T双绞线网络或SFP(小型可插拔)模块接入光纤网络,分别如图3-2和3-3所示。

图3-2 88E1111接入双绞线网络

图3-3 88E1111接入光纤网络

除了以上所述,88E1111芯片还支持光纤与铜线自动检测、网络连接的自动协商、可编程的LED驱动等功能,方便了用户对以太网接入的开发。

根据本文系统设计的功能的要求,以太网物理层芯片需满足同时支持RJ45和SFP两种接口,10Base-T、100Base-TX、1000Base-T标准双绞线和千兆光纤介质的传输,半双工和双工切换的工作模式。Marvell公司的以太网物理层芯片88E1111,采用0.13μm的CMOS工艺,是一款低成本、低功耗的千兆以太网物理层芯片,足以满足系统设计的要求

2.2 FPGA主芯片选择

在FPGA的开发设计中,FPGA芯片的选取非常重要,不合理的选取会导致一系列的后续设计问题,甚至会失败;合理的选取不仅避免设计问题,而且可以提高系统的性价比,延长产品的生命周期。通常,FPGA芯片选取需从芯片的供货商和开发工具的支持、电气接口标准、硬件资源、速度等级、温度等级、封装形式、价格七个方面入手。

(1)供货商和开发工具的支持

目前,主要的FPGA供应商有Xilinx公司、Altera公司、Lattice公司和Actel公司等,FPGA的发展迅速,器件的淘汰率随之提高,为了延长产品的生命周期,最好选择货源比较足的主流器件。

从开发工具来看,Xilinx公司的ISE和Altera公司的QuartusⅡ,更新及时、功能强大、界面友好,支持本公司所有器件的设计开发和很多第三方软件的应用,如Synplify Pro、ModleSim等,能将器件的性能发挥到最佳。因此,一般在没有特殊要求情况下,器件从这两家公司中选取。

虽然Altera公司的开发智能程度相对Xilinx公司要高一些,但Xilinx公司具有更强的硬件功能,通过IP核的使用可以达到更高的效率。目前,Xllinx公司的主流器件有Spartan-3、Spartan-3A/3ADSP/3AN、Virtex-4LX、Virtex-4SX、Virtex-4FX、Virtex-5LX、Virtex-5SX、Virtex-5FX、Spartan-6和Virtex-6等系列,其中Spartan-3系列主要应用于逻辑设计;Spartan-3A/3ADSP/3AN主要应用于简单数字信号处理,Virtex-4LX和Virtex-5LX系列主要应用于高速逻辑设计,Virtex-4SX和Virtex-5SX系列主要应用于高速复杂数字信号处理,Virtex-4FX和Virtex-5FX系列主要应用于嵌入式系统。本设计只需要对MAC数据帧做简单的逻辑处理和缓存等等,Spartan-3系列器件足以满足这一需求。

(2)芯片的电气接口标准

目前,数字电路的电气接口标准非常多,在某些大型的系统设计中常常需要同时支持多种电气接口标准。本设计中的FPGA的接口电气标准只采用了LVCMOS2.5V和LVCMOS3.3V,Xilinx公司的绝大部分器件均能够满足。

(3)硬件资源

硬件资源是FPGA芯片选取的重要指标,包括逻辑资源、I/O资源、布线资源、存储器资源和某些底层内嵌功能单元和内嵌专用硬核等。在FPGA设计中,I/O资源和逻辑资源的需求是最需要重点考虑的问题。逻辑资源一般要求消耗的资源不超过70%,主流FPGA器件中,逻辑资源都比较丰富,比较容易选择。I/O资源需要注意的是避免过度的消耗,因为过度的消耗可能会导致FPGA负荷过重,器件发热量过大,以影响器件的速度性能、工作稳定性和寿命,设计中也要充分考虑器件的散热问题。另外,局部布线资源也要充足,以免影响电路的运行速度。在一些特殊场合,特别是数据量比较大的情况下,还得考虑存储器资源,如BRAM或LUT资源。还有锁相环、DSP等底层内嵌功能单元或内嵌专用硬核可以根据具体的设计作为参考需求。

(4)速度等级

对于芯片速度等级的选取,有一个基本原则:在满足应用需求的情况下,尽量选择速度等级低的芯片。因为速度等级高的芯片更容易产生信号反射,增加价格成本,延长开发周期。本设计的主时钟最高位125M,XC3S400芯片具有-4和-5两个速度等级,-4等级的最高可以达到250M,为节约成本,选取的芯片采用-4等级。

硬件电路设计

3.1 以太网变换电路设计

以太网数据变换电路,实现的是以太网传输媒介上的物理层数据与MAC层数据的转换,为FPGA提供待处理的MAC数据源和输出待上传的MAC数据,本设计主要是选择物理层专业芯片88E1111完成这一功能,其电路设计包括以下几个方面:

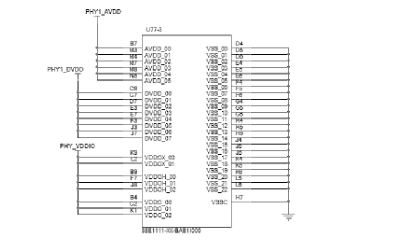

88E1111芯片支持两种电平:2.5V和1.0V,有时也可用1.2V代替1.0V。如图3-4所示为芯片的电源电路图,PHY_VDDIO采用2.5V,为芯片I/O引脚供电,与芯片引脚VDDO、VDDOH、VDDOX相连;PHY1_AVDD提供内部模拟逻辑电平,为2.5V,与AVDD引脚相连;PHY1_DVDD提供内部数字逻辑电平

图3-488E1111芯片电源电路

为1.0V,与DVDD引脚相连。为了提高电源的稳定性,电源PHY_VDDIO、

PHY1_AVDD、PHY1_DVDD需接入一些滤波电容,以减少电源噪声。

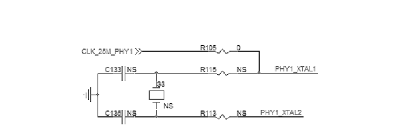

88E1111芯片对数据的处理需要有一个参考时钟,一般通过XAT1引脚输入25M或125M的参考时钟,或通过XAT1和XAT2直接接一个晶振。本设计采用XAT1引脚输入25M的时钟,以减少晶振的使用数量,如图3-5所示,CLK_25M_PHY1与XAT1引脚相连,提供25M的时钟;为了保证电路的可调性,同时在XAT1和XAT2的两端添加一个晶振,作为参考时钟的备用方案。

图3-588E1111芯片时钟电路

(2)配置电路设计

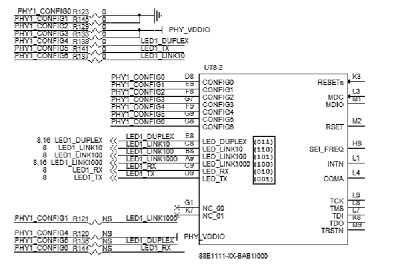

在88E1111的芯片设计中,器件物理地址、PHY操作模式、自动协商模式、MDI(Media Dependent Interface,媒介相关接口)交叉功能、PHY接口模式等的配置需通过芯片CONFIG0~CONFIG6引脚硬件配置来实现,CONFIG0~CONFIG6引脚配置位映射关系表和各配置寄存器的定义描述分别如表3-3和表3-4所示。

在硬件电路设计中,CONFIG0~CONFIG6配置位的选择通常是通过与LED输出引脚、VDDO或者VSS引脚的连接来完成的,其各引脚与配置位的映射关系如表3-5所示。

为了方便开发设计,本设计将芯片地址设置为00000,屏蔽PAUSE帧,同时使能MDI交叉连接、光纤与铜线接入自动识别、能量检测功能,其自动协商支持所有网路模式;125MHz的数据发送的参考时钟由FPGA提供,125MHz时

表3-3CONFIG0~CONFIG6引脚配置位映射关系表

| 引脚 | Bit[2] | Bit[1] | Bit[0] |

| CONFIG0 | PHYADR[2] | PHYADR[1] | PHYADR[0] |

| CONFIG1 | ENA_PAUSE | PHYADR[4] | PHYADR[3] |

| CONFIG2 | ANEG[3] | ANEG[2] | ANEG[1] |

| CONFIG3 | ANEG[0] | ENA_XC | DIS_125 |

| CONFIG4 | HWCFG_MODE[2] | HWCFG_MODE[1] | HWCFG_MODE[0] |

| CONFIG5 | DIS_FC | DIS_SLEEP | HWCFG_MODE[3] |

| CONFIG6 | SEL_TWSI | INT_POL | 75/60OHM |

表3-4各配置寄存器定义描述

| 配置寄存器 | 定义描述 |

| PHYADR[4:0] | 器件的物理地址,在MDC/MDIO配置模式下,表示器件五位的物理件地址;在I2C配置模式下,表示器件物理地址phyaddr[4:0],phyaddr[6:5]固定为10。 |

| ENA_PAUSE | PAUSE 帧使能信号,高有效;同时影响寄存器4 的默认值 |

| ANEG[3:0] | 自动协商模式配置寄存器,10/100/1000Base-T模式下由ANEG[3:0]配置决定,而1000Base-X模式下由ANEG[3:2]配置决定,具体的配置映射关系可参考88E1111芯片手册。 |

| ENA_XC | 交叉连接使能信号,1时MDI交叉功能有效,反之则无效。 |

| DIS_125 | 125MHz时钟使能信号,0使能。 |

| HWCFG_MODE[3:0] | 硬件配置模式,决定了PHY接口模式,常用的有:1000Base-X模式下RGMII为0011;1000Base-X模式下GMII 为0111;10/100/1000Base-T模式下RGMII为1011;10/100/1000Base-T模式下RGMII为1111;其他的模式配置可参考88E1111芯片手册 |

| DIS_FC | 光纤与铜线接入自动识别使能信号,0有效。 |

| DIS_SLEEP | 能量检测使能信号,0有效。 |

| SEL_TWSI | 寄存器配置模式选择,0表示采用MDC/MDIO配置模式,1表示采用I2C配置模式。 |

| INT_POL | 中断电平值,0表示高电平中断,1表示低电平中断。 |

| 75/60 OHM | 终端电阻匹配选择信号,主要用于光纤接入模式下,0采用50OHM,1采用75OHM。 |

表3-5各引脚与配置位的映射关系

| 引脚 | Bit[2:0] |

| VDDO | 111 |

| LED_LINK10 | 110 |

| LED_LINK100 | 101 |

| LED_LINK1000 | 100 |

| LED_DUPLEX | 011 |

| LED_RX | 010 |

| LED_TX | 001 |

| VSS | 000 |

钟输出设置为无效;IPQAM项目的CPU对从设备的寄存器配置采用的是I2C总线方式,因此88E1111需配置成I2C从模式;PHY接口采用GMII/MII模式,减少FPGA对时钟的时序要求。因此,如图3-6配置电路图所示,默认情况下将CONFIG0~CONFIG6引脚分别配置为000、000、111、111、111、001、110。但是为了系统的升级维护,对CONFIG1、CONFIG4、CONFIG5、CONFIG6引脚设置了配置保留值,根据不同的需求本系统可以支持PAUSE帧的传输、RGMII的PHY 接口、MDC/MDIO寄存器配置等工作模式。

图3-6 88E1111配置电路

(3)RJ45接口和SFP接口电路设计

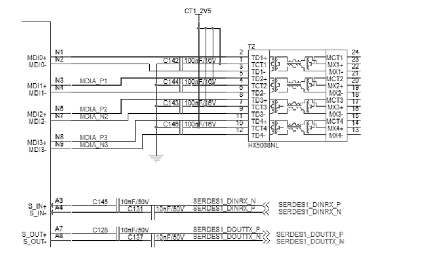

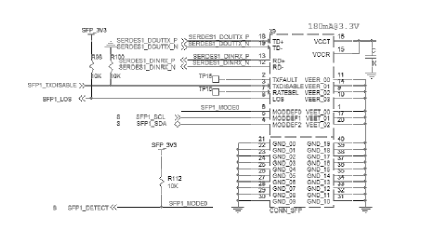

本系统支持普通双绞线和光纤两种媒介接入方式,双绞线的接入采用通用的RJ45接口,其电路图如图3-7所示,88E1111芯片的四对MDI引脚直接与HX5008NL芯片的四对TD引脚相连,实现与RJ45接口的连接,完成双绞线与88E1111芯片的数据交换;光纤的接入采用SFP接口,其电路图如图3-8所示,88E1111芯片的S_IN±引脚与SFP接口芯片的RD±引脚相连,接收光纤电缆上的数据;S_OUT±引脚与TD±引脚相连,完成本地的数据的输出;同时SFP接口芯片采用I2C配置模式,与系统设计一致。

图3-7 RJ45接口电路

图3-8 SFP接口电路

责任编辑:lq6

-

FPGA

+关注

关注

1634文章

21830浏览量

608035 -

以太网

+关注

关注

40文章

5480浏览量

173188 -

数据传输

+关注

关注

9文章

1972浏览量

65010

原文标题:以太网数据传输硬件设计实现

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

LORA模块的数据传输速率

以太网端口双工模式是什么意思

以太网端口的类型和特性

速锐得解码汽车以太网技术特点接口定义数据传输及应用

以太网接口的数据传输原理详解

TIDA-010076-通过单对以太网 (T1) 实现菊花链式电源和数据传输的PCB layout 设计

怎样去设计一种基于FPGA的以太网数据传输硬件?

怎样去设计一种基于FPGA的以太网数据传输硬件?

评论