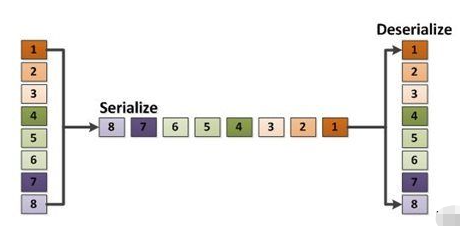

随着数据宽带网络的迅猛发展,需要不断提高系统设备的业务容量。目前的趋势是采用高速串行通信技术,即采用串行解串器SERDES,把低速的并行数据转换为高速串行数据连接。SERDES串行接口可在背板或电缆/光纤等不同互联介质上传输高速信号,在提高系统传输带宽的同时,有利于印刷电路板(PCB)布线,并降低系统功耗和噪声。

TI(德州仪器)推出一系列高性能的通用SERDES,满足高带宽、高性能的应用要求,广泛应用在WI系统、接入设备、传送网络、数据通信等通信产品,以及工业控制系统。本文以TLK3132为例,详细介绍了SERDES工作原理和器件特点,并以WI系统中的CPRI应用需求为例,提供TLK3132的设计方法等。

2TLK3132工作原理

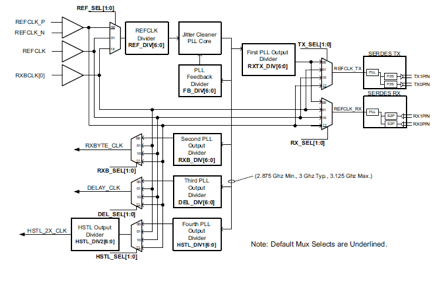

TLK3132是TI推出的一款通用两通道串行器/解串器(SERDES),采用90nm工艺,能满足一些低功耗的应用需求,内部功能模块如图1所示。SERDES Core的发送部分用于实现8位、9位或10位宽字的并串转换,然后通过一根电缆或印刷板(PCB)走线发送出去,而接收部分则将串行数据进行串并转换为8位、9位或10位宽的并行字。

图1 TLK3132内部功能框图

下面详细介绍了6个功能模块及其应用特点:并行接口、串行接口、时钟分布电路、8B/10B编解码电路、PRBS测试以及相关寄存器访问控制接口MDIO。

2.1 并行接口

TLK3132器件每个通道并行收发侧分别包含8位数据位和两位灵活的控制位,支持各种通用的并行接口,如千兆以太网的介质无关接口RGMII、GMII、RTBI、TBI,以及RNBI、NBI、REBI、EBI、TBID和NBID等多种工作模式。对于DDR模式而言,既支持位边沿采样(采样时钟边沿与数据位翻转边沿同步),也可支持位中间采样(采样时钟边沿处于数据位的中间位置);对于SDR模式而言,既支持上升沿采样并行口数据,也支持下降沿采样数据。由于使用同步时钟,在布线时时钟线和数据线必须等长且时钟线尽量不要分叉,此外通过配置不同的数据采样边沿,可以降低系统互连设计的风险,提高系统设计的鲁棒性。

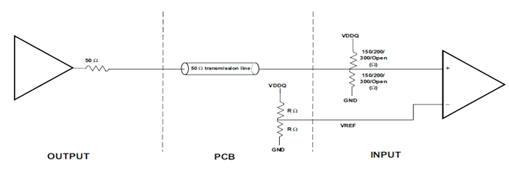

并行接口采用单端的HSTL Class1电平接口,遵循EIA/JESD8-6标准电气指标规格,同时支持1.5V或1.8V的电源电压。为了提高HSTL高速接口的SI性能,TLK3132并行接收侧集成了可寄存器配置的匹配电阻,采用戴维南等效电路匹配方式,等效于加一个匹配电阻到VDDQ/2,同时也可关闭内部的阻抗匹配电路,如图2所示;并行发送侧可通过寄存器配置4种不同的边沿速率。

图2 并行口等效框图

2.2串行接口

TLK3132支持的串行接口速率从600Mbps到3.75Gbps,不同通道可独立地工作于全速率、半速率以及1/4速率模式。为了补偿高速信号传输的介电损耗和趋肤效应,TLK3132高速串行接口发送端具有强大的去加重能力,共支持15级调节能力(达到10.87dB补偿),同时支持8级的输出摆幅设置(从125mV到1375mV);接收端包含有自适应均衡器,最大补偿能力得到12dB以上,保证高速串行接口的SI性能。在3.072Gbps速率下可支持50inches的FR4传输或30m的电缆传输(特性阻抗50欧姆),解决了高速信号在背板侧或前基板的设计难题。

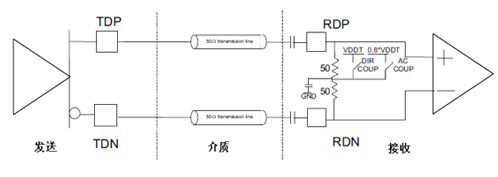

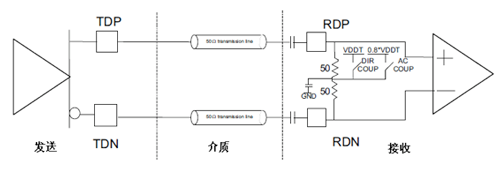

图3是TLK3132高速串行接口的AC耦合框图,采用CML高速电平接口,发送侧内部集成了50欧姆的匹配电阻。接收端支持DC和AC耦合,若采用直流耦合时,共模电压由发送侧决定,匹配电阻直接上拉到VDDT,若采用交流耦合,为得到最优的共模偏置电压,选择芯片内部0.8VDDT的偏置电压。在实际电路设计中,推荐采用交流耦合方式,容易实现不同接口的电平转换,并可去除共模噪声,避免外界噪声对接收端的影响。

图3 串行接口AC耦合

2.3 8B/10B编解码及通道同步

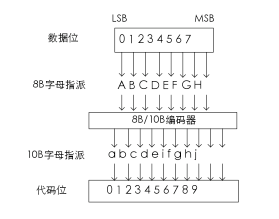

在串行链路通信中,为了实现信号时钟的恢复,需要避免出现长串0和长串1,同时保持电路上正负电平平衡,能正确地交流耦合避免信号失真,需要传输信号中的0和1数量数目相等,因此业界广泛应用8B/10B编解码方法:实现8B到10B的映射(图4),即一个字节(8bits)用10bits来表示,从中挑选出连续0或者1个数不会超过3个,0和1的个数差不大于2 (最多6个’0’或’1’)。

为了实现信号流中0和1的个数相等,在设计编码时,针对每个原码设计了两个编码,如:十六进制字节0x3B,对应两个编码分别为110110 1001(1的个数多于0)和001001 1001(0的个数多于1),在发送过程中不断统计当前数据流中0和1的个数差,如果0的个数大于1的个数,则发送0X3B字节时取前面一种编码;反之,则取后面一种编码,这样就不断平衡数据流中0和1的个数,保持串行数据中0和1的数量相同。

图 4 8B/10B映射

串行通信中,除了有效数据外,还需要一些控制字符传送某些控制协议。因此,在8B/10编码中,包含下面两种信息:

1)D分组,用于传递有效业务数据;

2)K分组,用于传递控制信息等,如K28.5控制字符10B编码包含0011111010或1100000101(连续5个’1’或’0’,称为Comma,千兆以太网使用的8B/10B编码方案中Comma是唯一的),用于定位串行数据流中每10个bits组的边界,避免数据流出现错误时无法界定每10bit的边界,导致链路中断。

TLK3132内部兼容了IEEE802.3-2005中关于1000BASE-X物理编码子层(PCS)技术(注:不支持自协商功能),如CTC FIFO、8B/10B编解码电路等模块,同时这些模块设计时非常灵活,通过MDIO口进行寄存器设置可以使能或关闭。此外,TLK3132通过检测Comma进行通道同步判断,内部的状态机也是参考1000BASE-X规定的链路同步和链路失步建立机制,因此TLK3132能被广泛应用在WI、数据网络、以太网等不同领域。

2.4时钟电路

SERDES实现的一个关键技术是时钟的产生和分布,图5是TLK3132芯片内部的时钟架构。时钟配置非常灵活,支持单端或差分参考时钟输入,同时包括多个高频锁相环电路:

1)高速SERDES Core包含了一个高频倍频器(用于产生高速串行数据)和一个基于相位内插的CDR(在接收端用于从串行数据中恢复时钟)。

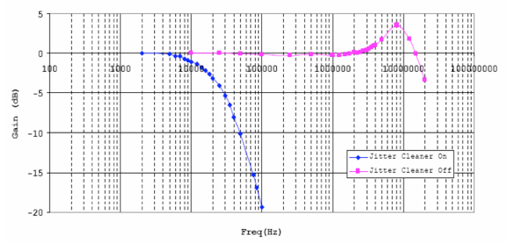

2)由于串并模块里的高频倍频器环路带宽很大,最大可达30MHz左右。故TLK3132内部集成了一颗基于LC振荡器的抖动滤除锁相环,环路带宽通常设置在几百KHz以内,可以对输入参考时钟进行滤除,降低参考时钟对几百KHz 以上抖动性能的要求,图6是TLK3132发送链路在抖动滤除器打开和关闭下的环路传递函数。此外,抖动滤除器也可对链路恢复的时钟(只可接收CH0通道的恢复时钟RXBCLK(0))进行抖动滤除,提高恢复时钟的信号质量。

3)PLL1、PLL2、PLL3和PLL4作为倍频器,和前级抖动滤除锁相环电路配合,分别产生适合的时钟频率以满足系统各个模块的需求。

图5 内部时钟架构

图6 TLK3132内部锁相环环路带宽

2.5 PRBS测试

TLK3132支持PRBS码的产生和验证,便于系统定位链路故障,提高设备的可维护性。TLK3132内部有两套PRBS测试方法,一个在SERDES Core内部(通过寄存器0x9011/0x9012配置),该测试一般是只针对生产测试,且控制性能受限,在电路设计中一般不用该功能;另一个是SERDES Core外面(图1所示),支持 PRBS测试多项式是 ,可以通过寄存器配置(0x10)或外部引脚PRBSEN逻辑控制打开或关闭。此外,PRBS验证时可通过GPO[1:0]管脚监控PRBS测试误码情况,也可访问寄存器0x1D读取误码数(当读取该寄存器后,将从新开始误码计数)。

2.6 MDIO接口和寄存器访问

TLK3132内部寄存器访问通过MDIO管理接口实现(遵循IEEE 802.3 Clause 22规格),包括管理数据时钟(MDC)和管理数据输入输出(MDIO)。由于Clause 22直接寻址寄存器空间限制,TLK3132增加了一些扩展寄存器,故支持两种寻址方式:

1)直接寻址:主要包括与物理层相关的链路配置,地址空间分布在0x00~0x1F,PA[0]的高低电平决定对TLK3132的CH0通道或CH1通道进行操作;

2)间接寻址:TLK3132的一些扩展功能访问,如内部时钟配置、I/O性能配置等。地址空间分布在0x9000~0x9900,不同通道的功能有独立的寄存器进行配置。通过间接地址访问寄存器,需要先把寄存器地址写到0x1E地址,然后把相应的控制字写到0x1F地址或从0x1F地址读取相应的寄存器值。

3 TLK3132在CPRI接口的应用

为了处理射频模块拉远技术中基带单元和射频单元的光纤链接,国际上成立两个标准化组织:一个是CPRI (Common Public Radio Interface),在2003年由华为、爱立信、NEC、西门子和北电发起成立的组织,致力于基带、射频接口的标准化;另一个是OBSAI (Open Base Station Architecture Initiative),由诺基亚、LG电子、三星电子等成立的联盟。二者都定义了使基带和射频分离的标准化接口,也就是将宏基站分为基带单元BBU和远端射频单元RRU两部分,BBU和RRU之间传送I/Q数据和控制管理数据,其信号格式就是CPRI或者OBSAI所定义的标准接口。本文以CPRI接口为例,详解TLK3132在射频模块拉远技术中的应用。

3.1 CPRI接口

CPRI接口在传输用户界面定义了物理层layer1和数据链路层layer2两层协议。在物理层中,将上层接入点的数据进行串并/并串转换,以及物理层的编解码(CPRI接口推荐采用8B/10B,遵循IEEE 802.3 2005 Clause36建议);在数据链路层,对上层接入点的I/Q数据、物理层协议数据、网络协议数据(包括以太网数据、高层数据链路协议数据)和厂家自定义的控制信息等进行相应的处理。

目前CPRI有三种建议的链路速率,分别是614.4Mbps、1228.8Mbps、2457.6Mbp。在发送侧,把I/Q数据、控制协议信息、同步信息等复用为CPRI帧结构信息,经过物理层的8B/10B编码后,通过光纤长距离传播(几公里到几十公里);在接收侧,CPRI帧信号经过串并转换后经过8B/10解码成相应的I/Q数据和控制协议信息,交由上层数据链路处理。

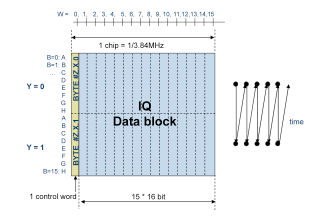

CPRI帧分成基本帧单元和超帧单元。基本帧单元的帧频是3.84MHz,包括16个字(表示为W=0…15,其中W0为控制字,后15个字为I/Q数据),根据不同的链路速率,字的长度分别为8bits、16bits(如图7所示)、32bits。超帧单元是由256个基本帧单元组成,其中,第1个基本帧单元里的控制字写入K28.5标志作为超帧的同步控制信息,其余的255个基本帧单元里的控制字包含控制和管理字(C&M)、厂商自定义控制字等,并预留一些控制字。

图7 线速率1228.8Mbps的CPRI基本帧结构

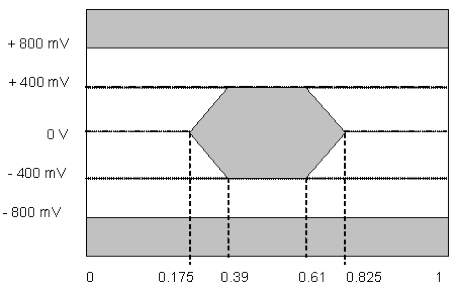

在高速数据链路通信中,抖动指标是非常关键的,CPRI接口相应推荐了高速串行信号的眼图和抖动规格。在SERDES发送侧,CPRI要求的眼图模板如图8所示。

图8 CPRI接口发送输出眼图模板(E.x.LV)

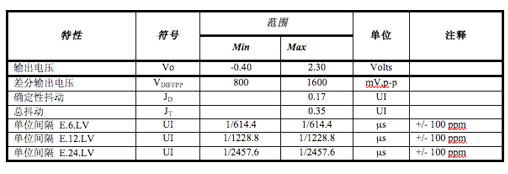

表1 E.6.LV, E.12.LV and E.24.LV发送器AC定时规格 (参考资料CPRI Specification V2.0)

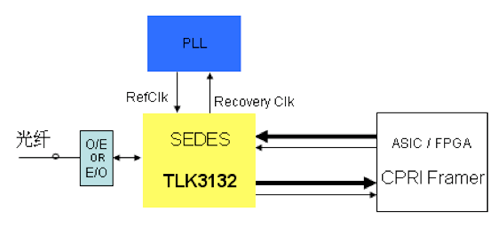

在CPRI接口的实现中,TLK3132完成高性能的串/并、并/串转换,以及CPRI帧的同步和8B/10B编解码,即CPRI接口物理层的相关功能实现。

3.2 应用例子

根据前面关于TLK3132的器件特点分析和CPRI接口介绍,TLK3132可以很好地满足CPRI接口的应用要求,图8是TLK3132在CPRI链路中的一个典型功能框图:TLK3132接收来自光电转换后的高速串行电信号,经串并转换后,提取相应控制字符和有效字符并进行8B/10B解码,送给ASIC或FPGA进行CPRI解帧处理;同时,也接收来自ASIC/FPGA的CPRI帧信号,进行相应的8B/10B编码后送给SERDES Core完成并串转换。

在该电路中,TLK3132恢复时钟送给PLL作为参考时钟,同时其参考时钟又来自PLL的输出时钟。为保证内部CDR可靠工作,TLK3132要求参考时钟跟输入高速串行数据的频偏控制在+/-200PPM以内,因此外围PLL在失锁情况下,必须保证本地振荡器的自由振荡频率要足够稳定,通常建议采用基于压控晶振的时钟方案。

图8 TLK3132在CPRI接口的典型应用

下面例子说明如何通过MDIO设置TLK3132相关寄存器的软件配置。假设:CH0和CH1通道串行速率分别为1228.8Mbps和2457.6Mbps、并行接口采用SDR接口并工作在NBI模式、使能内部8B/10B编解码器、差分参考输入122.888MHz时钟,内部抖动滤除锁相环关闭,则在TI的TLK3132评估板上参考软件配置如下。

START

CLAUSE 22 //选择CLAUSE 22模式

SETPHYADD(00) //选择物理地址0

WRITE(00, 8000) //软件复位芯片,即对所有寄存器进行复位

READ(11, 3590, FFFF) // 验证MDIO 功能是否正常

WRITE(1E, 9100) //把0x3FF0写入0x9100寄存器,差分参考输入作为SERDES Core的参考时钟

WRITE(1F, 3FF0)

WRITE(1E, 9000) //高频倍频器的倍频系数设为10

WRITE(1F, 1515)

WRITE(1E, 9001) //设置CH0为1/2速—1228.8Mbps、CH1为全速—2457.6Mbps

WRITE(1F, 6060)

WRITE(10, 8400) //并行接收时钟选择各自通道的恢复时钟

WRITE(11, B197) //并口为SDR且工作在NBI模式、上升沿打数据、8B/10B使能

WRITE(1E, 9002) //设置CH0通道接收为交流耦合、自适应均衡

WRITE(1F, 1005)

WRITE(1E, 9004) //设置CH1通道接收为交流耦合、自适应均衡

WRITE(1F, 1005)

WRITE(1E, 900A) //设置CH0通道串行发送端的摆幅为1000mV,去加重为9.52% (0.87dB)

WRITE(1F, 0B21)

WRITE(1E, 900C) //设置CH1通道串行发送端的摆幅为1000mV,去加重为9.52% (0.87dB)

WRITE(1F, 0B21)

WRITE(10, 8C00) //数据通道复位

PAUSE(100) //等待芯片配置生效

WRITE(1E, 901B) //检查SERDES Core内部锁相环是否锁定

READ(1F, 0011, 0011)

STOP

3.3 实验测试

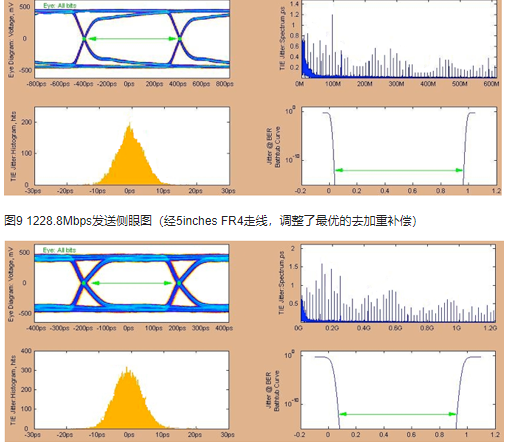

由于串行口速率高达1228.8Mbps和2457.6Mbps,对PCB的layout提出较大的挑战。同时TLK3132具有非常优秀的损耗补偿能力,可以调整最佳的去加重补偿等级,以得到最佳的信号完整性性能。

在3.2节的例子中,反复发送K28.5字节数据,实际测试到的TLK3132发送端眼图如图9和图10(分别对应的串行速率为1228.8Mbps和2457.6Mbps),抖动主要来源于随机噪声,眼宽均在0.9UI以上,具有非常优越的抖动性能(通过适当调整去加重能力补偿传输线FR4的损耗,以提高SI性能)。

图10 2457.6Mbps发送侧眼图(经5inches FR4走线,调整了最优去加重补偿)

4总结

TLK3132是一款低功耗、低抖动、低成本、高性能的多速率收发器,灵活的内部模块配置功能使其广泛地应用于高速串行通信。

为了降低无线网络的组网成本和提高覆盖范围,射频拉远技术广泛应用在3G网络建设,可把原基站内的基带单元和射频单元通过标准化接口(如CPRI等)进行分离,达到一处机房多处天线配置的网络布局,以减少运营商对固定机房的投资。作为CPRI接口实现的一个关键技术—高速串并/并串收发器,TLK3132提供非常优越的SI性能、标准的8B/10B和通道同步处理、灵活的片内时钟产生和分布等,完全能满足高可靠、多速率的CPRI接口标准要求。

责任编辑:gt

-

接口

+关注

关注

33文章

8728浏览量

152107 -

光纤

+关注

关注

19文章

3960浏览量

73734 -

电缆

+关注

关注

18文章

2755浏览量

55201

发布评论请先 登录

相关推荐

SERDES工作原理和器件特点是什么?

TLK3132,pdf(2-Channel Multi-Ra

高性能SERDES在CPRI接口的应用分析

TLK3132工作原理 CPRI接口应用(一)

TLK3132 双通道 600Mbps 至 3.75Gbps 多速率收发器

通用两通道串行器/解串器TLK3132的工作原理及应用

通用两通道串行器/解串器TLK3132的工作原理及应用

评论