作为半导体晶圆清洗技术国际会议,由美国电化学会(ECS)主办的“International Synmposium on Semiconductor Cleaning Science and technology (SCST)”和比利时imec主办的“International Symposium on Ultra Clean Processing of Semiconductor Surfaces (UCPSS)是著名的半导体清洗技术的正式学术活动。

相比之下,由美国私人技术咨询公司Linx Consulting主办的Surface Preparation and Cleaning Conference(SPCC)每年在美国俄勒冈州举行。此前,Sematech 是美国半导体制造强化研究机构的一部分,是半导体行业信息收集活动的一部分,但随着该研究机构的解散,该机构由 Linx Consulting 接管和运营,不是学术活动。今年,该活动照常举行了。

清洁过程的数量和未来的预测数量

SPCC 2021 的主旨演讲由半导体技术趋势研究公司 IC Knowledge 就高级 DRAM、NAND 和逻辑器件的未来小型化趋势发表演讲。图 1 是这三种器件制造过程中清洗步骤数的过去和未来趋势。

关于DRAM清洗,随着微细化进行到1x-nm(可能19/18-nm)、1y-nm(同17/16-nm)、1z-nm(同15nm),清洗工序数增加超过200个,1+-nm(14-nm)及以后,代替使用浸没ArF光刻(光刻 - 蚀刻 - 重复清洗)的多图案化,由于采用EUV光刻的单图案化,清洗步骤减少。然而,在1μ-nm及更高版本,由于必须采用EUV光刻的双图案,清洗步骤的数量预计将增加。

在DRAM清洗中,晶圆背面和斜面清洗的步骤数量最大,电阻剥离后清洗,CMP后清洗是仅次于此的。值得一提的是,从1x-nm开始,SCCO2(超临界二氧化碳)用于高纵横比圆柱形电容器的清洗和干燥。为了防止图案坍塌,使用不产生表面张力的超临界流体。

3D NAND 的清洗,以三星的 V-NAND 工艺为例,清洗步骤直到 128 层,160 层为80 层两级重叠结构,276 层为 96 层三级重叠结构,清洗步骤不断增加。368层为96层4级,512层为128层4级重叠结构,清洗步骤数超过250步。在 NAND 清洗步骤中,未来,背面、斜面和 CMP 后清洁呈上升趋势。

以台积电的技术节点为例,逻辑器件的清洗,但随着小型化的进展,清洗次数增加,从5nm的EUV光刻全面引入,ArF多图案化在关键层被更改为EUV单图案化,清洗步骤减少。然而,在1.5nm及更高版本,由于EUV被迫采用双图案,清洗过程增加。在逻辑器件的清洗中,与其他器件一样,背面和斜面清洗最为多,但多层布线结构的BEOL清洗次数明显多于内存过程。

清洗过程是所有工艺中出现最多的过程,今后将进一步增加。这是防止半导体器件产量下降的关键过程。

在SPCC 2021中,日本进行了三次在线演讲。

晶圆蚀刻中溶解氧的连续监测(Horib场高级技术)

SiGe 通道门全周结构中的选择性 Si 蚀刻(三菱化学/比利时 imec)

湿洗中的晶圆干燥问题(东京电子)

东京电子预计,在DRAM之后,超临界流体清洗和干燥将用于NAND和尖端逻辑(参见图2)。自 2010 年代中期以来,三星将其子公司 SEMES 的多叶超临界清洗和干燥设备引入 DRAM 量产。

在SPCC 2021中,imec给出的蚀刻Ru是一种新布线材料,并宣布在未来半导体工艺中蚀刻和随后的清洗,如叉片的各向异性蚀刻的下一代晶体管。

编辑:jq

-

半导体

+关注

关注

334文章

27475浏览量

219603 -

NAND

+关注

关注

16文章

1685浏览量

136216 -

半导体晶圆

+关注

关注

0文章

35浏览量

5129

原文标题:市场 | 半导体制造这一关键步骤会如何发展和变化?

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

镓在半导体制造中的作用

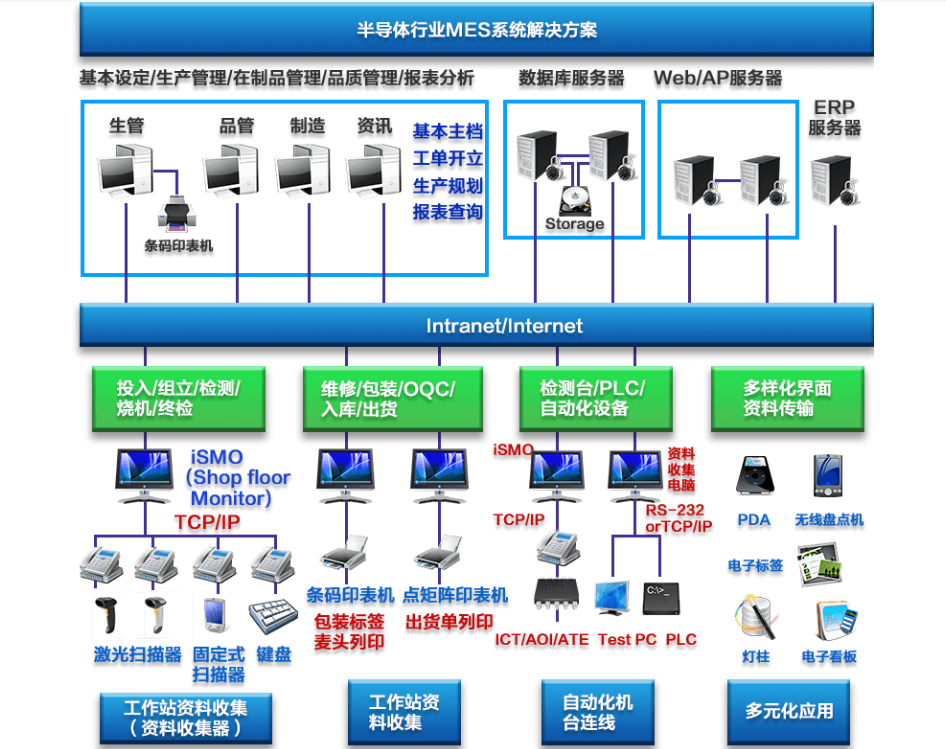

半导体制造行业MES系统解决方案

半导体制造三要素:晶圆、晶粒、芯片的传奇故事

全球半导体制造业迈向新高:SEMI预测未来两年产能大幅提升

半导体制造商必须适应不断变化的格局

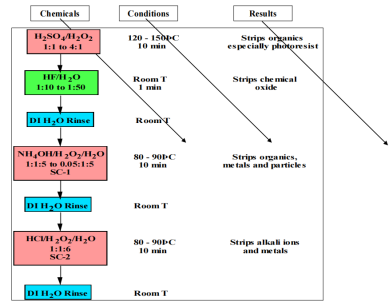

硅晶片清洗:半导体制造过程中的一个基本和关键步骤

半导体制造技术节点:电子科技飞速发展的幕后英雄

主轴维修:关键步骤和要点有哪些?|深圳恒兴隆机电.

半导体制造中混合气体需精确控制

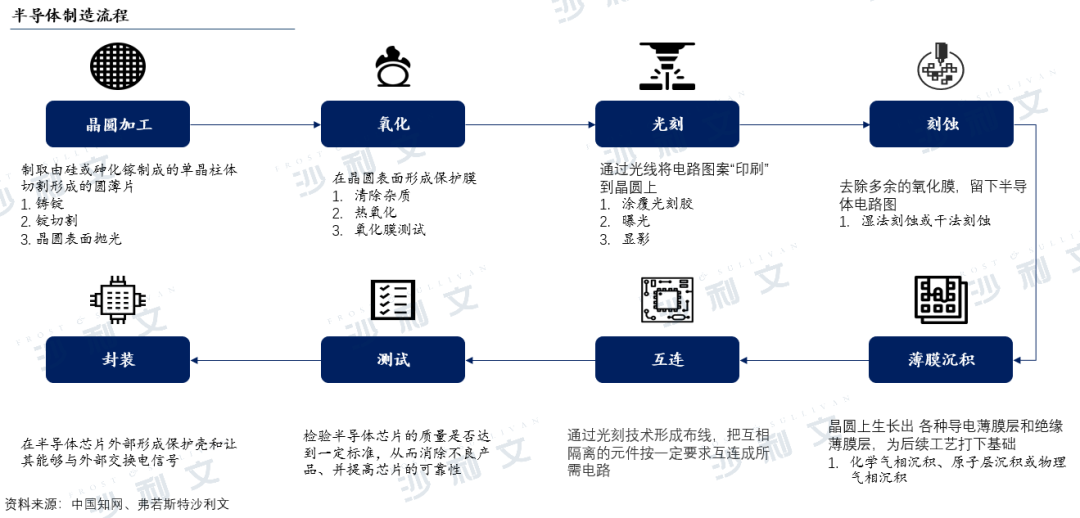

制造半导体芯片的十个关键步骤

深入探讨半导体制造这关键步骤未来的发展和变化

深入探讨半导体制造这关键步骤未来的发展和变化

评论