Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。

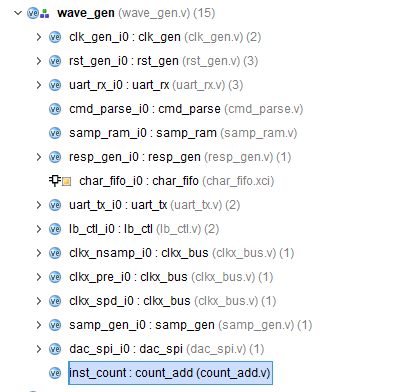

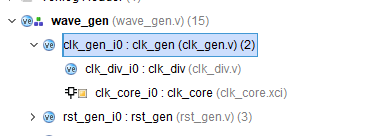

这里我们使用的Vivado版本是2017.2,使用的例程是Vivado自带的wavegen工程,并在工程中增加一个计数器模块,如下图所示

在这里插入图片描述

这个模块的代码也很简单,就是加1计数

modulecount_add( inputclk, inputrst, outputreg[7:0]res ); always@(posedgeclk)begin if(rst) res<= 8'b0; else res <= res + 1'b1; end endmodule

我们要把这个模块当做Reconfiguration Module,把它替换成另外一个module: count_sub,就是每个周期减1计数。

modulecount_sub( inputclk, inputrst, outputreg[7:0]res ); always@(posedgeclk)begin if(rst) res<= 8'b0; else res <= res - 1'b1; end endmodule

下面开始进行Partial Reconfiguration的配置

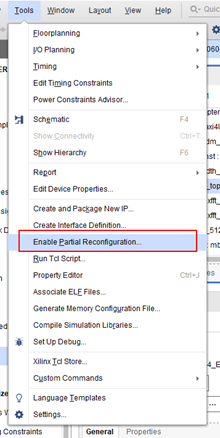

首先打开工程,并将其中一个Reconfiguration Module添加到工程中即可,这里我们选择将count_add添加到工程中,选择Tools->Enable Partial Reconfiguration

在这里插入图片描述

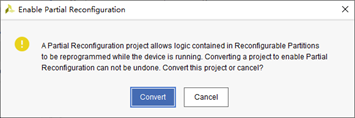

出现下面的对话框,点击Convert。该对话框是指如果使能了Partial Reconfiguration模式,是不能返回到普通模式的。

在这里插入图片描述

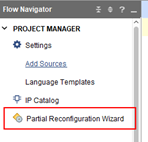

此时在Flow Navigator的PROJECT MANAGER下面就会出现Partial Reconfiguration Wizard的选项

在这里插入图片描述

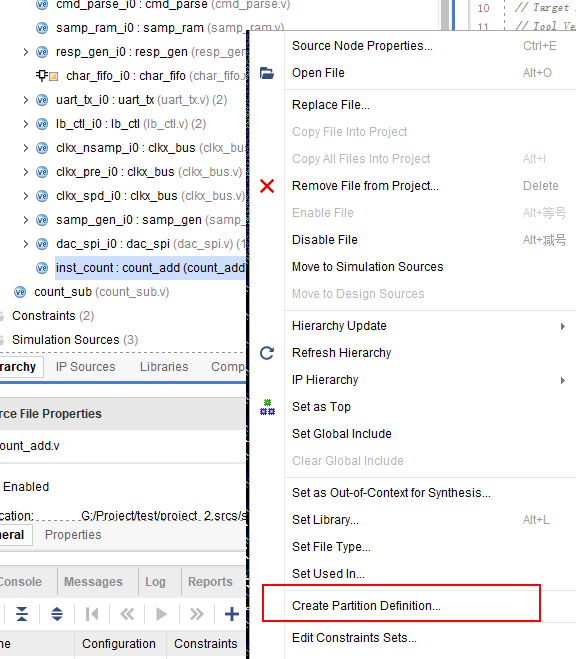

右键要reconfiguration的模块,即inst_count,并选择Create Partition Definition

在这里插入图片描述

此时,弹出对话框提示我们输入创建的Partition的名字,我们起名为count_demo,点击OK

在这里插入图片描述

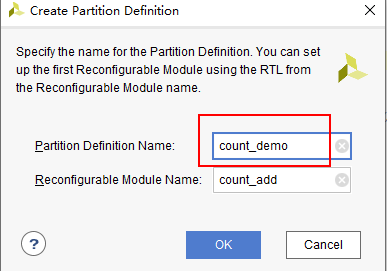

这时我们可以看到该模块的图标发生了变化,变成了黄色的棱形,如下图所示

在这里插入图片描述

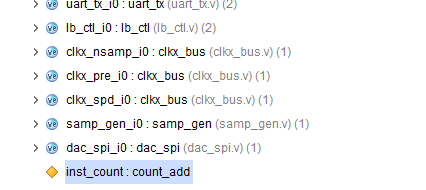

在这一步我们需要提醒一下,通常我们需要进行PR的模块都是比较复杂的模块,里面很可能会包含IP Core,那样的话我们就不能直接这样操作,比如我们要对该工程中的clk_gen_i0模块进行PR,可以看到,这个模块中包含了clk_core_i0这个IP

在这里插入图片描述

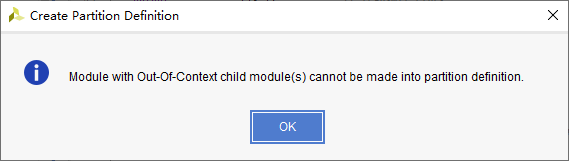

当我们在clk_gen_i0这个模块上右键选择Create Partition Definition时,会提示下面的对话框:

module with out-of-context child module cannot be made into partition definition

在这里插入图片描述

这个意思是包含有ooc子模块的模块,是不能做成partiton的,Vivado中所有的IP Core都是ooc的模块,因此我们需要把clk_gen_i0这个模块导出成dcp后再使用,具体可以参考我的另一篇文章

Vivado中模块封装成edif和dcp

简单来讲,就是先将这个模块设为top,综合后导出dcp,使用的tcl脚本是

write_checkpoint-noxdef

有几个需要RM(Reconfiguration Module)的模块,就要综合几次,导出几个dcp文件

我看网上也有的教程是直接对整个工程进行综合,然后单独导出RM模块的dcp,使用下面的tcl

write_checkpoint-cell

这两种导出dcp的方式是有区别的,把整个工程进行综合,每个子模块的接口很有可能会有所改变,可能是名字改了,也可能是增加或减少了一些接口。如果我们的几个RM只是接口相同,功能不同的话,这样带有不同RM模块的工程综合的结果可能不一样。因此推荐将RM模块设为top,综合后导出dcp。

另一点需要注意的是,如果使用了dcp文件,我们也添加一个wrapper.v到工程中,因此dcp文件是不能直接进行Create Partition Definition操作的。

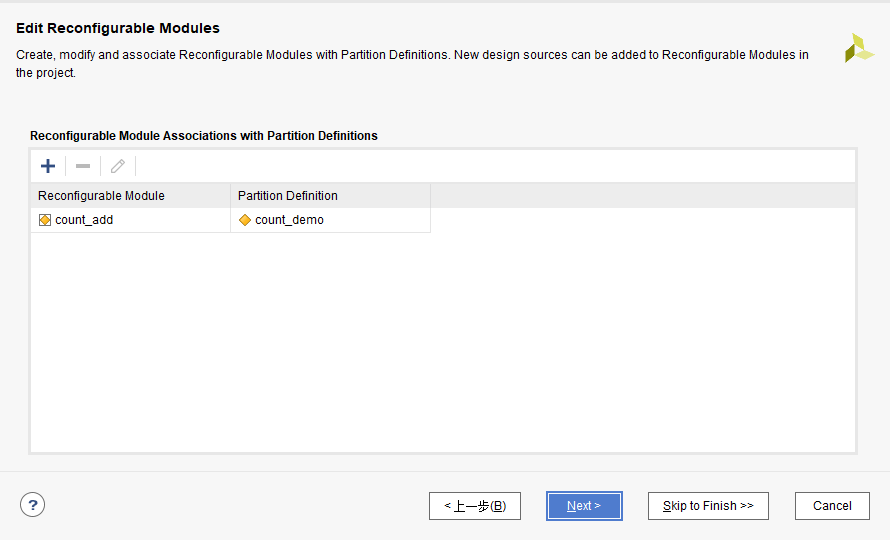

选择左侧导航栏的Partial Reconfiguration Wizard,开始添加RM

在这里插入图片描述

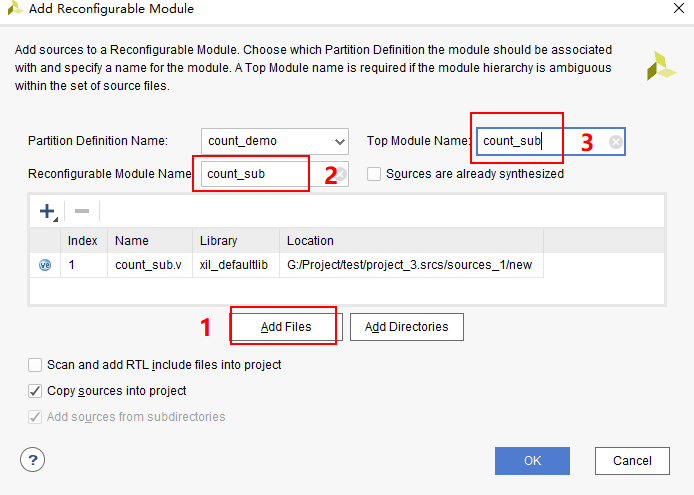

这里,点击+号按钮,出现下面对话框,首先点击Add Files,选择count_sub.v;然后输入Reconfiguration Module Name,由于我们只有一个模块,因此top的name可以不填;如下图,Next

在这里插入图片描述

在这一步如果我们使用dcp文件和wrapper文件的话,需要把它们都添加进来

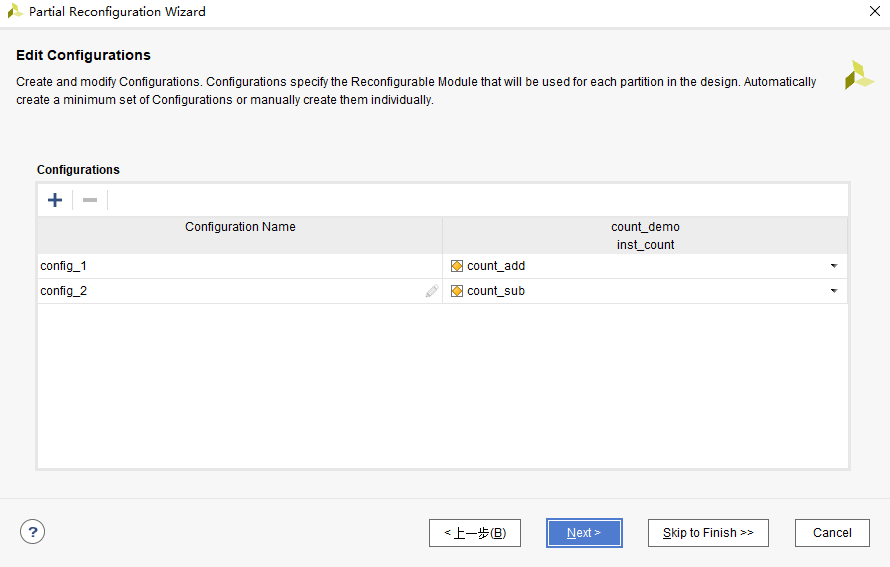

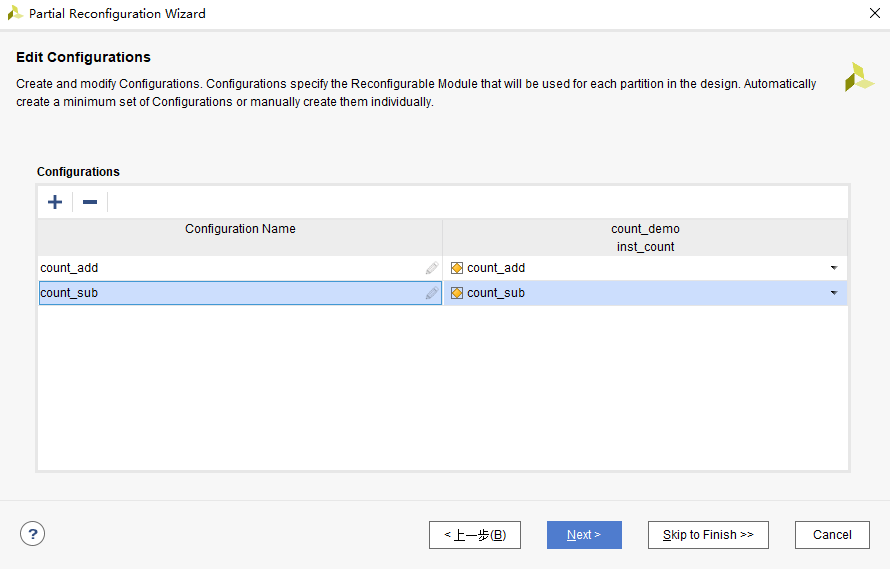

编辑配置,点击automatically create configurations,如果在这个界面没看到这个auto…按钮,就先返回到上一步,再next到这个界面,总会出现的;点击后出现下面的界面:

在这里插入图片描述

我们修改配置的名字如下,next

在这里插入图片描述

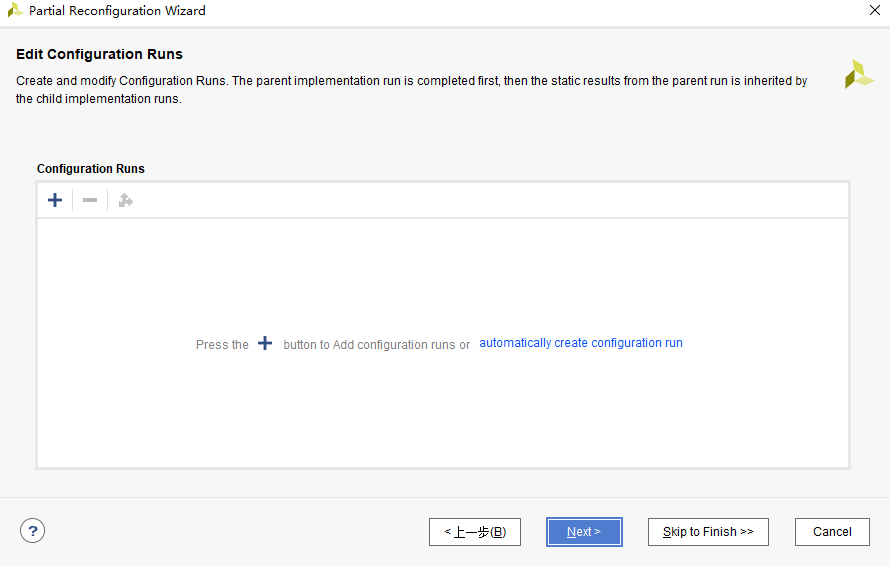

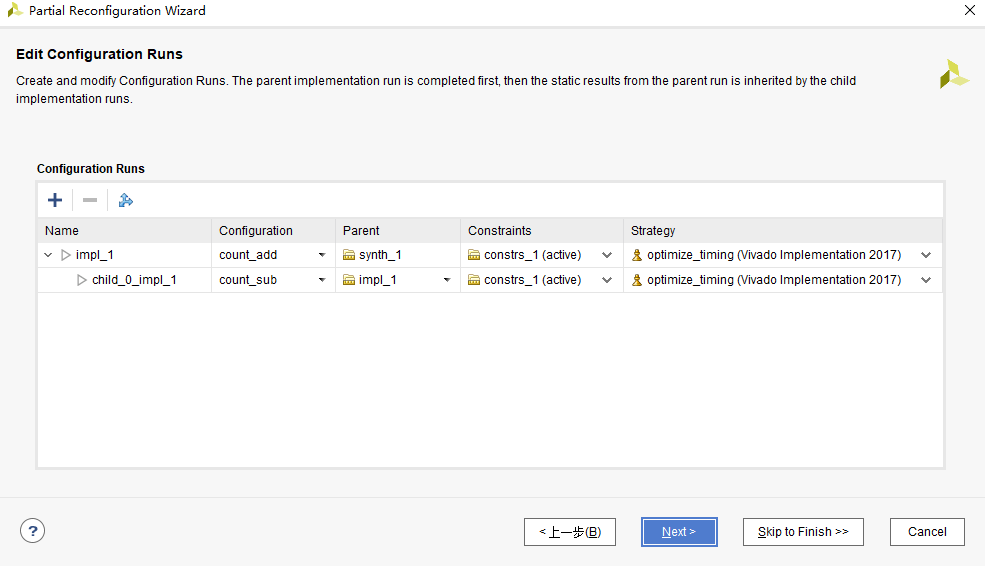

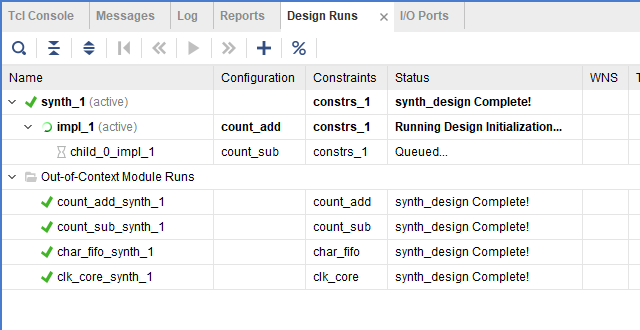

配置runs,也是先点击automatically create configuration run

在这里插入图片描述

在这里插入图片描述

这个图意思是工程中有两个implention runs,第一个叫impl_1,这个里面跑的是包含有count_add模块的程序;第一个叫child_0_impl_1,这个里面跑的是包含count_sub模块的程序。Next到Finish。

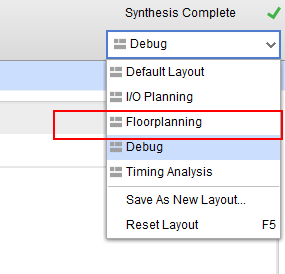

开始综合,完成后点击Open Synthesized Design,并在Vivado右上角,切换到Floorplanning视图

在这里插入图片描述

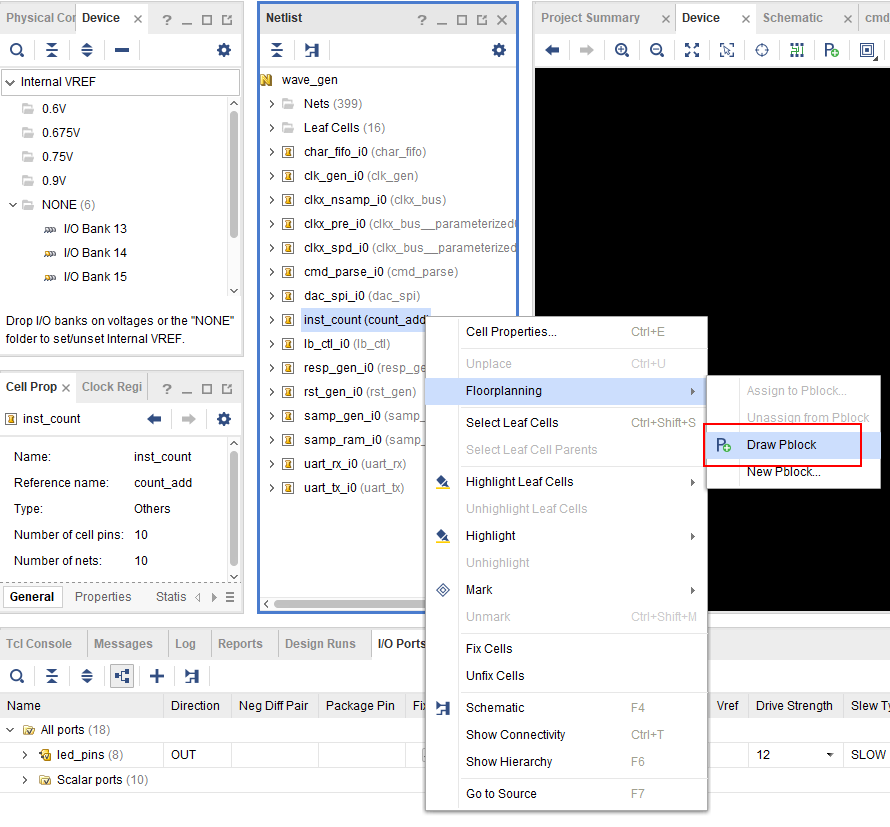

邮件inst_count并点击Draw Pblock

在这里插入图片描述

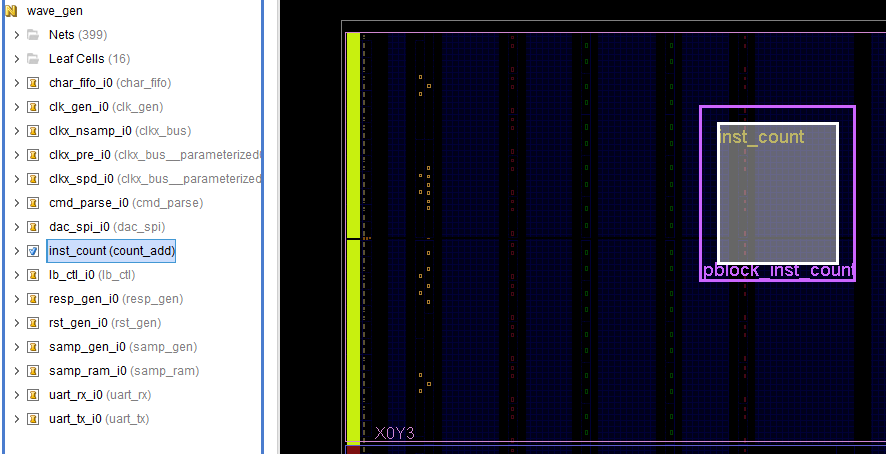

选择一个区域作为Pblock

在这里插入图片描述

绘制Pblock是有讲究的,其中最简单的两个规则就是:

Pblock区域中包含的资源能可以覆盖我们模块需要的资源

不能与其他的Pblock冲突

当然,还有很多其他的规则,这里就不一一介绍了,如果Pblock没画好,很可能导致后面的DRC和Implementation不过。

关于该更多Pblock的说明,可以参考UG909手册UG909

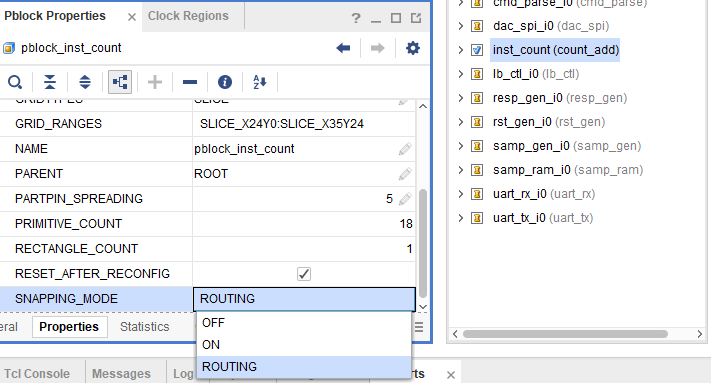

选中框之后,改一下框的属性,将RESET_AFTER_RECONFIG的勾选中,意思是重新配置后,会复位这个Pblock里面的内容;再将SNAPPING_MODE改为Routing(或者设为On),意思是如果我们的边界选的不太好,Vivado会自动处理,选off的话,就是完全按照我们指定的边界。

在这里插入图片描述

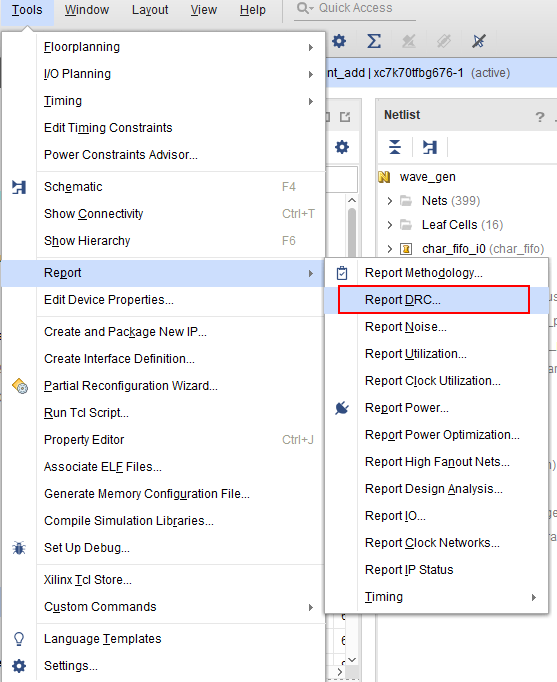

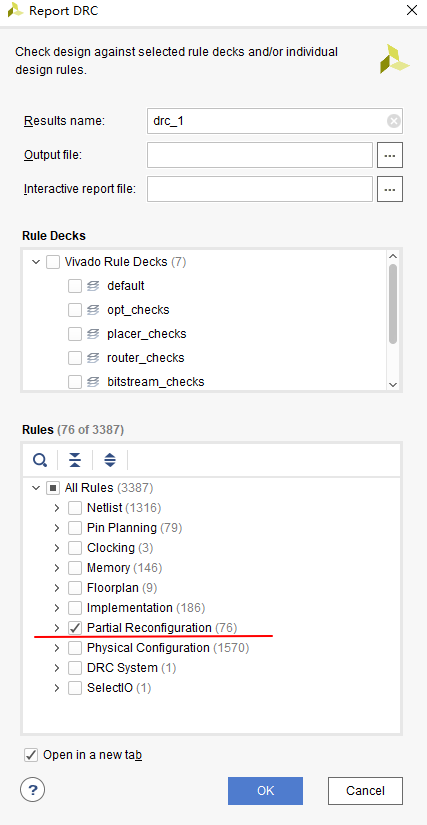

点击Tools->Report->Report DRC

在这里插入图片描述

只选择PR即可

在这里插入图片描述

如果提示No Violations Found,则说明上面的操作过程没有问题。

Run Implementation,可以看到有两个runs需要进行

补充小知识:Vivado中jobs和threads的区别?选择多个jobs能加快实现速度么?

在这里插入图片描述

Generate Bitstream,OK

在这一步进行前,Vivado会自动执行pr_verify,并生成

对于7系列的FPGA,会在impl_1文件夹下生成两个bit文件:

wave_gen.bit和inst_count_count_add_partial.bit,第一个bit文件是整个工程且包含count_add模块的bit文件,第二个bit文件是当我们需要进行Partial Reconfiguration的时候需要下载的bit文件;在child_0_impl_1文件夹下会生成一个bit文件inst_count_count_sub_partial.bit,是当我们需要进行Partial Reconfiguration的时候需要下载的bit文件。

对于UltraScale系列的FPGA,会在生成*_partial.bit的同时多出来一个*_partial_clear.bit,意思是在进行Partial Reconfiguration的时候,先下载*_partial_clear.bit把那一部分的内容先清空,再下载*_partial.bit进行配置。

使用Project模式的好处就是比较简单,敲的指令也比较少,如果是Non-Project模式,在这中间还需要很多操作,虽然麻烦,但对我们理解它的工作模块很有帮助,有兴趣的同学可以再用Non-Project模式下操作一遍。

文章出处:【微信公众号:OpenFPGA】

责任编辑:gt

-

FPGA

+关注

关注

1664文章

22508浏览量

639427 -

计数器

+关注

关注

32文章

2321浏览量

98578

原文标题:Xilinx FPGA Partial Reconfiguration 部分重配置 详细教程

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Atmel AT17LVxxxA FPGA配置EEPROM:特性、应用与技术解析

探索Atmel AT17LV系列FPGA配置EEPROM:特性、应用与设计要点

Atmel AT17LV系列FPGA配置EEPROM的全面解析

Labview接口(interface)的工作过程

线束接头气密性检漏设备的操作流程-岳信仪器

FPGA的图像采集过程

对浮点指令扩展中部分问题的解决与分享

硅片超声波清洗机操作过程中常见问题及解决办法

车载摄像头气密性检测仪操作常见问题及解决办法-岳信仪器

有哪些方法可以避免在电能质量在线监测装置硬件故障检测过程中对设备造成二次损坏?

操作误区警示:发动机气密性检测仪新手易犯错误-岳信仪器

一文详解xilinx 7系列FPGA配置技巧

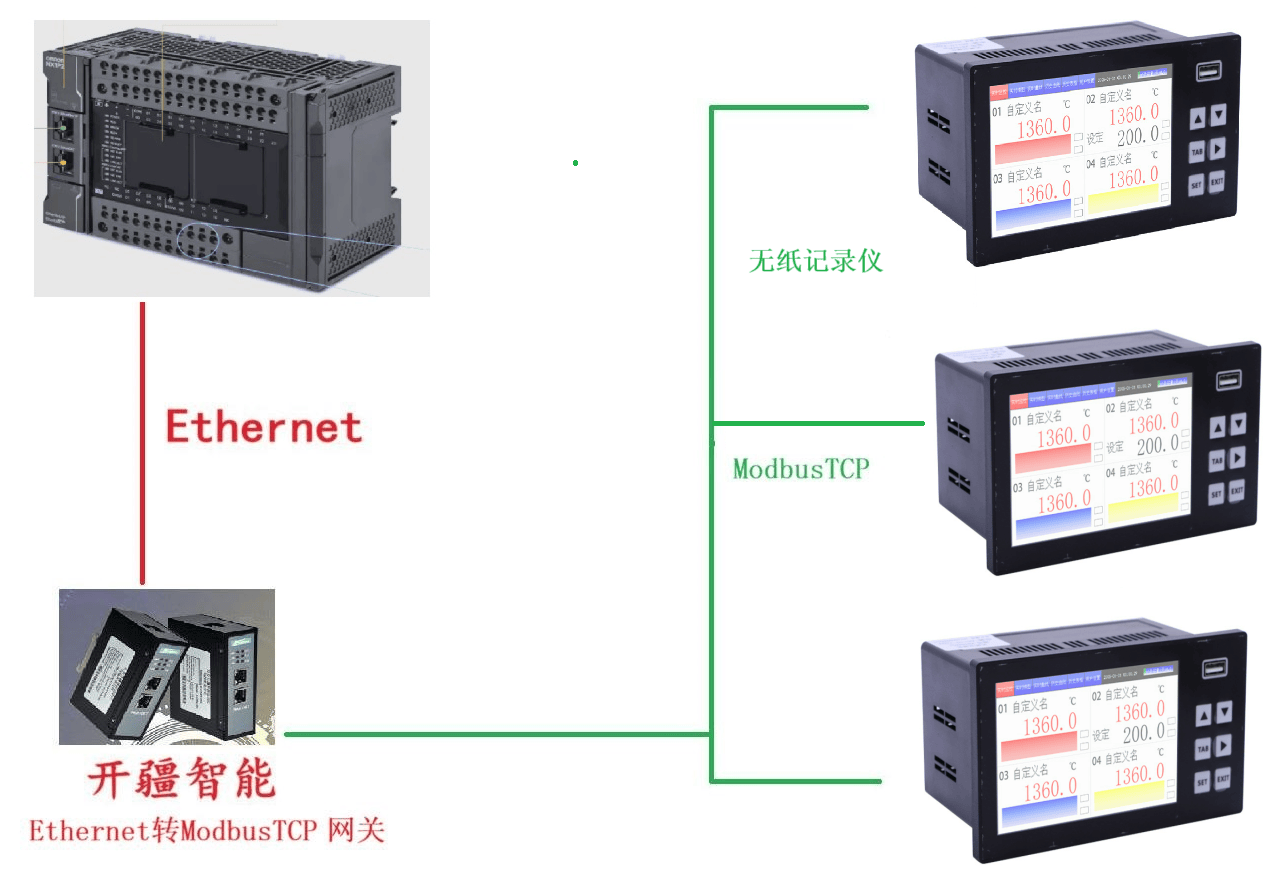

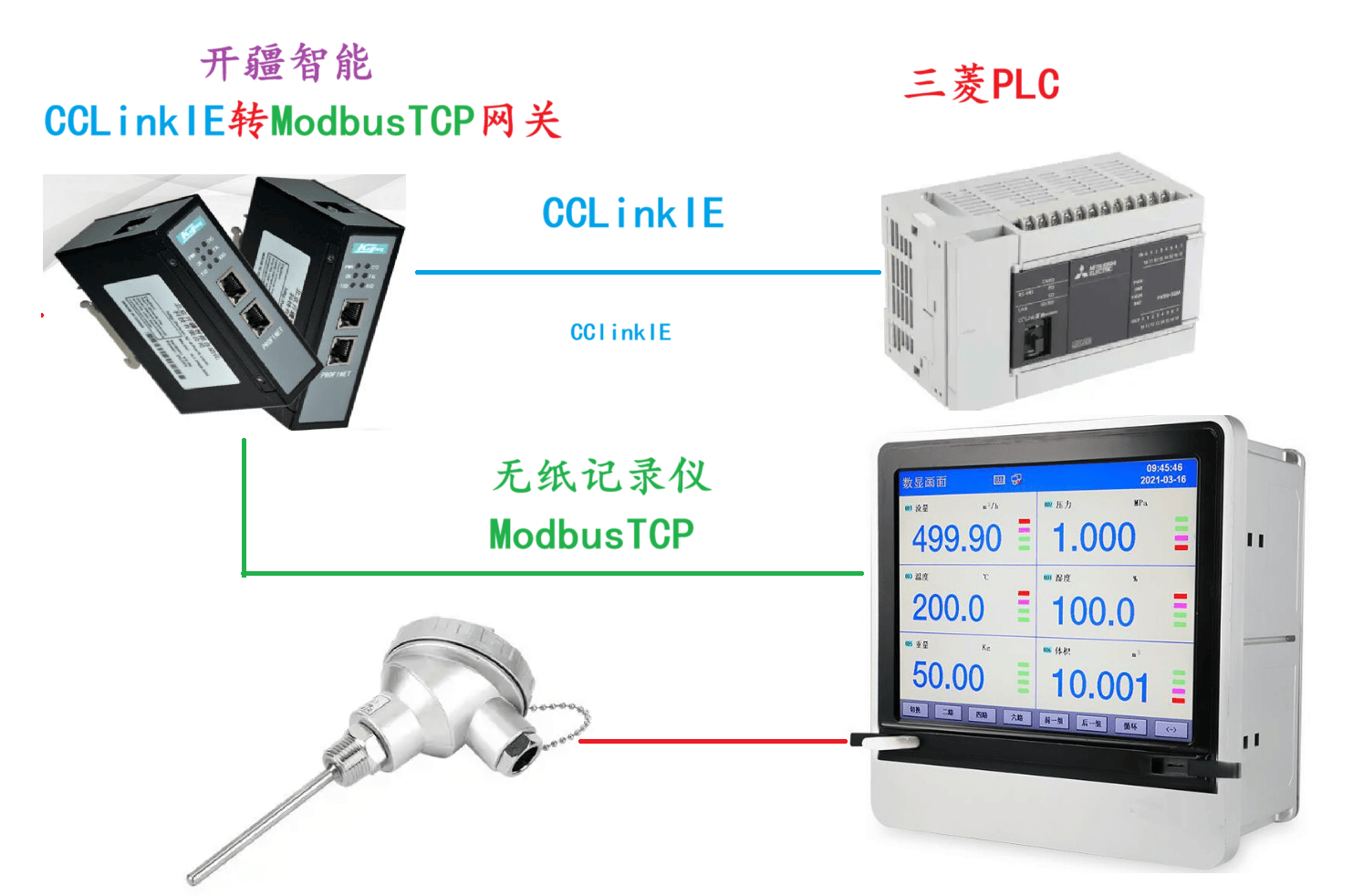

开疆智能Ethernet转ModbusTCP网关连接测联无纸记录仪配置案例

如何在CentOS系统中部署ELK日志分析系统

FPGA应用中部分重配置的操作过程

FPGA应用中部分重配置的操作过程

评论