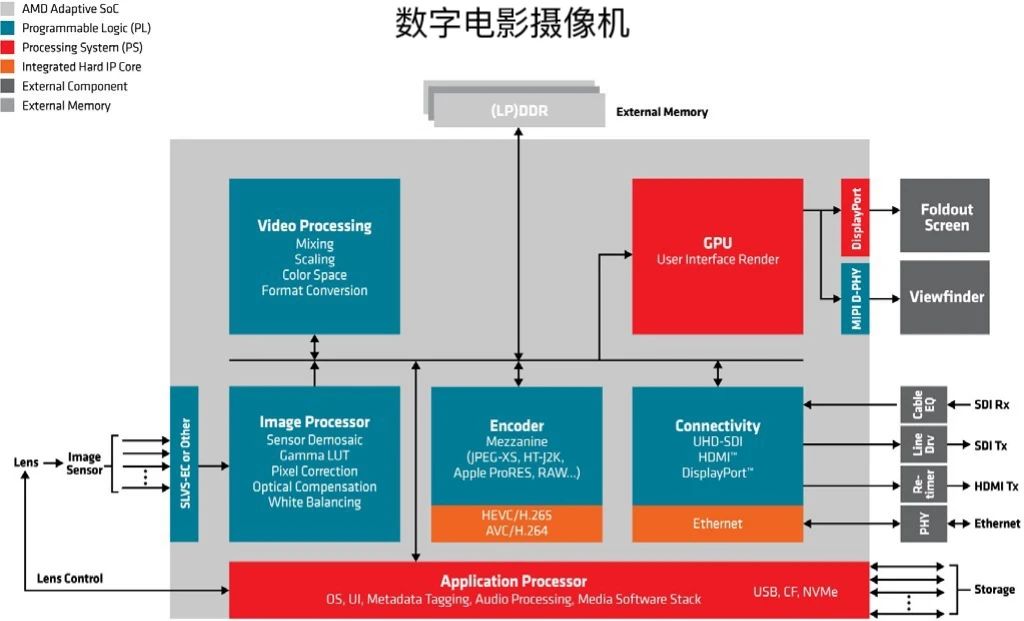

2021 年 7 月 15 日,中国北京 —— 赛灵思公司(Xilinx, Inc.,(NASDAQ: XLNX))今日宣布推出 Versal™ HBM 自适应计算加速平台( ACAP ),这是 Versal™ 产品组合的最新产品系列。Versal HBM ACAP 在单个平台上融合了高速存储器、安全连接和灵活应变的计算。该系列集成了最先进的 HBM2e DRAM,可提供 820GB/s 吞吐量和 32GB 容量,与 DDR5 1相比存储器带宽提高 8 倍、功耗降低 63%。Versal HBM 系列在架构上能够满足数据中心、有线网络、测试与测量领域中计算最密集、内存受限应用的更高存储需求。

图:赛灵思全新Versal™ HBM 自适应计算加速平台( ACAP )系列

赛灵思产品管理与营销高级总监 Sumit Shah 表示:“众多实时高性能应用正面临存储器带宽不足的严重瓶颈,并且只能在其功耗和耐热能力极限下运行。Versal HBM 系列能够消除这些瓶颈,为客户提供优质解决方案,既助力数据中心和网络运营商显著提升性能,又能降低系统功耗、时延、外形尺寸和总拥有成本。”

高带宽与安全连接

Versal HBM 器件在 Versal Premium 系列的基础上构建,集成了功耗优化型网络内核,从而实现高带宽与安全连接。Versal HBM 系列通过112Gb/s PAM4 收发器提供了 5.6Tb/s 串行带宽、2.4Tb/s 可扩展以太网带宽、1.2Tb/s 线速加密吞吐量、600Gb/s Interlaken 连接,以及内置 DMA 的1.5Tb/s PCIe®Gen5 带宽,同时支持 CCIX 和 CXL。这套广泛的硬化 IP 为各种协议、数据速率和光传输标准提供了现成的多太比特( multi-terabit )网络连接,实现了最佳功耗与性能水平以及最快的上市时间。

灵活应变的计算

作为一款自适应异构计算平台,Versal HBM 系列旨在加速广泛的具备大型数据集的工作负载,其集成了用于实现低时延硬件并行处理的自适应引擎、用于 AI 推断和信号处理的 DSP 引擎,以及用于嵌入式计算、平台管理、安全启动和配置的标量引擎。不同于固定功能加速器,Versal HBM 能在几毫秒内动态重新配置硬件,以灵活适应不断演进的算法和新兴协议,进而避免对硬件进行重新设计和重新部署。

图:Versal HBM 系列在单个平台上融合了高速存储器、安全连接和灵活应变的计算

改造网络与数据中心

灵活应变的计算与高带宽存储器和多太比特连接的融合,使得下一代云加速和安全互联成为现实。Versal HBM ACAP 为大数据工作负载提供了卓越的性能和能效,这些工作负载包括欺诈检测、推荐引擎、数据库加速、数据分析、金融建模,以及用于自然语言处理( NLP )的深度学习。Versal HBM 将运行时间较之现代服务器级 CPU 提升了几个数量级,同时还支持大 4 倍的数据集2,因此,用户能够以数量少得多和成本低得多的服务器来部署具备大规模互联数据集的应用。

同样,Versal HBM ACAP系列还能为 800G 路由器、交换机和安全应用提供网络可扩展性和优异性能。利用传统网络处理器( NPU )实现下一代 800G 防火墙通常需要多个 NPU 器件和 DDR 模块,而单个 Versal HBM ACAP 就可以消除对外部存储器的需要,并能以显著降低的功耗和极小的外形尺寸,执行数据包处理、安全处理和灵活应变的 AI 使能异常检测。Versal HBM 系列令客户可以使用更少的器件和系统实现其应用,因而为云和网络提供商大幅节省了资本支出( CapEX )和运营成本( OpEX )。

Versal HBM ACAP 系列适用于硬件与软件开发者,并为任意开发者提供了设计入门通道,包括面向硬件开发者的 Vivado® 设计套件、面向软件开发者的 Vitis™ 统一软件平台,以及面向数据科学家且具备特定领域框架与加速库的 Vitis AI。

供货情况

Versal HBM 系列以业经量产验证的 7nm Versal 器件为基础构建。开发者可以开始在 Versal Premium 系列器件和评估板上制作原型,并轻松迁移到 Versal HBM 系列上。Versal HBM 系列将从 2022 年上半年开始提供样品。相关技术文档现已提供,工具将于 2021 年下半年通过早期试用计划提供。

-

赛灵思

+关注

关注

32文章

1794浏览量

131243 -

大数据

+关注

关注

64文章

8882浏览量

137389 -

加速平台

+关注

关注

0文章

1浏览量

1188

发布评论请先 登录

相关推荐

AMD推出第二代Versal Premium系列

AMD Alveo V80计算加速器网络研讨会

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

第二代AMD Versal Prime系列自适应SoC的亮点

ALINX受邀参加AMD自适应计算峰会

PMP22165.1-适用于 Xilinx 通用自适应计算加速平台 (ACAP) 的电源 PCB layout 设计

在Vivado中构建AMD Versal可扩展嵌入式平台示例设计流程

AMD Versal AI Edge自适应计算加速平台之PL LED实验(3)

AMD Versal AI Edge自适应计算加速平台PL LED实验(3)

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal AI Edge自适应计算加速平台之Versal介绍(2)

赛灵思推出Versal HBM自适应计算加速平台,应对网络与云端大数据的双重挑战

赛灵思推出Versal HBM自适应计算加速平台,应对网络与云端大数据的双重挑战

评论