1 APB介绍

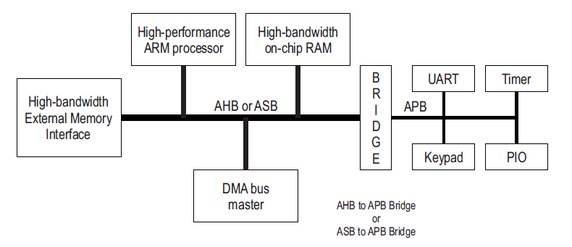

高级外设总线 (APB) 是高级微控制器总线架构 (AMBA) 协议系列的一部分。它定义了一个低成本接口,该接口针对最低功耗和降低的接口复杂性进行了优化。APB 协议不是流水线的,使用它连接到不需要 AXI 协议高性能的低带宽外设。

APB 协议将信号转换与时钟的上升沿相关联,以简化将 APB 外设集成到任何设计流程中的过程。每次传输至少需要两个周期。APB 可能相连的接口:

• AMBA 高级高性能总线 (AHB)

• AMBA 高级高性能总线精简版 (AHB-Lite)

• AMBA 高级可扩展接口 (AXI)

• AMBA 高级可扩展接口精简版 (AXI4-Lite)

可以使用它来访问外围设备的可编程控制寄存器。APB 版本:

• AMBA 2 APB Specification

• AMBA 3 APB Protocol Specification v1.0

• AMBA APB Protocol Specification v2.0

2 信号描述

3 操作状态机

IDLE: 这是 APB 的默认状态。

SETUP: 当需要传输时,总线进入 SETUP 状态,此时相应的选择信号 PSELx 被置位。 总线只在一个时钟周期内保持在 SETUP 状态,并且总是在时钟的下一个上升沿移动到 ACCESS 状态。

ACCESS: 使能信号 PENABLE 在 ACCESS 状态下有效。 地址、写、选择和写数据信号在从 SETUP 到 ACCESS 状态的转换期间必须保持稳定。

退出 ACCESS 状态由从机的 PREADY 信号控制:

• 如果从机将 PREADY 保持为低电平,则外围总线保持在 ACCESS 状态。

• 如果 PREADY 被从器件驱动为高电平,则退出 ACCESS 状态,如果不需要更多传输,则总线返回 IDLE 状态。或者,如果另一个传输紧随其后,则总线直接移动到 SETUP 状态。

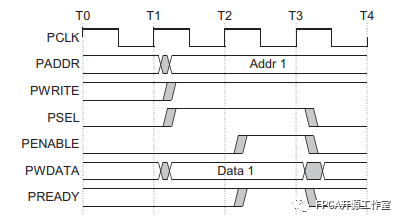

4 APB写操作

时序分析:

在 T1,写传输开始地址 PADDR、写数据 PWDATA、写信号 PWRITE 和选择信号 PSEL 开始,在 PCLK 的上升沿寄存。这称为写传输的建立阶段。

在 T2,使能信号 PENABLE 和就绪信号 PREADY 在 PCLK 的上升沿寄存。

置位时,PENABLE 指示传输的访问阶段的开始。

置位时,PREADY 表示从机可以在下一个上升沿完成传输 PCLK 的边缘。

地址 PADDR、写数据 PWDATA 和控制信号都保持有效,直到传输在 T3 完成,即访问阶段结束。

使能信号 PENABLE 在传输结束时无效。选择信号 PSEL 也被置为无效,除非在传输之后紧接着另一个传输到同一外设。

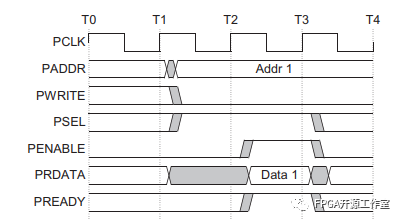

5 APB读操作

时序分析:

从图中可发现除了PWRITE信号是倒过来有效外,APB 读操作时序图和APB写操作时序图非常相似,在这里不再作详细的解释。要特别注意的是,在 T3 后,也就是在进入ACESS周期后,APB Slave必须要将 Master 所要读取的数据准备好,以便 Master 可以在 ACESS 周期末被 T4 正时钟沿触发时正确的将数据读取。

编辑:jq

-

AMBA APB总线

+关注

关注

0文章

3浏览量

1082

原文标题:AMBA-APB总线介绍

文章出处:【微信号:leezym0317,微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AMBA AXI4接口协议概述

usb主机控制器位于ahp总线上吗

AMBA总线协议的基本原理和应用场景

浅述园区智慧用电管理系统的设计与应用

Arm和新思科技继续就AMBA协议系列的最新扩展密切合作

新思科技为AMBA CHI-G协议量身定制一系列AMBA协议解决方案

STM32F030时钟没有APB2, 为什么库函数会有RCC_APB2PeriphClockCmd ?

请问DMA总线访问APB外设和SRAM1,CPU操作CCM RAM,这个是同时进行的还是分时复用的呢?

聊聊AMBA协议的evolution过程

SOC设计中APB协议总线的工作原理

漫谈AMBA总线-AXI4协议的基本介绍

AMBA总线中APB slave设计介绍

AMBA总线中APB interconnect的介绍

浅述AMBA-APB总线

浅述AMBA-APB总线

评论