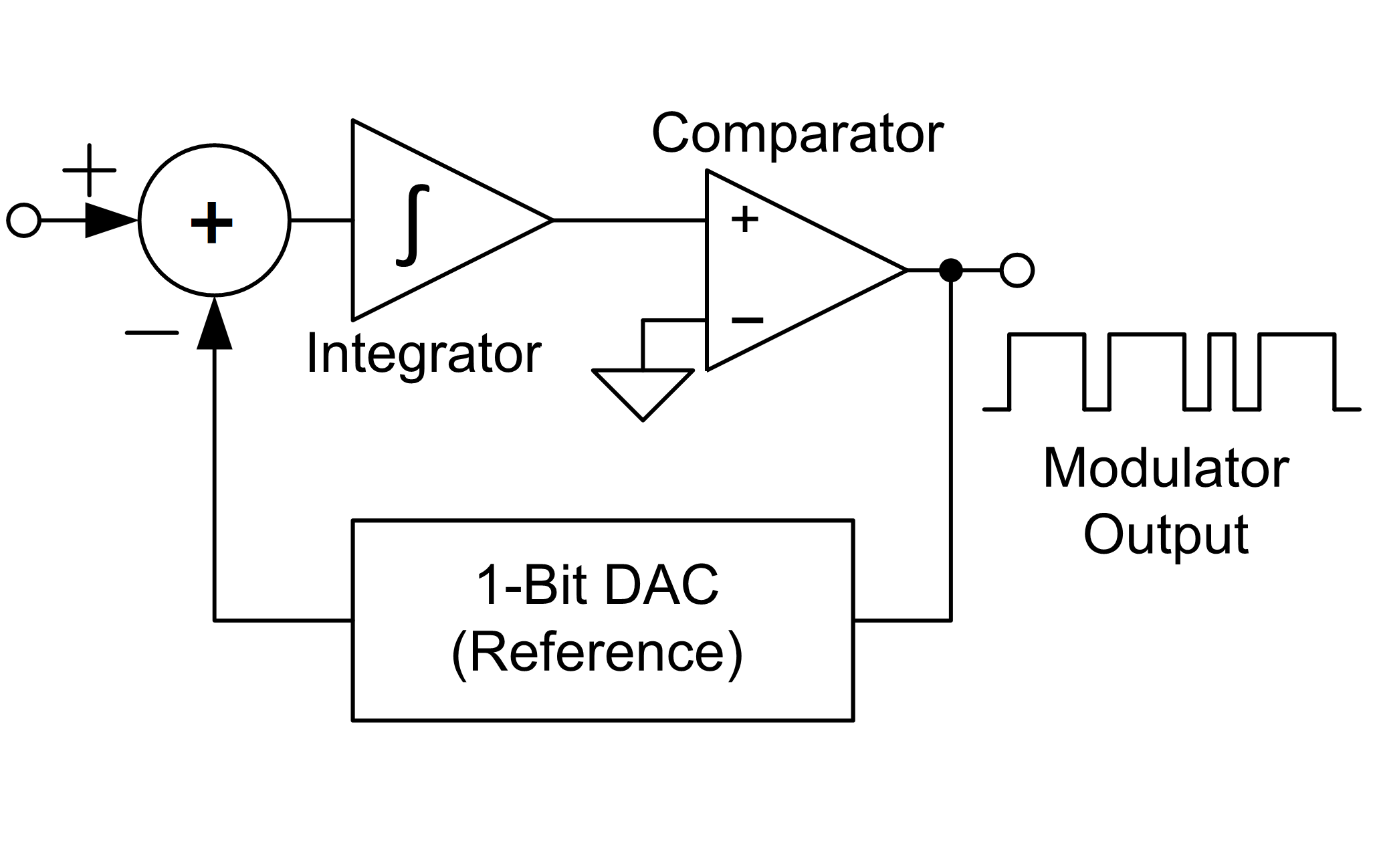

一阶 sigma-delta 调制器类似于 PWM,但如果需要对其进行滤波,则具有更好的频率响应,因为它具有更高的频率输出内容。

创建一阶 sigma-delta 调制器的最简单方法是使用硬件累加器……每次累加器溢出时,输出“1”。否则输出’0’。这在 FPGA 中很容易完成。

module PWM3( clk, rst_n, PWM_in, PWM_out);input clk;input rst_n;input [3:0] PWM_in;output PWM_out;

reg [4:0] PWM_accumulator;always @(posedge clk or negedge rst_n) if(!rst_n) PWM_accumulator 《=0; else PWM_accumulator 《= PWM_accumulator[3:0] + PWM_in;

assign PWM_out = PWM_accumulator[4];endmodule

输入值越高,累加器溢出越快(“ PWM _ 累加器[4]”) ,输出“1”的频率越高。

编辑:jq

-

Verilog

+关注

关注

28文章

1352浏览量

110511

原文标题:Verilog实现一阶sigma_delta DAC

文章出处:【微信号:leezym0317,微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

有没有采用sigma-delta原理的AD芯片推荐

对于1位量化的Sigma-delta调制器来说,As和SNR和DR分别是什么关系?

想做一个采集设备,请问选用什么样的ADC和DAC合适?

【「从算法到电路—数字芯片算法的电路实现」阅读体验】+第九章sigma delta adc阅读与分享

关于使用Delta-Sigma ADS1278遇到的疑问求解答

请问AIC3206的一阶滤波的频率到底该怎么计算呢?

delta-sigma DAC的过采样率是如何确定的?

使用精密Delta-Sigma ADC进行RTD断线检测

Verilog如何实现一阶sigma_delta DAC

Verilog如何实现一阶sigma_delta DAC

评论