3 ModelSim工程实战之自动仿真说完了 ModelSim 的使用流程,接下来我们将会对每个流程进行详细的操作演示,一步步、手把手带领大家学习使用 ModelSim 软件。首先我们讲解的 ModelSim 自动仿真,所谓自动仿真,其实是在 Quartus II 中调用 ModelSim 软件来进行仿真。

在调用过程中,Quartus II 会帮我们完成 ModelSim 中的所有操作,我们只需要分析最后的仿真结果。下面我们就以上章节中我们创建的 Quartus II 软件工程为例,进行仿真。3.1 检查 EDA 路径首先我们打开之前的 Quartus II 工程

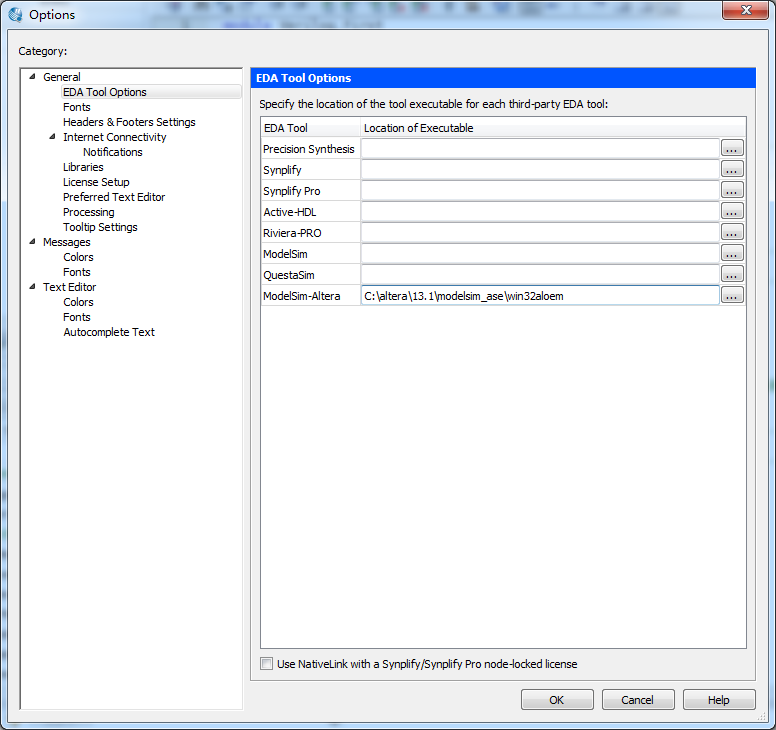

在该页面中,我们在菜单栏中找到【Tool】→【Options】按钮并打开,在打开的页面左侧,我们找到“EDA Tool Options”点击,如图

在该页面中,如果你安装的是 ModelSim 软件,那么你需要在 ModelSim 路径中进行设置,这里我们使用的 ModelSim-Altera , 所 以 我 们 将 ModelSim-Altera 路 径 设 置 成 了C:altera13.1modelsim_asewin32aloem。这里需要大家注意的是一定要选择 modelsim_ase文件夹中的 win32aloem。

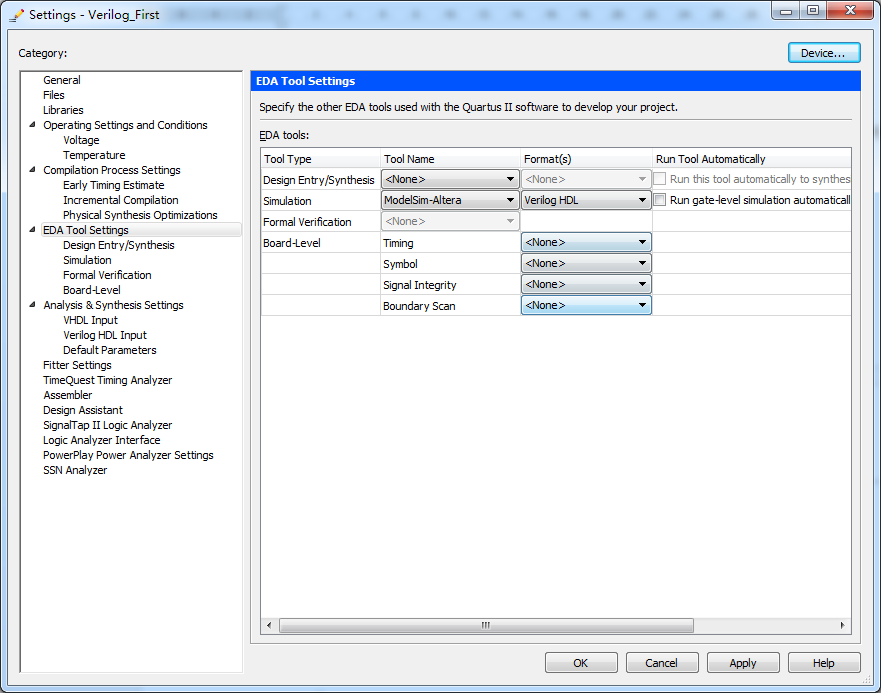

不要选择 modelsim_ae 文件夹中的 win32aloem。还记得我们前面说的么?ae 是收费版本,我们是不能使用的,这里的 ase 免费版本也是可以满足我们的设计的。路径设置完成以后,我们点击【OK】返回我们的 Quartus II 软件界面。3.2 选择 EDA 工具我们在 Quartus II 软件页面的菜单栏中,我们找到【Assignments】→【Settings】按钮并打开,在打开的页面左侧我们找到“EDA Tool Settings”点击,如图

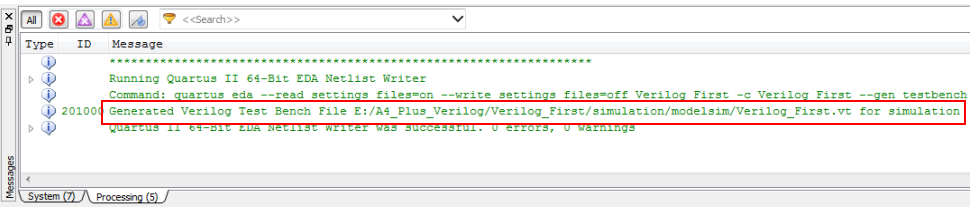

还记得我们之前创建工程的时候,由于在 Quartus II 软件中我们没有用到仿真,所以我们将这里设置成了“None”,现在我们需要用到仿真工具了,我们需要在这里将 Simulation 设置成“ModelSim-Altera、Verilog HDL”。设置完成之后,我们点击【OK】返回 Quartus II 软件页 面中。3.3 编写仿真文件我们在 Quartus II 软件页面的菜单栏中,我们找到【Processing】→【Start】→【Start TestBench Template Writer】按钮并点击,这时 Message 窗口中会显示,如图

我们可以从这条信息中知道,Quartus II 软件自动给我们生成了一个 TestBench 模板,我们只需要在这个模板上稍作修改就能直接使用了。我们在工程目录下找到 Verilog_First.vt 文件,我们可以用记事本打开进行修改,也可以使用 Quartus II 软件打开它进行修改,这里我们建议还在 Quartus II 软件中进行修改。我们在 Quartus II 软件的菜单栏中找到【File】→【Open】按钮并打开,在对话框中找到我们的 Verilog 文件

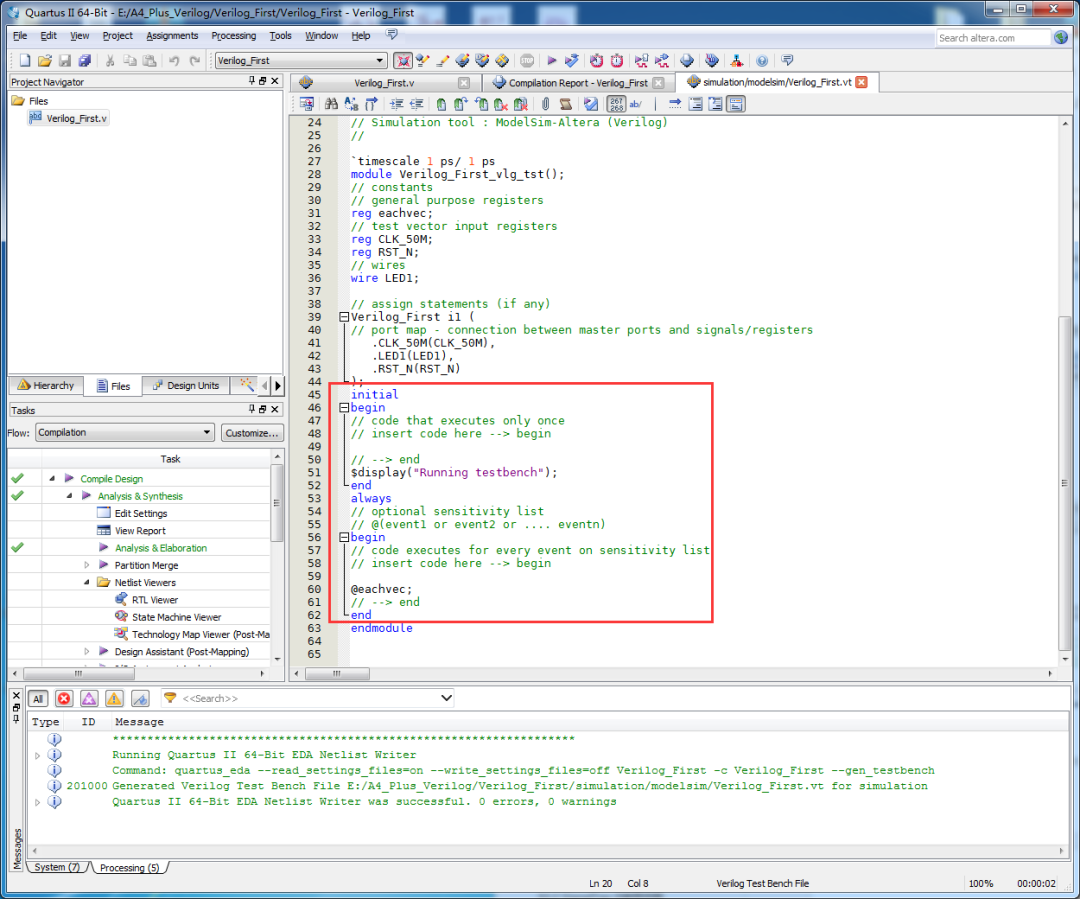

打开之后,如图

在该图中我们可以看到,Quartus II 软件已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个模板里添加我们需要的测试代码(也就是我们常说的激励)。为了让读者能够更好的理解仿真。

这里我们就简单介绍一下 TestBench 源代码:代码的第 1 行,表示仿真的单位时间为 1ps,精度为 1ps。想要进行仿真首先要规定时间单位,我们建议大家最好在 Testbench 里面统一规定时间单位,不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,timescale 是 Verilog 语法中的不可综合语法。

代码的第 2 行就是我们熟悉的部分了,其中第 5 行至第 10 行是我们的数据类型定义,这里我们可以看到 reg eachvec 是一个多余的信号,没有任何作用,我们也可以将它删除,接下来我们再来看第 13 行至第 18 行,这一部分就是一个模块调用,它将我们的 Verilog 模块中的信号连接到我们的 TestBench 模块中。

最后,我们再来看下第 20 行至第 32 行代码,其中第 20 行至第 26 行是信号的初始化,第 28 行至第 31 行是时钟信号的生成。这里我们主要来讲讲#10000,#10000 表示的是延迟 10000ps(即 10ns),具体的延迟单位,还是要看我们的 timescale 是如何设置的。

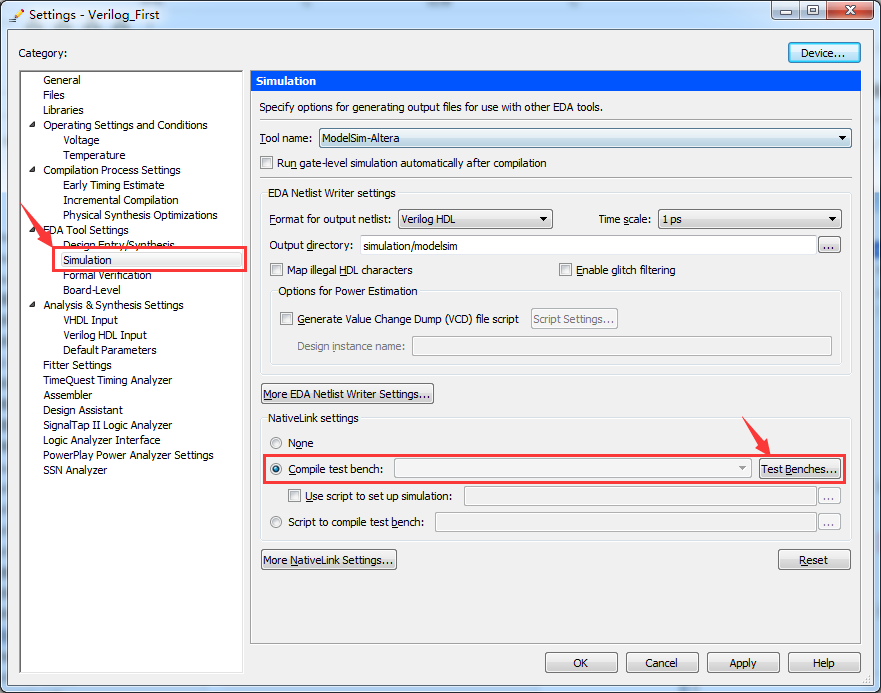

至此,整个代码都介绍完了。3.4 配置仿真功能编写完了仿真文件,接下来我们需要在 Quartus II 软件中配置仿真功能,我们在 Quartus II软件界面的菜单栏找到【Assigement】→【Settings】按钮并打开,在打开的页面中,我们找到左侧的 Simulation 点击,出现如图

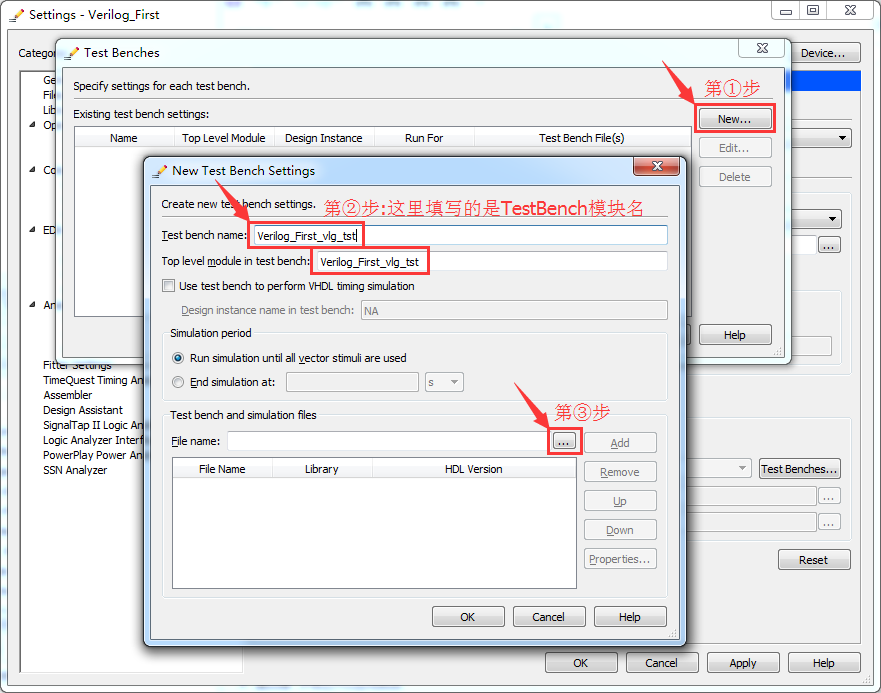

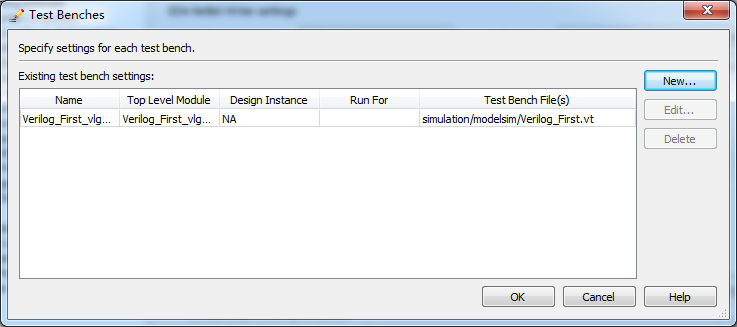

我们选中“Compile Test bench”,然后单击后面的【Test Benches】按钮,则出现如图 2.9所示的“Test Benches”窗口(也就是图中上面的窗口),接着我们单击【New】按钮,则会出现如图 所示的“New Test Bench Settings”窗口(也就是图中下面的窗口)。

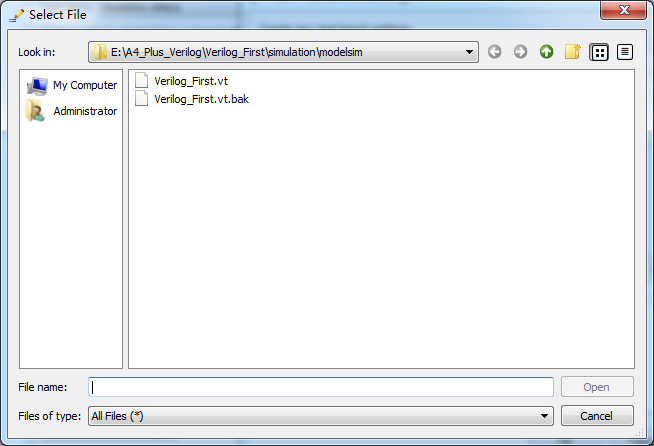

在该页面中,我们将 TestBench 模块名输入到“Test bench name”和 “Top level module in test bench”的编辑栏中。接着我们在“Test bench and simulation files”下拉列表框中添加仿真文件,如图 所示,点击【Open】即可。

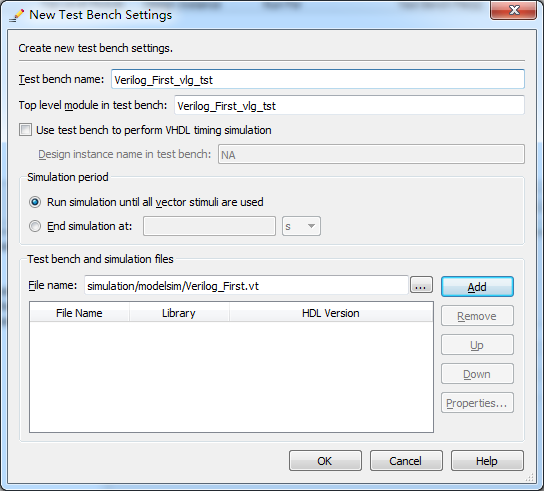

然后单击【Add】 按钮添加到最下面的列表中如图

完成后我们单击【OK】按钮,便可看到如图 2.12 所示的“Test benches”窗口的列表中出现了刚才添加的仿真文件相关信息,至此,我们仿真文件添加完成了,接着我们单击【OK】按钮,返回我们的 Quartus II 软件界面。

3.5 开始功能仿真

万事俱备只欠东风,经过上面这么多的操作步骤,我们终于完成了所有设置,接下来我们就可以进行仿真了,在开始仿真之前,我们这里有一点要需要注意,我们在 Quartus II 软件中实现的功能是 LED 闪烁,它的间隔时间是 1s,如果我们想要仿真这个功能,那么我们仿真软件运行时间最低就是 1s。这 1s 钟在我们看来是很短很短的,不过在仿真软件看来是很长很长的,我们的仿真软件单位可是 ps。

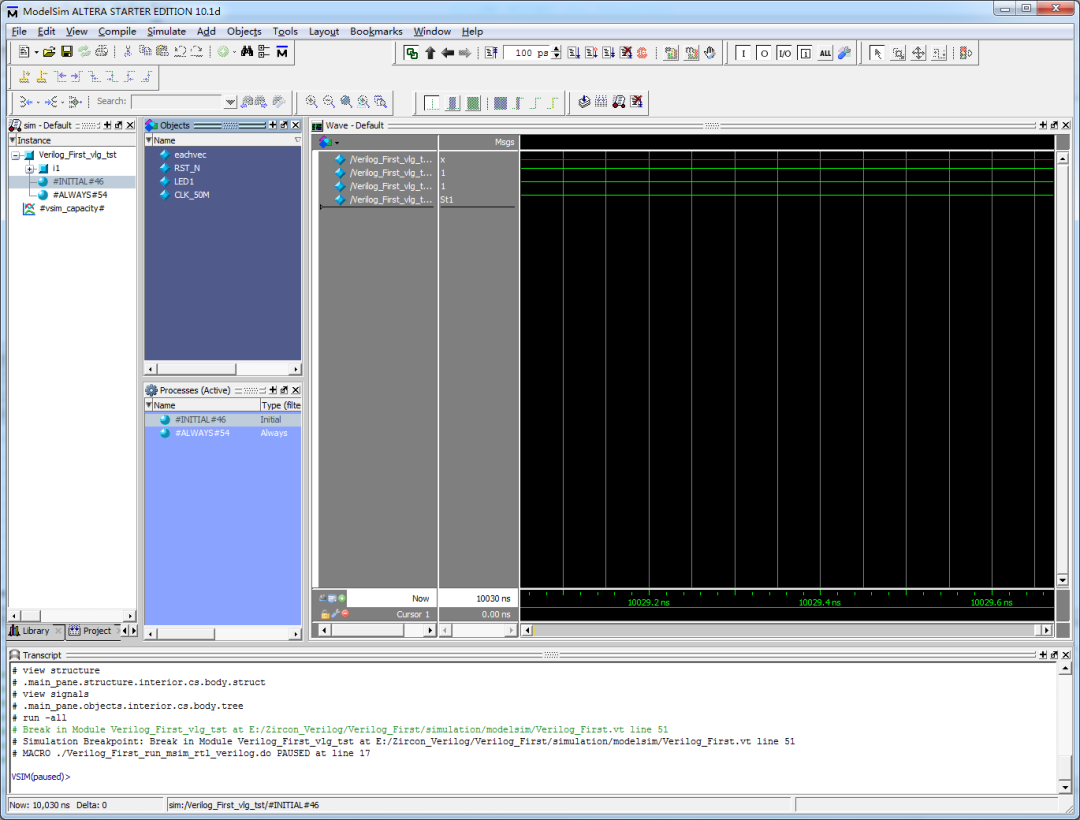

为了便于我们仿真,这里我们需要稍微改动一下 Verilog 代码,我们需要将 parameter SET_TIME_1S = 27‘d50_000_000;修改为 parameter SET_TIME_1S = 27’d50; 也就是将我们原来的 1s 钟修改成了 1us。修改完毕后,我们在 Quartus II 软件界面中的菜单栏中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按钮并点击,则会出现如图 2.13 所示界面。

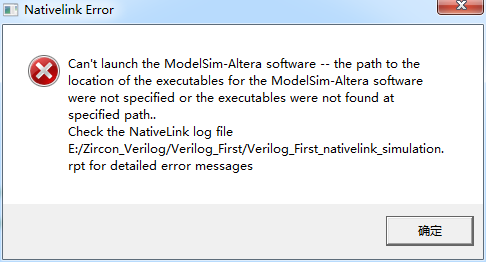

看到这里,也许有的朋友点击【RTL Simulation】并没有出现 Modelsim 仿真窗口界面,而是出现了如图 2.14 所示界面。

出现这种错误主要是因为我们前面设置的 Modelsim 路径不对造成的,如何解决这个问题呢?我们尝试将 ModelSim-Altera 路径设置成了 C:altera13.1modelsim_asewin32aloem。这和我们刚刚设置不同的是,我们在路径的最后面添加了一个反斜杠。

这时,我们再点击【RTL Simulation】按钮就会出现 Modelsim 仿真窗口界面了,这里我们需要说明的是:有的电脑不添加反斜杠是可以运行的,有的电脑不添加反斜杠是不能运行。在 Modelsim 软件启动过程中,我 们不需要任何操作,它会自动完成仿真,并给出我们所需要的波形,当波形图出现之后,我们就可以查看波形来判断设计功能是否正常了。

编辑:jq

-

ModelSim

+关注

关注

5文章

174浏览量

47164

原文标题:ModelSim 使用【二】联合Quarus自动仿真

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

OptiSystem与OptiSPICE的联合使用:收发机电路的眼图分析

自动驾驶联合仿真——功能模型接口FMI(终)

康谋分享 | 自动驾驶联合仿真——功能模型接口FMI(四)

康谋分享 | 自动驾驶联合仿真——功能模型接口FMI(三)

如何在ModelSim中添加Xilinx仿真库

康谋分享 | 自动驾驶联合仿真——功能模型接口FMI(二)

康谋分享 | 自动驾驶联合仿真——功能模型接口FMI(一)

ISE 关联 Modelsim 详细操作

最实用的Modelsim使用教程

最实用的Modelsim使用及仿真的基本步骤

基于ModelSim使用二联合Quarus自动仿真教程

基于ModelSim使用二联合Quarus自动仿真教程

评论