过去,FPGA设计者主要关心时序和面积使用率问题。但随着FPGA不断取代ASSP和ASIC器件,设计者们现正期望能够开发低功耗设计,在设计流程早期就能对功耗进行正确估算,以及管理和对与FPGA相关的各种内部电压及I/O电压排序。

电源管理已成为FPGA设计者的一个重要考虑因素,特别是在设计便携式、电池供电的产品时。通过功率监控设计技术能够减少功耗、增强可靠性、降低生产成本,并减少对电源和冷却的要求。

设计者可能会面临的与FPGA电源相关的主要问题如下:系统级电源要求是什么?将要消耗多少电流?要求多大的电压水平以及上电和断电问题?器件的温度条件如何,在该设计给定的温度环境下器件能否可靠地工作?在电路板上是否需要针对发热器件内置冷却装置?

电源理论

在电子器件中,功率通常被定义为电流做功的量。器件往往将电能转换为热能,但遗憾的是,除非是设计一个加热器或者是电灯泡,否则在大多数应用中热都被认为是无用的。了解FPGA的热动力学原理将有助于设计者选择事半功倍的方法来降低功耗。总功耗是某些类型的低功耗器件以及工艺节点和器件封装特性的函数。

功耗的AC部分(与电路资源相关)是功耗的动态部分。AC功耗与电路资源的工作频率和操作状态,以及电路资源的数量直接成正比。以下等式说明了降低供电电压(最主要的因素)、开关电容、节点的转换频率或信号转换频率是如何影响功耗的。

CMOS FPGA的功耗主要来自两个方面:静态与动态。式中的功耗用焦耳/秒或者瓦特来表示 :

式中各字符的含义为:P-功率(焦耳/秒或瓦特);V-电压(焦耳/库仑或伏特);I-电流(库仑/秒或安培);R-电阻(欧姆);-每个节点的转换频率;C-开关电容;V2DD-电源电压;F-频率(每秒转换的次数)。

PStatic相对于PDynamic的功耗随处理节点而变化。在130纳米和90纳米器件中,静态功耗是总功耗的一小部分。例如,假定一个内部逻辑工作频率50MHz、I/O工作频率250MHz的设计实例,在130纳米FPGA(如LatticeECP或LatticeXP系列)中PStatic约为10%,而在90纳米的LatticeECP2或LatticeXP2中则PStatic约为20%。

动态的转换操作以及负载电容的充/放电消耗了大部分能量,这在很大程度上是由用户设计来决定的。在65纳米和更小的工艺节点上,这一传统会发生变化。

晶体管物理特性在尺寸较小时会发生变化,这使得静态泄漏非常大。由于晶体管泄漏不断增加,静态功耗成指数增长。静态功耗在65纳米处超过动态功耗。莱迪思(Lattice)半导体公司和其它FPGA供应商主要采用改进制造工艺,以及混合使用不同类型晶体管的方法来处理这些问题。

AC功耗与电路资源的工作频率和操作状态,以及电路资源的数量直接成正比。以上PDynamic等式指出了供电电压(最主要的因素)、开关电容、节点的转换频率以及信号转换频率是如何影响功耗的。

随着FPGA工艺的尺寸在缩小,使得设计者从更小的晶体管和IC裸片所带来的功耗减小中获益。但增加的时钟速度和大尺寸设计往往在某种程度上抵消了这些好处。FPGA结构单元的相关功耗在不同的工艺节点之间也会发生变化。

例如,130纳米LatticeECP和90纳米LatticeECP2/M FPGA的各部分电路资源、走线以及LUT、寄存器、嵌入式存储器块(EBR)等逻辑的动态功耗比例进行了比对。这里假定设计中的逻辑部分利用率为90%、PLL/DLL、存储器、DSP等嵌入式ASIC的利用率为100%,采用混合LVCMOS 1.2V和LVDS 2.5V DDR信号标准的I/O的利用率为80%。

虽然90纳米器件中的总功耗可能有所下降,但I/O所占功耗的比例大大增加。对于一个特定的器件系列而言,这将影响采用何种降低功耗的策略。

热管理

热是IC工作时的副产品,必须利用工艺确保FPGA工作在规定的结温范围之内。只要温度不超过指定的环境温度和硅片结温的上限,半导体器件就能正常工作。当超过温度上限时,IC会停止正常工作并将被损坏。在大功率应用或高工作温度下采用IC时,热管理是绝对必要的。

为避免出现可靠性方面的问题,半导体供应商在器件数据表中规定了最大允许结温。设计工程师应对其特定设计进行热分析以便确保器件和封装不超过结温要求。内部数据是相对的,实际值取决于各种因素,例如裸片尺寸、焊盘尺寸、气流、电源,PCB设计及应用本身。

尽管总功耗、环境温度、热阻和气流都对器件的热有影响,但器件数据表中规定的结温(Tj)无疑是最关键的因素。例如带有各种结构块(包括DSP、存储器和SERDES I/O)的LatticeECP2/M,商业级器件允许的结温是0℃至85℃,工业级器件为-40℃至100℃。器件工作在上述范围内时,AC特性能够得到保证。这种器件工艺的结温可靠性限制是125℃。了解供电电压的最大最小值会有助于设计者降低静态功耗。

工作在较高温度下的器件同样意味着有较大的静态电流(SICC)。在给定温度下SICC和总ICC(静态ICC和动态ICC)的差值提供可用动态预算。如果器件运行时的动态ICC高于这一预算,总ICC也比预算值高,则将导致裸片温度上升至超过规定的工作条件。器件的结温受诸多因素的影响,例如功率、环境温度,热阻或气流。减少一个或多个因素会引起变化以减少器件的结温。

当考虑热耗散时,用到了热阻的概念。在IC中,热阻(()表示对于裸片表面耗散的每瓦功率(热)而言,裸片结点的稳态温升超过一个给定的参考值。它的单位是℃/W。最普通的例子是热阻Junction-to-Ambient (JA(℃/W),以及热阻Junction-to-Case (JC(℃/W)。另外一个因素是热阻Junction-to-Board (JB(℃/W)。

除了器件和封装,电路的热特性取决于工作温度、器件功耗以及系统散热能力。器件的最大结温计算如下:

TJ = TA + P * θJA (1)

TJ = TC + P * θJC (2)

TJ = TB + P * JB (3)

式中的TJ、TA、TC和TB分别为结温、环境温度、表面(或封装)温度和电路板温度(℃)。P是器件的总耗散功率。(JA通常用于自然和强制的对流冷却系统。当器件封装具有一个直接安装在PCB板或散热片上的高导电性外壳时,(JC非常有用。(JB则在与器件封装相邻的电路板温度已知的情况下使用。

对于功率(P=Vcc * Icc)因素而言,ICC可通过各个器件数据表的功耗来估算,或者视为功率评估软件的输出。下图列出了各种不同IC封装的热阻((JA和(JC)特性,并展示了某些封装类型的优势以及气流和静止空气环境的对比。

当设计一个系统时,设计者必须确保器件工作在系统环境所规定的温度范围之内。这个问题应在设计系统之前重点考虑。利用FPGA功率评估工具,设计者能够预测器件的发热并估计动态功耗预算。在设计电路板之前估计器件的工作温度还使设计者能够更好地对功率预算和气流进行规划。

管理功耗

对于一个设计者必须解决功耗问题的目标应用,应采用功耗逼近的方法。第一步,设计者应寻找降低功耗的RTL。事半功倍的方法包括目标嵌入式模块、小型FSM的格雷(gray)编码,采用可减小尺寸而对性能影响不大的方式来组织各个模块。如果FPGA是高密度的90纳米器件,则应该对I/O编程和转换进行仔细考虑以节省功率。其次,应该采用可节省功耗的综合、布局和布线优化,例如寄存器再定时和面积优化。最后,可反映实际工作情况的强大测试平台将有助于用功率评估软件创建用于后仿真分析的精确的活动因子和转换速率因子。

有许多设计技术可以帮助降低系统的整体功耗。

减小静态功耗的方法包括:

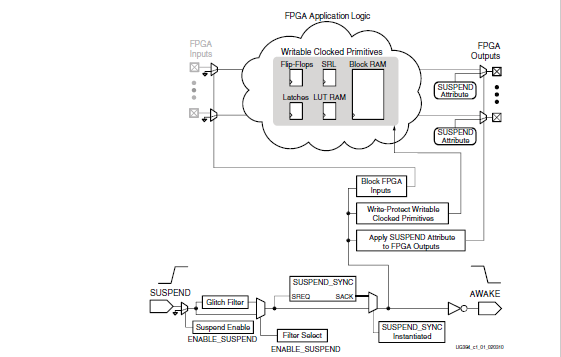

使用睡眠模式(如果提供的话)。例如在系统不工作期间,可以把LatticeXP “C”(VCC= 1.8/2.5/3.3V)器件设置成睡眠模式。睡眠模式期间待机电流可减小1000倍。如果电源处于工作范围内,则无需切换电源。

减小工作电压。采用器件规范中VCC和VCCJ的较低值。

利用以下方法尽可能地减小工作温度:采用较低热阻能更好散热的封装;将散热片和散热层放置在PCB板上器件的周围;采用诸如机械导管和风扇等气流技术。

减小I/O的开关电容和频率。

当睡眠模式时对I/O去耦。如果无法实现的话,关闭内核电压,只留下VCCO。

减小I/O电压摆幅。使I/O驱动尽可能地低。例如,如果驱动3.3V CMOS,可以尝试采用2.5V~3.0V VCCO。这样做会降低抗噪声能力,但对减小功耗十分有益。I/O采用低电压标准。

利用压摆率控制来减小输出开关电流。一些FPGA能提供对LVCMOS或LVTTL输出缓冲器的控制,这些缓冲器能被配置成低噪声性能或者高速性能。

减小动态(AC)的方法:

优化综合资源。减小设计在器件间的跨度。在紧凑型设计中采用较少的布线资源以减少功耗。

用嵌入式ASIC模块。现代FPGA中EBR、DSP和PCS模块在通用LUT/寄存器逻辑上的功耗较低。

采用计数器/FSM模块的信号编码优化。例如,16位二进制计数器平均只有12%的活动因子,7位二进制计数器平均有28%的活动因子。另一方面,7位线性反馈移位寄存器(LFSR)能以50%活动因子进行翻转(即触发),这会导致较高的功耗。由于活动因子小于10%,格雷码计数器在每个时钟边沿仅有一位发生变化,因此耗用的功率最少。

采用优化的时钟频率。由于动态功耗直接与工作频率成正比,这样可以减小功耗。设计者必须确定设计的某部分是否工作在较低时钟速率下,以减少功耗。

采用门控时钟优化。由于时钟信号始终都在转换,会消耗大量功率,所以门控时钟能帮助减少同步寄存器中过多的转换操作。应该将门控时钟列为FPGA布线资源的最高优先级。

时分复用(TDM)类型算法。

同步计数器与异步计数器实现。

FPGA功率评估工具

和仿真类似,FPGA热分析是一种与传统FPGA实现工具并行运作的验证流程。在面向莱迪思FPGA的ispLEVER设计工具流程中,设计者可以在任何阶段评估功耗:即利用功率计算器进行综合前、布线后和仿真后评估。FPGA功率计算软件工具通常可使设计者在三个不同的精确级上估计功耗:

驱动估计,此时手工输入占用的电路资源和转换频率。

Post-PAR,此时面向一个更精确的使用模型引入后布局和布线。

后仿真,此时为获得更精确的活动因子和转换速率模型,导入由HDL仿真器产生的转换频率。

功率计算器采用诸如器件特性、电压、温度、器件参数差异、气流、散热片、使用的资源、活动因子和频率等各种输入参数来计算器件的功耗。计算器求出功耗的静态(DC)和动态(AC)部分,以及预计的结温(TJ)。

在进行综合前,用逻辑块的活动因子和I/O切换率估算切换频率。如果在布局和布线后使用功率计算器,则可以通过本地电路描述(NCD)数据库导入实际的器件利用率。系统采用post-map、 post-place或post-route NCD的结果时,功率计算是最准确的。基于仿真结果含有活动因子和切换率的可选VCD文件将进一步增加精确性。

可从下列方程得出AC功率:

总AC功率(资源)= KRESOURCE * fMAX * AFRESOURCE * NRESOURCE

其中,KRESOURCE是针对资源的功率常数(mW/MHz)。fMAX是运行时的最高频率,用MHz量度频率。

AFRESOURCE是针对资源的活动因子。活动因子为开关频率的百分比。NRESOURCE是设计中所用资源的数目。

活动因子(或AF%)被定义为信号激活或转换输出时的频率(或时间)的百分比。与时钟域相关的大部分资源以与时钟相同的频率百分比运行或转换。功率计算器的使用者可以手工输入参数,或者引入基于模拟结果的活动因子。

可针对每个布线资源、输出或者PFU计算出AF。如果没有模拟结果,那么对于一个占用约30% 到70%器件资源的设计,通常推荐AF%在15% 至25%之间。AP精确性取决于时钟频率、设计的激励信号和最终的输出。

I/O功耗的关键输入参数是I/O转换速率。用户提供的信号(输入情况下)或者作为设计输出(输出情况下)的信号决定了I/O的操作情况。I/O的转换速率定义了它们的操作状况。下列方程定义了输出的转换速率(或者TR),单位用MHz表示。

转换速率(MHz) = 1/2 * fMAX * AF%

本文小结

设计中最关键的因素之一是降低系统的功耗,特别对于手持设备和其它现代电子产品而言。降低功耗的技术多种多样,这取决于目标器件的类型和设计的特性。理解FPGA功耗、静态和动态功耗、内核与I/O资源将影响降低功耗的策略。采用节省功率的设计技术以及估计方法将有助于设计者满足目标器件的工作规范要求。

编辑:jq

-

FPGA

+关注

关注

1629文章

21736浏览量

603235

原文标题:FPGA设计中的电源管理

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

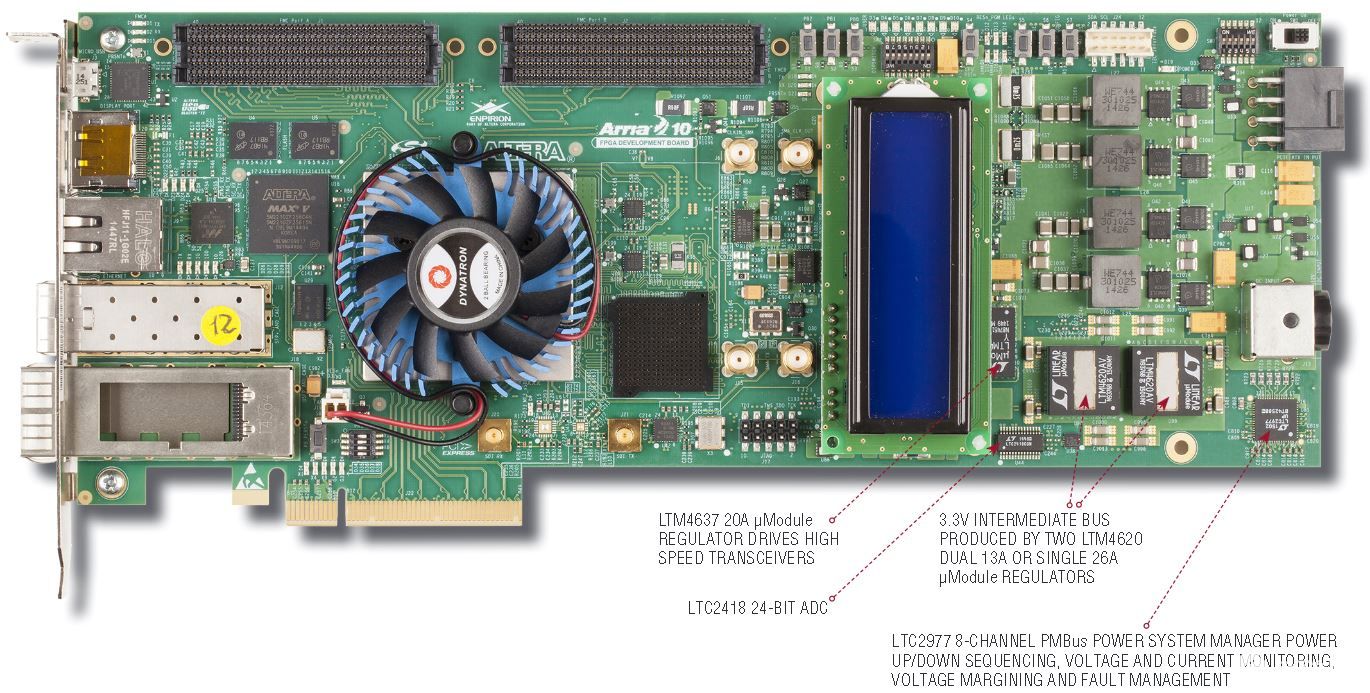

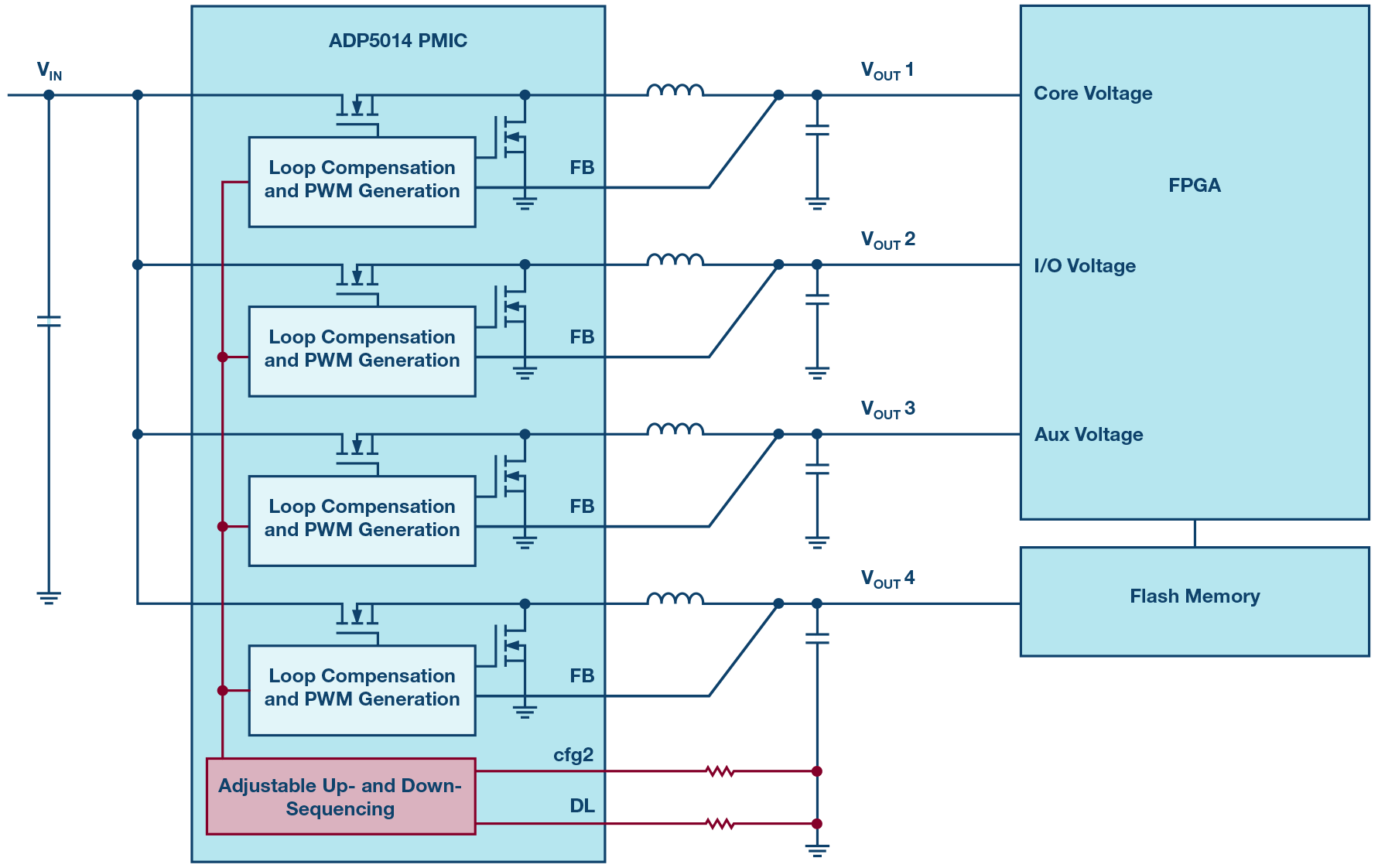

基于FPGA应用设计优秀电源管理解决方案

适用于FPGA、GPU和ASIC系统的电源管理

适用于FPGA、GPU和ASIC系统的电源管理

基于FPGA应用设计优秀电源管理解决方案

如何有效的管理FPGA设计中的时序问题

TI将数字电源管理应用于Xilinx FPGA设计

spartan-6 FPGA电源管理的用户指南资料免费下载

详解FPGA中的电源管理创新分析介绍

篇1:如何为FPGA选择合适的电源管理方案

避免FPGA、GPU和ASIC系统电源管理中的调试周期

FPGA设计中的电源管理

FPGA设计中的电源管理

评论