随着下游新能源汽车、充电桩、光伏、5G基站等领域的爆发,引爆了对第三代半导体——碳化硅材料衬底、外延与器件方面的巨大市场需求,国内众多企业纷纷通过加强技术研发与资本投入布局碳化硅产业,今天我们首先来探讨一下碳化硅衬底的国产化进程。

◆ 碳化硅衬底类型

碳化硅分为立方相(闪锌矿结构)、六方相(纤锌矿结构)和菱方相3大类共 260多种结构,目前只有六方相中的 4H-SiC、6H-SiC才有商业价值。另碳化硅根据电学性能的不同主要可分为高电阻(电阻率 ≥105Ω·cm)的半绝缘型碳化硅衬底和低电阻(电阻率区间为 15~30mΩ·cm)的导电型碳化硅衬底,满足不同功能芯片需求,其中:

半绝缘型碳化硅衬底主要应用于制造氮化镓射频器件。通过在半绝缘型碳化硅衬底上生长氮化镓外延层,制得碳化硅基氮化镓外延片,可进一步制成氮化镓射频器件;

导电型碳化硅衬底主要应用于制造功率器件。与传统硅功率器件制作工艺不同,碳化硅功率器件不能直接制作在碳化硅衬底上,需在导电型衬底上生长碳化硅外延层得到碳化硅外延片,并在外延层上制造各类功率器件。

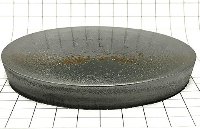

大尺寸碳化硅衬底有助于实现降本增效,已成主流发展趋势。衬底尺寸越大,单位衬底可生产更多的芯片,因而单位芯片成本越低,同时边缘浪费的减少将进一步降低芯片生产成本。目前业内企业量产的碳化硅衬底主要以4英寸和6英寸为主,在半绝缘型碳化硅市场,目前衬底规格以4英寸为主;而在导电型碳化硅市场,目前主流的衬底产品规格为6英寸。国际巨头CREE、II-VI以及国内的烁科晶体都已成功研发8英寸衬底产品。

◆ 碳化硅单晶制备技术

碳化硅衬底制备技术包括 PVT 法(物理气相传输法)、溶液法和HTCVD法(高温气相化学沉积法)等,目前国际上基本采用PVT法制备碳化硅单晶。 SiC单晶生长经历3个阶段,分别是Acheson法、Lely法、改良Lely法。

利用SiC高温升华分解特性,可采用升华法即Lely法来生长SiC晶体,它是把SiC粉料放在石墨坩埚和多孔石墨管之间,在惰性气体(氩气)环境温度为 2 500℃的条件下进行升华生长,可以生成片状SiC晶体。

但Lely法为自发成核生长方法,较难控制所生长SiC晶体的晶型,且得到的晶体尺寸很小,后来又出现了改良的Lely法,即PVT 法(物理气相传输法),其优点在于:采用SiC籽晶控制所生长晶体的晶型,克服了Lely法自发成核生长的缺点,可得到单一晶型的SiC单晶,且可生长较大尺寸的SiC单晶。

◆ 为何半绝缘型与导电型碳化硅衬底技术壁垒都比较高?

PVT方法中SiC粉料纯度对晶片质量具有较大影响。粉料中一般含有极微量的氮(N),硼(B)、铝(Al)、铁(F e)等杂质,其中氮是n型掺杂剂,在碳化硅中产生游离的电子,硼、铝是p型掺杂剂,产生游离的空穴。

为了制备n型导电碳化硅晶片,在生长时需要通入氮气,让它产生的一部分电子中和掉硼、铝产生的空穴(即补偿),另外的游离电子使碳化硅表现为n型导电。

为了制备高阻不导电的碳化硅(半绝缘型),在生长时需要加入钒(V)杂质,钒既可以产生电子,也可以产生空穴,让它产生的电子中和掉硼、铝产生的空穴(即补偿),它产生的空穴中和掉氮产生的电子,所以所生长的碳化硅几乎没有游离的电子、空穴,形成高阻不导电的晶片(半绝缘型)。

掺钒工艺复杂,所以半绝缘碳化硅很难制备,成本很高。近年来也出现了通过点缺陷来实现高阻半绝缘碳化硅的方法。p型导电碳化硅也不容易制备,特别是低阻的p型碳化硅更不容易制备。

◆ 下游市场需求强劲,碳化硅衬底市场迎来黄金成长期

导电型碳化硅衬底方面,受益于新能源汽车逆变器的巨大需求,将保持高速增长态势,根据中国宽禁带功率半导体及应用产业联盟的数据显示,预计2020-2025年国内市场的需求,4英寸逐步从10万片市场减少到5万片,6英寸晶圆将从8万片增长到20万片;2025~2030年:4英寸晶圆将逐渐退出市场,6英寸晶圆将增长至40万片。

半绝缘型碳化硅衬底方面,受下游5G基站强劲需求驱动,碳化硅基氮化镓高频射频器件将逐步加强市场渗透,市场空间广阔,预计2020-2025年国内市场的需求,4英寸逐步从5万片市场减少到2万片,6英寸晶圆将从5万片增长到10万片;2025~2030年:4英寸晶圆将逐渐退出市场,保守估计6英寸晶圆将增长至20万片。

◆ 碳化硅衬底国产化进程大提速

全球碳化硅衬底代表企业主要有CREE、II-VI、SiCrystal,国际龙头企业相比国内企业由于起步早,在产业化经验、技术成熟度、产能规模等方面具备领先优势,抢占了全球碳化硅衬底绝大部分的市场份额。

随着下游终端市场,新能源汽车、光伏、5G基站等领域的快速增长,为上游碳化硅衬底提供了巨大的市场活力,国内以山东天岳、天科合达、烁科晶体等为代表的企业纷纷跑马圈地碳化硅衬底市场,通过加强技术研发与资本投入,逐渐掌握了4英寸至6英寸,甚至8英寸的碳化硅衬底制造技术,缩小了与国际龙头之间技术与产能方面的差距。

编辑:jq

原文标题:碳化硅衬底的国产化进程

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

碳化硅衬底的特氟龙夹具相比其他吸附方案,对于测量碳化硅衬底 BOW/WARP 的影响

测量探头的 “温漂” 问题,都是怎么产生的,以及对于碳化硅衬底厚度测量的影响

不同的碳化硅衬底的吸附方案,对测量碳化硅衬底 BOW/WARP 的影响

碳化硅衬底的环吸方案相比其他吸附方案,对于测量碳化硅衬底 BOW/WARP 的影响

什么是MOSFET栅极氧化层?如何测试SiC碳化硅MOSFET的栅氧可靠性?

优化湿法腐蚀后碳化硅衬底TTV管控

降低碳化硅衬底TTV的磨片加工方法

碳化硅衬底,进化到12英寸!

中国碳化硅衬底行业产能激增,市场或将迎来价格战

全国最大8英寸碳化硅衬底生产基地落地山东?

碳化硅压敏电阻 - 氧化锌 MOV

碳化硅衬底产业全景:国内外主要厂商分布图

简述碳化硅衬底的国产化进程

简述碳化硅衬底的国产化进程

评论