1. 前言

在数字IP/IC,FPGA项目的上板验证阶段,对于一些难以确定原因的bug,比如:RTL仿真时,测试pattern覆盖不够全面,fpga跑起来后的实际信号时序可能跟RTL 仿真不一致,从而出现Bug。一种debug的方式就是用FPGA工具提供的ILA模块(xilixn在ISE中叫:chipscope),来实时抓取FPGA内部数字信号的波形,分析逻辑错误的原因,帮助debug。

ILA的正确、高效使用,能加速debug的进程。

2. ILA工作原理

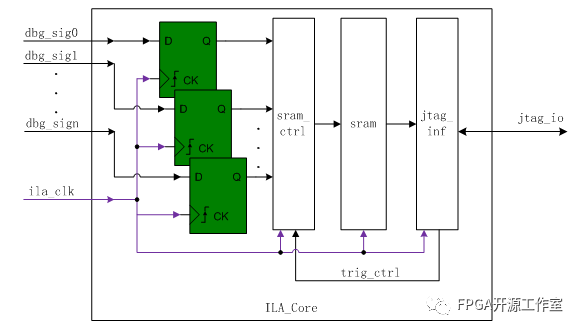

根据xilinx的datasheet功能描述,猜测ILA也是一个数字IP,大致结构如下:

其中:

1) dbg_sig?:是待观测的debug信号;

2) ila_clk:是设置的ILA工作时钟(监测、抓取);

3) jtag_inf:ILA数据与上层的交互口(tigger条件设置,抓取的数据上传);

4) sram_ctrl:根据trig_ctrl,触发抓取,并把抓取的数据按cila_clk的cycle实时写入SRAM;

5) sram:抓取数据的存储空间;

6) jtag_io:Jtag协议定义的标准IO;

根据这个大致结构,预计ILA工作原理如下:

1) PC端GUI应用程序设置trigger条件;通过jtag_io配置进入ILA core;

2) ILA core开始工作,使用ila_clk监测debug信号是否符合tigger条件;

3) 符合条件后,使用ila_clk抓取debug信号,并实时存入SRAM;

4) 抓取结束后,通过jtag_io把debug信号的值上传到PC端;

5) PC端GUI应用程序显示波形;

根据这个工作原理,可以推导出ILA的一些使用特性:

1) ILA加入后,需要增加LUT/DFF的使用量;

2) ILA加入后,需要增加的使用量,跟debug信号的数量,抓取深度成正比;

这些特性,跟实际布局布线后的结果是匹配的。

3. ILA使用方法与注意

ILA的使用步骤如下:

A. 设计综合;

B. 点击:Set Up Debug开始添加ILA;

C. 添加debug信号:

D. 对每个debug信号选择监测、抓取时钟:

E. 设置抓取特性:

F. 结束,保存ILA设置。ILA信息将存入工程的xdc约束文件:

到此,ILA插入结束,在place&route完成,产生configure bit后,下载进入FPAG即可使用ILA进行内部观测了。

4. ILA使用注意

在ILA的使用过程中,有如下3点需要注意:

A. 设置监测、抓取时钟时,最好用drive这个信号的clk。因为是数字电路,也存在跨时钟域的问题。如果ila_clk和debug信号的clk不一致,这儿就是一个跨时钟域的点。在P&R时,timing会报错。你可以用set_false_path来mask掉这些timing violation,但是需要记住跨时钟域的特性:如果debug一个4bit信号,实际信号只有4‘b0001--》 4’b0111的变化,可能抓取到:4‘b0001--》 4’b0101 -》 4‘b0111。

B. 因为综合可能优化掉一些信号(尤其是组合逻辑),或改变信号的名字,为了keep某些信号,可以在RTL code中,添加:“* mark_debug = “true” *”,使用如下:

C. 设置抓取特性时,“input pipe stage”建议设置到2~3。这样虽然多用些DFF,可以确保ILA输入时的timing更容易过。因为你的debug逻辑可能离ILA core非常的远,增加pipe stage寄存器,可以把信号一级一级pipe到ILA core的输入口。

5. 写在最后

虽然ILA比逻辑分析仪好用多了,但是并不建议靠ILA来debug。因为:

1) ILA分析的波形长度有限;

2) ILA抓取的信号数量有限;

3) 添加大量信号时,麻烦;

4) 如果需要新加debug信号,需要重新做ILA,在Place&Route,这样费时费力(一个稍大的工程,可能需要跑数小时);

所以,“此女”虽好但不可亵玩焉,否则走火入魔,举步维艰。建立完备的测试pattern,cover全功能点,跑RTL simulation才是正道。

编辑:jq

-

数字电路

+关注

关注

193文章

1604浏览量

80567 -

GUI

+关注

关注

3文章

655浏览量

39624 -

ILA

+关注

关注

0文章

5浏览量

3589

原文标题:数字IC/FPGA设计基础_ILA原理与使用

文章出处:【微信号:bianpinquan,微信公众号:变频圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ADC12DJ3200设置斜坡测试模式,通过ILA查看数据,从第九个数据开始出现错误,怎么解决?

光纤收发器的使用方法和注意事项

BLDC电机的工作原理和使用方法

钳形电流表的使用方法和注意事项

LCR电桥测试仪的工作原理与使用方法

点焊机的工作原理及使用方法

如何在下载Bitstream后自动触发ILA采集

板式换热器工作原理 板式换热器的安装和使用方法

制氧机原理及使用方法 空气制氧机的工作原理

游标卡尺的使用方法及注意事项

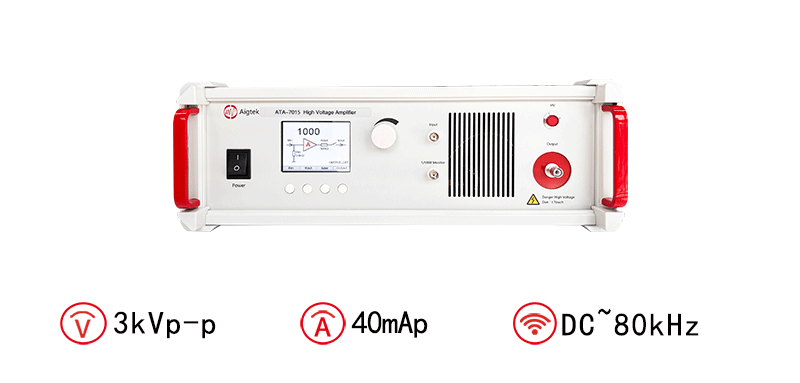

高压放大器的工作原理和使用方法是什么

ILA工作原理 ILA使用方法与注意

ILA工作原理 ILA使用方法与注意

评论