本篇文章来自赛灵思高级工具产品应用工程师 Hong Han.

本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado.

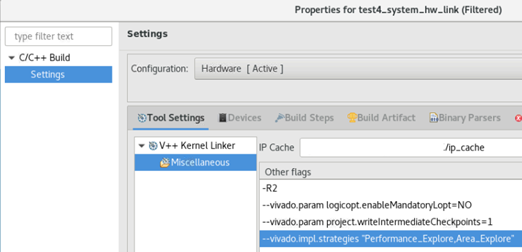

对于Vivado实现阶段策略的指定:

--vivado.impl.strategies

举例设置需要尝试的实现策略:

--vivado.impl.strategies “Performance_Explore,Area_Explore”

对应configure文件的内容:

#Vivado Implementation Strategies

[vivado]

impl.strategies=Performance_Explore,Area_Explore

在Vivado中可以建立多个基于相同的综合结果不同策略的impl run来尝试在单次运行获取更好的结果,而过去的Vitis一直以来只能支持单一的策略。这里我们可以看到Vitis 2020.2已经可以支持同时在一个run中选择多个策略进行尝试, 不同策略用逗号隔开,工具会自动选择先满足时序的策略来直接后续的步骤并生成XCLBIN文件。

如需等待所有策略都跑完再挑最好的结果,可以设置 --advanced.compiler 参数

[advanced]

param=compiler.multiStrategiesWaitOnAllRuns=1

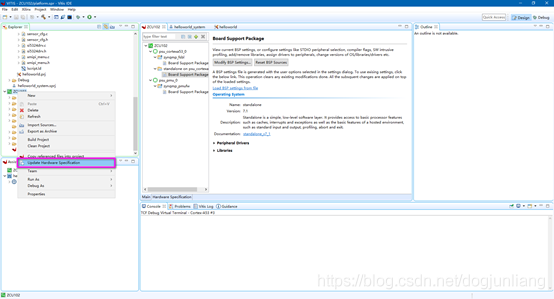

在Vivado工程中,可以看到有三个impl runs,一个default策略和另两个用--vivado.impl.strategies 添加的 Performance_Explore和Area_Explore策略。

对于Vivado仿真阶段选项的指定

举例:意图在仿真xelab阶段覆盖原有的timeunit, 在Vivado中需要执行以下的命令: (关于仿真选项的具体含义,请参考UG900)

UG900 https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug900-vivado-logic-simulation.pdf

set_property -name {xsim.elaborate.xelab.more_options} -value {-override_timeunit -timescale 1ns/1ps} -objects [get_filesets sim_1]

相应的v++ --link 的选项:

--vivado.prop=fileset.sim_1.xsim.elaborate.xelab.more_options={-override_timeunit -timescale 1ns/1ps}

对于Vivado综合阶段选项的指定

Vitis加速kernel设计实际是一个DFX的设计(关于DFX的内容可以参考UG909),平台的逻辑属于静态逻辑,其布局布线事先就已经完成且锁定。 包含kernel的逻辑属于动态部分,需要单独做out-of-context综合并连接到平台的既有网表中做in-context 实现。

UG909:https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug909-vivado-partial-reconfiguration.pdf

加入我们期望对于这部分逻辑综合采用 AreaOptimized_medium Directive,需要执行的Vivado命令如下:

synth_design -top ulp -part xcu200-fsgd2104-2-e -mode out_of_context -directive AreaOptimized_medium

对应的V++ --link选项是:

vivado.prop=run.my_rm_synth_1.STEPS.synth_DESIGN.ARGS.DIRECTIVE=AreaOptimized_medium

注意:在这里synht run的的名字是my_rm_synth_1,可能随着Vitis版本或者平台有变化,使用的时候需要注意是否需要做相应的修改。

在底层Vivado工程的synth run的log文件中可以看到综合的Directive已经成功改为之前设置的值AreaOptimized_medium

其他的Vivado属性指定:

--export_script/--custom_script: 导出脚本/使用用户脚本定制编译和连接的过程

--remote_ip_cache: 指定远程IP Cache 目录

--no_ip_cache: 关闭IP Cache

总结:在这里介绍了通过Vitis选项将各类Vivado的设置传递到底层Vivado工程的方法并举例说明, 希望能帮助用户在Vitis侧能很精细地控制Vivado的各类属性。

编辑:jq

-

编译

+关注

关注

0文章

665浏览量

33204 -

DFx

+关注

关注

0文章

35浏览量

10635 -

Vivado

+关注

关注

19文章

819浏览量

67238

原文标题:开发者分享 | 如何在Vitis中把设置信息传递到底层的Vivado (下)

文章出处:【微信号:TheAlgorithm,微信公众号:算法与数据结构】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何在Vitis中把设置信息传递到底层的Vivado

使用Vitis 在EBAZ4205(ZYNQ)矿机上实现"Hello World!"

如何使用vivado在verilog中传递shell命令

Vitis的使用教程

使用Vitis HLS创建属于自己的IP相关资料分享

【KV260视觉入门套件试用体验】+02.开发环境安装Vitis/Vivado(zmj)

Vivado HLS和Vitis HLS 两者之间有什么区别

Vitis初探—1.将设计从SDSoC/Vivado HLS迁移到Vitis上

在Vitis中把Settings信息传递到底层的Vivado

在Vitis中把Settings信息传递到底层的Vivado

评论