上篇博文:【FPGA】SRIO IP核系统总览以及端口介绍(一)(User Interfaces 之 I/O Port)根据数据手册PG007,介绍到了逻辑层接口的IO口,今天想研究下,这些端口如何使用,结合实际问题来想想这个问题。

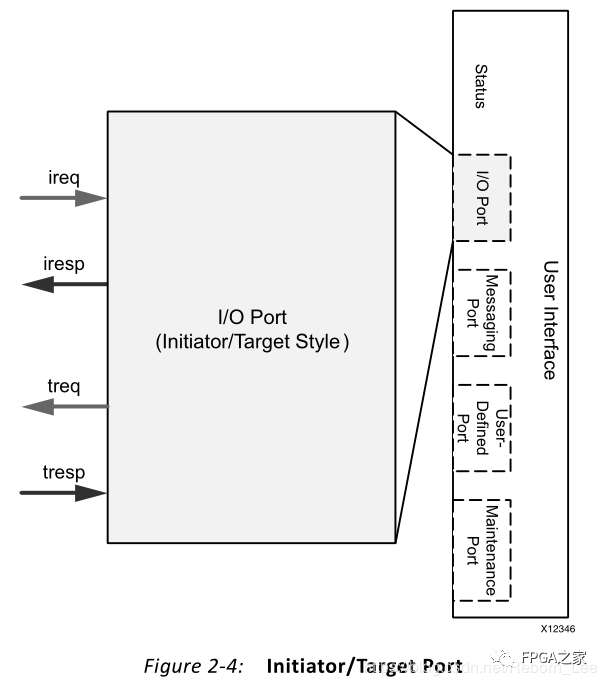

我们知道I / O端口可以配置为两种样式之一:Condensed I/O or Initiator/Target.

我们考虑使用Initiator/Target方式:

这种方式的端口信号分为ireq/iresp与treq/tresp这两对信号类型。

假如通信双方是DSP和FPGA,DSP发数据,而FPGA收数据;

对于FPGA来说,这端为initiator,ireq为发数据请求信号,iresp为来自DSP的响应信号;对于DSP发来的数据,treq为DSP发送数据的请求信号,而tresp为对DSP的响应信号。

从远程设备接收的响应在发起者响应(iresp)信道上呈现给用户设计。

下面为数据手册上的描述:

Requests generated by the local endpoint are placed on the Initiator Request (ireq) channel to be transmitted on the link. Responses received from a remote device are presented to the user design on the Initiator Response (iresp) channel.

Requests originating from a remote device which are received by the core are presented to the user design on the Target Request (treq) channel. Responses to these requests, which are generated by the user design, are placed on the Target Response (tresp) channel.

意思是本地设备的请求信号在ireq channel上,对应的远程设备的响应在iresp channel上。

而远程设备的请求在treq上,对应的本地响应在tresp上。

Table 2-5 shows the signals associated with the Initiator/Target port. At the

• s_axis_ireq* are associated with INITIATOR_IREQ.

• m_axis_iresp* are associated with INITIATOR_IRESP.

• m_axis_treq* are associated with TARGET_TREQ.

• s_axis_tresp* are associated with TARGET_TRESP.

从treq/tresp信号开始:(treq从DSP发起的请求信号,FPGA端收到数据后,就从treq中提取有用信息)

m_axis_treq_tvalid 表明数据有效;(输出)

m_axis_treq_tready 握手信号。表明来自源端的数据被接收;(输入)

m_axis_treq_tdata[63:0] 包头和数据;(数据)

m_axis_treq_tkeep[7:0]

字节限定符,指示相关联的数据字节的内容是否有效。如果端口配置为使用HELLO格式,则这与8'hFF相关联。对于配置为使用SRIO Stream格式的端口,此输出设置为8'hFF,除非设置了tlast。

位7对应于数据的最高有效字节(tdata [63:56]),位0对应于最低有效字节(tdata [7:0])。(输出)

m_axis_treq_tlast 表示数据包的最后一拍。(输出)

m_axis_treq_tuser[31:0] (输出)

HELLO格式:在数据包的第一拍时有效,该信号由数据包的源ID(31:16)和目标ID(15:0)组成。如果使用8位设备ID,则每个ID的最高有效字节应填充0。

SRIO流格式:在此格式中,tuser只有8位宽。如果设置了数据包的关键请求流(CRF)标志,则设置位1。

所有其他位都保留。在数据包中的后续节拍中,保留此字段。

对于其他的信号就不一一赘述了。

对于特定应用中,例如FPGA接收来自DSP的数据,FPGA接收端RX的串行数据,最终到达逻辑层会以treq形式给出。我们对此消息进行处理即可。

责任编辑:haq

-

FPGA

+关注

关注

1629文章

21729浏览量

602977 -

IP

+关注

关注

5文章

1701浏览量

149502 -

端口

+关注

关注

4文章

963浏览量

32051

原文标题:【FPGA】SRIO IP核系统总览以及端口介绍(二)(I/O Port 含义介绍)

文章出处:【微信号:VOSDeveloper,微信公众号:麻辣软硬件】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何使用IO口检测电源电压的转换逻辑

单片机IO口相关知识

51单片机、AVR单片机和PIC单片机的IO口操作

51单片机IO口输入输出方式_IO口的四种使用方法

单片机IO口原理解析

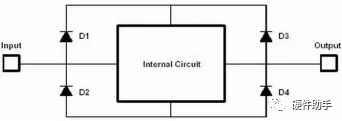

STM32的IO口保护以及FT兼容IO口

IO口模拟SPI

关于stm32单片机准双向IO口配置

使用IO口检测电源电压的转换逻辑

逻辑层接口的IO口如何使用

逻辑层接口的IO口如何使用

评论