本篇博文中的分析是根据客户真实问题撰写的,该客户发现即使时序已得到满足的情况下,硬件功能仍出现错误。最后发现,问题与时钟域交汇 (Clock Domain Crossing) 有关,因此,本篇博文介绍了如何调试设计中的时钟域交汇问题。

问题说明:

在此设计中,用户生成了比特流并将其用于器件编程,在硬件上进行测试时,用户发现少量时钟域上无法获得期望的功能。

用户对行为仿真和实现后仿真进行了测试,发现信号上可得到正确的结果。

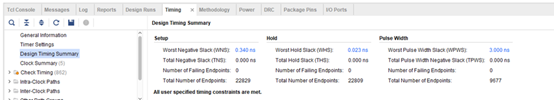

同时,这些用户未发现任何种类的时序违例,所有值均为正值,如“设计时序汇总 (Design Timing Summary)” 中所示。

注:您可使用以下选项自行检查设计的时序汇总信息:

■ 在 Vivado GUI 中,转至“报告 (Reports)”选项卡 -》“时序 (Timing)”-》“时序汇总报告 (Report Timing Summary)”

■运行以下 Tcl 命令:

report_timing_summary -file 《filepath》/timingreport.txt

根本原因:

硬件功能问题背后可能存在多种原因。

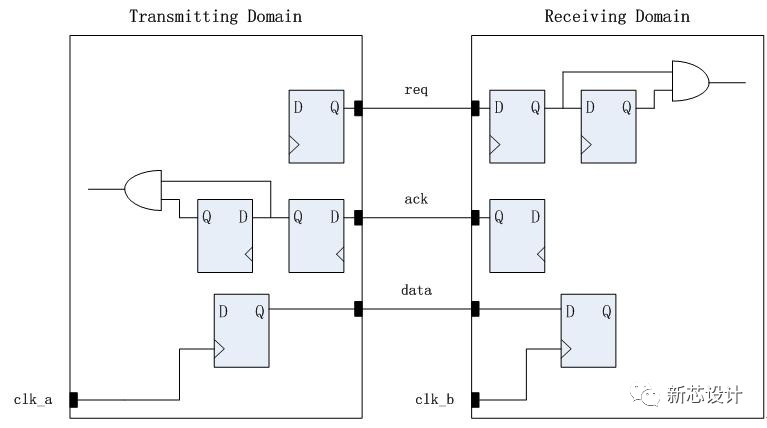

包括缺少时钟域交汇 (CDC) 同步器、时钟拓扑欠优化、时钟结构中使用了组合逻辑、亚稳态以及经典的未约束路径问题。

要检查与时钟/架构/CDC 等相关的警告/严重警告,可使用方法论报告。

要在 Vivado GUI 中打开方法论报告,请转至“报告 (Report)”选项卡 -》“方法论报告 (Report Methodology)”,或者在 Tcl 控制台 (Tcl console) 中,使用 report_methodology。

报告打开后,您可能会看到几条与设计相关的警告和严重警告,需您进行检查。

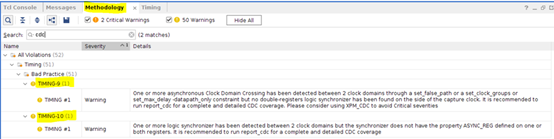

在此示例中,报告中显示了几条警告,这些警告与 CDC 相关的错误实践有关(这些警告的 ID 为 Timing-9 和 Timing-10),如下所示。

这些警告声称工具经由约束语句(例如,set_false_path 或 set_clock_groups)的使用,在 2 个时钟域之间检测到一个或多个异步时钟域交汇。

但它在捕获时钟端未找到任何双寄存器逻辑同步器。因此,它建议用户运行 report_CDC 并对这些 CDC 路径执行进一步分析。

要在 Vivado GUI 中打开 CDC 报告,请转至“报告 (Report)”选项卡 -》 “时序 (Timing)”-》“CDC 报告 (Report CDC)”。或者,您可在 Tcl 控制台中运行 report_cdc 命令。

请参阅 (UG906) 以获取有关阅读此 CDC 报告的详细指南。

CDC 报告显示在发生硬件功能错误的时钟域内存在不安全的未知 CDC 端点(如下所示)。请参阅 (UG906) 以了解此报告命名法。

如何解决这些警告/严重警告?

1) (UG906)包含有关这些警告以及其它时序方法论检查的详细说明。请详查其中提供的示例,以理解每一项警告及其根本原因。您可通过添加适当的同步电路(通过修改 RTL 或者使用赛灵思可参数化宏 (XPM))来相应改善设计。

2) 您可能还需要相应添加或修改约束,或者在 RTL 源代码中为 CDC 端点添加 ASYNC_REG 属性。(您还可参阅(UG906)以便详细了解 CDC 拓扑结构。)

3) 对于伪静态寄存器接口,最好将 CDC 接口豁免,而不是对其进行过度设计。

如需获取有关豁免以及如何创建豁免的更多信息,请参阅 (UG906)。

注:伪静态 CDC 寄存器接口为包含近似静态的配置寄存器的 CDC 路径。这些路径初始化后可能不再改变,或者可能仅改变 1 次,因此用户几乎可以将其看作是静态的。

结论

对 CDC 路径完成必要修改后,客户得以成功通过硬件的功能测试。

编辑:jq

-

寄存器

+关注

关注

31文章

5343浏览量

120345 -

RTL

+关注

关注

1文章

385浏览量

59781 -

CDC

+关注

关注

0文章

57浏览量

17809

原文标题:开发者分享 | 使用方法论报告 1:时序已满足,但硬件功能出现错误

文章出处:【微信号:gh_2d0d1910c28b,微信公众号:思佳讯SkyworksSolutions】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何处理好FPGA设计中跨时钟域问题?

如何处理好FPGA设计中跨时钟域间的数据

关于FPGA中跨时钟域的问题分析

由于时钟域交汇处理不当所导致罕见的比特翻转

如何调试设计中的时钟域交汇问题

如何调试设计中的时钟域交汇问题

如何调试设计中的时钟域交汇问题

评论