Virtex UltraScale+部分芯片中集成了HBM(High Bandwidth Memory)。HBM的容量最小为8GB,最大可达16GB,极大地增强了存储带宽。

先从芯片结构角度看,对比VU13P和VU37P,把VU13P的SLR0用HBM替换,同时在SLR1内增加了32个HBM AXI接口(硬核),其余两个SLR(SLR2和SLR3)保持不变,就构成了VU37P。这样VU37P其实就是3个SLR加上HBM构成的SSI芯片。

从设计角度考虑,仍以VU37P为例。作为多die芯片,跨die路径是设计性能的一个瓶颈。使用HBM时,如果跨die路径是从SLR2到HBM,这意味着这条路径穿过了SLR1和SLR0,也就是两次跨die,因此,需要添加至少5级别流水寄存器以实现时序收敛,如下图所示。

同时,Xilinx建议确保从SLR2到SLR0的HBM AXI接口路径是垂直的,而不是对角交错的,如下图右侧是推荐的路径,而左侧布局方式则容易导致布线拥塞。

由于HBM以及32个HBM AXI硬核接口都在SLR0内,因此合理规划SLR0的资源利用率可有效缓解布线拥塞。对于HBM AXI接口利用率较高的设计,应尽可能减少与HBM无关逻辑的资源利用率,以保证HBM AXI能够使用到最佳位置的逻辑资源。

此外,由于HBM AXI接口靠近I/O列,如下图中蓝色菱形标记所示。因此,如果在SLR0使用MIG IP会增加时序收敛的难度,建议此时将MIG IP放置在SLR1或SLR2。这要在设计初期规划好。

当同时使用PCIE4C和HBM时,Xilinx建议使用距离HBM AXI接口最远的PCIE4C。

责任编辑:haq

-

芯片

+关注

关注

455文章

50784浏览量

423450 -

HBM

+关注

关注

0文章

379浏览量

14752

原文标题:使用带HBM芯片的注意事项

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

测试光伏逆变器需要注意哪些地方呢?

TLV320aic33进行ADC的使用时,为什么没有输出?ADC使用时有什么要注意的地方吗?

请问启用AIC3104本身降噪功能,有什么需要注意的地方?

DS16EV5110A使用有什么需要注意的吗?

THS4001在设计电路上有什么特别需要注意的地方吗?

使用THS3091有什么要注意的地方吗?

应用PLC需要注意哪些问题

三星HBM芯片遇阻英伟达测试

四川长虹回应帮华为代工 HBM芯片备受关注

电阻应变片的类型有什么?电阻应变片的使用有什么需要注意的吗?

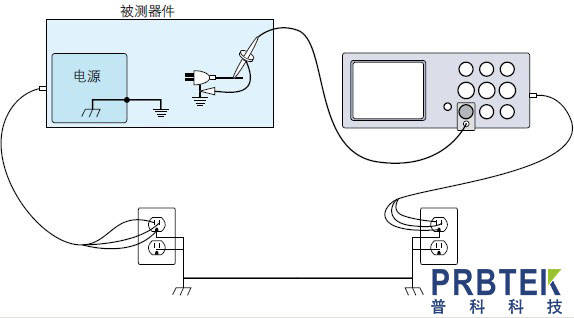

示波器表笔正确的接地方法及注意事项

使用带HBM芯片有哪些要注意的地方

使用带HBM芯片有哪些要注意的地方

评论