FIFO是在FPGA设计中使用的非常频繁,也是影响FPGA设计代码稳定性以及效率等得关键因素。在数据连续读取时,为了能不间断的读出数据而又不导致FIFO为空后还错误的读出数据。可以将FIFO的Empty和Almost_empty以及读使能配合起来使用,来保证能够连续读,并准确的判断FIFO空满状态,提前决定是否能启动读使能。

具体的实施办法是:当Empty为1,立即停止读;当Empty为0,Almost_empty为0时,可以放心读;当Empty为0,但是Almost_empty为1时,如果上一拍读使能Read也为1,那么不能读;当Empty为0,但是Almost_empty为1时,如果上一拍读使能Read为0,可以读最后一拍。

在FIFO使用时,使用到Almost_full信号以及读写counter来控制FIFO的读满预警,如果数据不是在空满判断的下一拍写入FIFO,则设计FIFO的满预警时要小心。如果你不确定判断满预警之后要延迟多少拍才能真正写入FIFO,那么尽量让FIFO有足够满预警裕量。

例如,在wr_data_count为128才是真的满了,你可以设成wr_data_count为120的时候就给出满预警,可以保证设计的可靠和安全。当然,如果你能准确的算出判断满预警与真正写入FIFO的延迟,可以用精确的满预警阈值。

当需要使用到数据位宽转换时,如将128位的数据转换成64位的数据,最好不要用XILINX自己生成的位宽转换FIFO。可以例化两个64位的FIFO,自己控制128转64。这样可以大大的节省资源,是XILINX CORE生成的FIFO资源的一半。

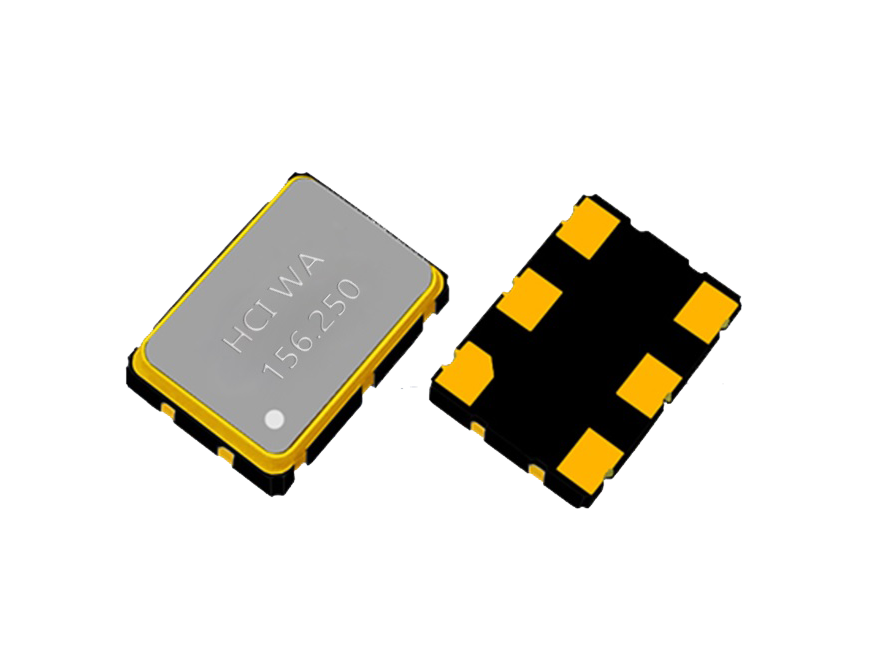

另外,当需要使用到位宽大于18bits,且深度小于等于512的FIFO时,建议使用XILINX COREGenerator来产生,它可以将一个36bits位宽512深度的FIFO在一个18×1024的BLOCK RAM中实现。如果我们自己用BLOCK RAM来实现一个FIFO,那只能例化一个36×1024的BLOCK RAM基元,造成浪费。

责任编辑:haq

-

FPGA

+关注

关注

1664文章

22508浏览量

639465 -

Xilinx

+关注

关注

73文章

2208浏览量

131962 -

fifo

+关注

关注

3文章

407浏览量

45914

原文标题:FIFO使用技巧

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

浅谈FPGA在无叶风扇控制器中的应用

基于FPGA的高效内存到串行数据传输模块设计

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

求助,关于串口设备驱动fifo问题

AI狂飙, FPGA会掉队吗? (中)

FPGA在机器学习中的具体应用

CYT2B93CAE如何构建不产生中断的FIFO?

【RK3568+PG2L50H开发板实验例程】FPGA部分 | ROM、RAM、FIFO 的使用

PLL技术在FPGA中的动态调频与展频功能应用

在FPGA设计中FIFO的使用技巧

在FPGA设计中FIFO的使用技巧

评论