电子发烧友网报道(文/程文智)不论我们设计的电子产品是应用在云计算、无线LTE、数据中心,还是物联网、汽车、医疗保健,或者是航空航天等领域,系统内必然需要时钟产品的支持,时钟产品就如人类的脉搏一样,只有在时钟的支持下,电子产品才能正常工作。

那么时钟产品有哪些种类,它们分别有什么特性,工程师在选用的时候需要注意些什么呢,我们今天就来一起聊一聊。

时钟产品的分类

时钟产品主要分为两大类,一类是异步时钟产品,它的功能是给本地单板提供工作时钟,包括晶振、时钟发生器,及时钟缓冲器等等;另一类是同步时钟产品,它的功能是跟踪上下游时钟产生同步之后的时钟给下游使用,它主要包括滤抖芯片、同步以太网(SyncE)和IEEE1588时钟产品等。

具体一点来分的话,工程师常用的时钟产品主要是六个大类:

一是振荡器,包括MEMS振荡器和石英振荡器,TCXO、MCXO、OCXO、EMXO、VCXO、VCSO都是石英振荡器。值得一提的是MEMS振荡器和石英振荡器是有本质不同的。

二是时钟生成器,主要是低抖动、低功耗的时钟发生器。

三是时钟分配器,它实际上是时钟缓冲器,包括低附加抖动的各种各样的缓冲器。详细来看,有扇出缓冲器,零延时缓冲器,分频器和多路开关等。

四是抖动衰减产品,这类主要用在网络里,或者是上下游,进行时钟滤抖的,比如抖动滤波,时钟转换等。

五是时钟同步产品,包括同步以太网时钟芯片和IEEE1588的时钟芯片。

六是其他简单的时钟器件,包括555定时器,逻辑转换器,交叉点开关,触发器/逻辑门等等。

接下来我们来看一看这些不同类型的时钟产品都有哪些特点,在选用不同类型的时钟产品时,有哪些注意事项。

晶体振荡器和MEMS振荡器

振荡器产品分为两类,一类是传统的石英晶体振荡器,第二大类是MEMS振荡器。

对于传统的石英晶体振荡器,它们通常是属于模块,而不是传统意义上基于硅的芯片,MEMS振荡器则是传统意义上的芯片。为什么这么说呢?

对于传统的石英晶体振荡器,通常有晶体、XO、VCXO、TCXO、OCXO等几种。

对于晶体而言,虽然它内部有振荡电路,但是由于晶体是无源的,一般无法进行独立振荡,用户通常需要在外面加上合适的电阻和电容,构成外部谐振电路,才能让它产生用户需要的频率。

XO或时钟振荡器是最基础的振荡器,由晶体和基本驱动电路组成,内部不但集成了谐振电路,还集成了驱动电路。因此,用户只需要提供一个稳定的电源,就能产生所需要的频点。但是由于没有任何形式的补偿,频率稳定基本上是依靠晶体本身的特性。

VCXO,即压控晶体振荡器,它内部有一个VC的压控端,用户可以通过调整VC压控端的电压,从而让VCXO成为了一个频率可以微调的时钟输出。也就是说,它可以依赖石英晶体的特性,通过施加外部电压来控制振荡器的输出频率变化。

TCXO,即温补晶体振荡器,通过附加的温度补偿电路来补偿因环境温度变化而引起的振荡器频率变化。它的内部包含一个温度补偿电路,当外部环境温度变化的时候,温度补偿电路会去补偿因为温度的变化造成的晶体频率的偏差,从而产生一个相对稳定的频率输出。

但是,对于一些特殊的应用场合,TCXO仍然是不能满足要求的,因此,另外一种产品应运而生了,那就是OCXO。

OCXO,即恒温晶体振荡器,它内部具有一个恒温槽,恒温槽会根据晶体不同的加工工艺,使恒温槽保持在80~90℃的恒定范围。也就是说谐振电路相当于工作在空调房内一样,从而保证了谐振电路输出频率的相对稳定。

不论是无源的晶振还是有源的晶振,除了谐振电路之外,还需要一些辅助的电路,比如说温度补偿电路,恒温槽的控制电路等等。

也就是说,此类产品中的谐振电路和辅助电路其实是放置在一个类似PCB的基板上,再与晶体封装起来,形成了一个振荡器产品。因此,对于传统的石英晶体振荡器来说,它是一个模块,而不是一个基于硅片的IC。

对于MEMS振荡器而言,是完全不一样的,它是采用硅晶圆生产工艺制造,并通过电极产生静电场来激励谐振器。也就是说,它完全基于硅片,因此,MEMS振荡器是一个IC产品。

正是因为这样,石英晶体振荡器与MEMS振荡器之间是有一些差异的。由于MEMS振荡器是基于硅的芯片,因此,它在抗振动、抗冲击、失效率、封装和交货时间,以及灵活性上,是远远领先于石英晶体振荡器的。

但是,对于一些特殊的应用场合,比如频率稳定度要求很高的场合,OCXO的频率稳定度要更高。因此,一些特殊应用场合仍然会使用石英晶体振荡器。

当然,随着技术的进步,MEMS振荡器的频率稳定度也在逐渐提升当中,业内目前有厂商可以提供与TCXO稳定度相当的产品。

图2:振荡器的比较(来源:Microchip)

振荡器产品有MEMS振荡器、石英晶体振荡器,以及原子钟振荡器。这一系列振荡器产品中,他们的性能是完全不一样的,比如说温度稳定性、老化率、24小时保持性能、相位噪声性能等等,都是不一样的。此外,功率和成本也完全不同。

工程师可以根据自己的实际情况去选择合适的振荡器产品,不管是哪种产品,那么通常需要关注哪些常见的参数呢?

一般来说,工程师在选择振荡器产品的时候,需要关注频率稳定性、初始容差、老化率、抖动、相位噪声和保持性能等等。当然,对于一些特殊的应用场合,和一些特殊的振荡器产品,还有一些特殊的参数需要去关注。

接下来,我们看一个OCXO的典型应用场景。

OCXO在外部控制器和其他电路的配合下,形成了一个闭环的模拟锁相环(APLL),该APLL可以锁定GPS提供的1pps的信号输入,产生1pps的信号输出和一个10MHz频率的时钟输出,系统可以根据1pps的信号输出和10MHz时钟输出做各种各样的数据和信号处理。

时钟发生器

时钟发生器也可以称为频率合成器,一般来说需要外加晶体或振荡器做为参考。时钟发生器的主要功能是实现频率变换,可以对参考源晶体或振荡器频率进行倍频或降频,从而产生1路或多路输出。

在时钟发生器的内部,实际上是一个模拟锁相环(APLL),该APLL可以锁定来自外部的参考时钟,这个参考时钟可以是上游提供的参考时钟,也可以是振荡器提供的参考时钟。APLL可以把时钟参考时钟倍频到高频,比如将25MHz的信号倍频到4GHz,然后基于4GHz再做分频,从而产生各种各样的频率。

其实除了上面提到的APLL,还有数字锁相环(DPLL),这两者有何差异呢?对于APLL而言,固有抖动非常好,但它有自己的缺点,比如不够灵活、带宽不能做得很低、没有办法提供各种各样的保持功能。

DPLL跟APLL恰好相反,它的固有抖动比较差,但是它非常灵活、带宽可以做得很低、能提供非常优秀的基于算法的保持功能。

但其实,不论是APLL,还是DPLL,他们都两个共同点,一是他们都是低通滤波器;二是他们都是闭环的负反馈系统。

复杂的系统中通常有多路时钟域,每个时钟由独立的晶体或振荡器产生。相比之下,时钟发生器具备诸多优势:高度集成、可代替多个晶体或振荡器、占用电路板的空间少,以及可靠性高等。

那么,在选择时钟发生器时,需要考虑哪些参数呢?一般来说,主要考虑的参数有:输出时钟可以支持的频率范围、输出时钟可以支持的时钟域、输出时钟可以支持的路数、抖动/相位噪声等。

此外,还可根据需求考虑其他一些参数,比如输出电平可以支持的类型、是否支持SSC扩频时钟、是否支持相位调节、是否需要零延时功能、是否支持默认加载配置等。

拿Microchip的ZL30267时钟发生器来说,它内部有两个APLL,它们同时锁定到了同一个XO,然后产生了以太网络需要的156.25MHz时钟;PCIe系统所需要的100MHz时钟;以及USB系统需要的48MHz时钟。也就是说,通过这样的时钟发生器,可以产生各种各样的频点,给单板做工作时钟。

时钟缓冲器

当系统中需要多路时钟信号时,最有效的产生方法是使用时钟缓冲器。而时钟缓冲器实际上是一个比较简单的器件,本质上来说,它实现了时钟的驱动,比如说前面有一个时钟进来,可以通过时钟缓冲器,实现多个相同频段的输出。

在选用时钟缓冲器时,工程师除了关注输入输出,以及输出频率等常规参数之外,尤其要注意另外一个参数是附加抖动RMS。为什么关注该参数呢?因为对于时钟缓冲器产品,是会劣化时钟的,也就是说,一个好的,低抖动的时钟输入进来,经过时钟缓冲器之后,时钟的抖动会变大。那么,抖动变大之后的时钟是否满足应用的要求,这一点工程师需要多多关注一下。

滤抖芯片

滤抖芯片,顾名思义就是滤除抖动,既然可以滤除抖动,那么芯片内部必然是一个低通的滤波器,滤抖芯片通常会有两种架构类型,第一种是基于模拟锁相环的滤抖芯片,由于模拟锁相环的带宽不能做到非常低,因此基于模拟锁相环的滤抖芯片不能实现非常好的滤抖效果。

另一种是基于数字锁相环加上模拟锁相环的滤抖芯片,这种芯片把DPLL和APLL的优点结合在一起。

比如Microchip的ZL30169,其内部就是基于DPLL和APLL架构的滤抖芯片。它前面是输入的参考时钟,后面是参考时钟的监视器、DPLL模块、APLL模块,分频器模块,输出的驱动电路等。

根据其内部框图,可以看出,除了模块之外,对于内部有DPLL模块的锁相环而言,通常还需要外部提供一个工作时钟,该工作时钟在给DPLL提供工作时钟的同时,还会用这个工作时钟来监控输入参考源的变化。

同步以太网和IEEE1588时钟产品

同步以太网和IEEE 1588时钟产品内部基本上采用了DPLL+APLL的架构。为什么采用这类架构呢,因为这样可以利用APLL抖动性能好,DPLL比较灵活的特点。

同步以太网和IEEE 1588时钟产品通常要满足复杂的协议,比如物理层的7.813,7.862协议等。对于DPLL而言,它内部是可编程的,因此,我们可以在DPLL上面处理各自的算法,这个算法就可以保证满足同步以太网和1588的相关协议。

一般来说,时钟的同步有三种类型:频率同步、相位同步,以及时间同步。它们之间是不一样的。

对于频率同步,他们之间的相差是固定的,但是沿是无法对齐的;对于相位同步,相差是固定的,沿也是对齐的,但每一个沿产生的时刻可能是不一样的;而时间同步,每一个沿产生的时刻是一样的,因此我们称之为时间同步。

拿电信网络来说,整个的电信网络的时钟频率精度必须完全相同,才能完成相互通信;而电信网络实际上是逐级逐跳传递同步信号的。具体来说,电信网络最开始的高精度时钟信号由原子时钟产生,一般原子时钟会作为第一跳的设备,第一级的设备会把同步信号传递到第二级,第二级会把同步信号传递给第三级、第四级等等。

逐级逐跳传递过程中,通过什么来实现的呢,其实就是通过同步以太网和IEEE1588来实现的。

具体来看一下同步以太网时钟在具体设备和网络中,是如何传递的,首先上游同步以太网会给PHY一个参考的工作时钟,PHY收到时钟后,会基于这个时钟,把数据传递给下一级,在接收端,接收端会把时钟和数据解出来,提取出来的时钟,会再给锁相环芯片,锁相环芯片锁定这个时钟,产生一个新的时钟,给PHY的SerDes,它再基于这个时钟,把数据传递出去,从而实现了物理层的逐级逐跳的时钟传递的过程。

设备的内部的同步是怎么样来传递的?电信系统一般是多卡系统,主备2个时钟卡和多个线路卡,输入同步信号从PHY接收器恢复传输到时钟卡系统时钟,再由时钟卡处理后分发信号传输到所有线路卡PHY发送器。

时钟卡和线路卡上都会放置锁相环芯片,但是它们实现的功能是不一样的,时钟卡上的锁相环可以滤除时序干扰(漂移),并在外部时序源暂时丢失时提供保持功能,以及满足各种各样的复杂协议;线路卡上的锁相环芯片可以滤除抖动和转换时钟频率。

IEEE 1588的传递跟同步以太网的传递有点不一样。它是把时间信号放在报文内。逐级逐跳往下传递的。对数字锁相环,或者模拟锁相环而言,它是一个低通滤波器,同时也是一个闭环的负反馈系统,对于IEEE 1588而言,它也是是一个闭环的负反馈系统。但是它的反馈不在芯片内部,而在于板级,或者系统上。

声明:本文由电子发烧友原创,转载请注明以上来源。如需入群交流,请添加微信elecfans999,投稿爆料采访需求,请发邮箱huangjingjing@elecfans.com。

编辑:jq

-

以太网

+关注

关注

40文章

5427浏览量

171816 -

振荡器

+关注

关注

28文章

3832浏览量

139136 -

mems

+关注

关注

129文章

3937浏览量

190699 -

时钟发生器

+关注

关注

1文章

200浏览量

67293

原文标题:不同类型时钟产品的特性及选择时的注意事项

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

不同类型时钟产品的特性及选择时的注意事项

同类型的RISCV核与ARM的核产品在使用上有那些区别?

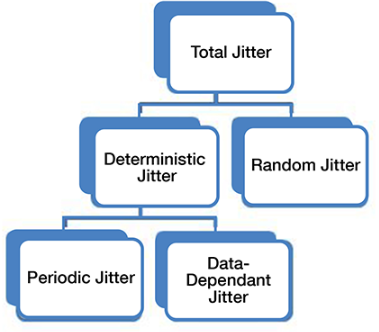

理解不同类型的时钟抖动

光纤的基本类型如何选择质量好和实用的光纤产品

不同类型的边缘计算机应该如何选择

不同类型的边缘计算机如何选择

不同类型电阻的特性资料下载

选择人员定位系统时应该注意什么

选择光纤线应该注意哪些问题-clan

如何识别不同类型的抖动

不同类型时钟产品的特性及选择时应该注意哪些

不同类型时钟产品的特性及选择时应该注意哪些

评论