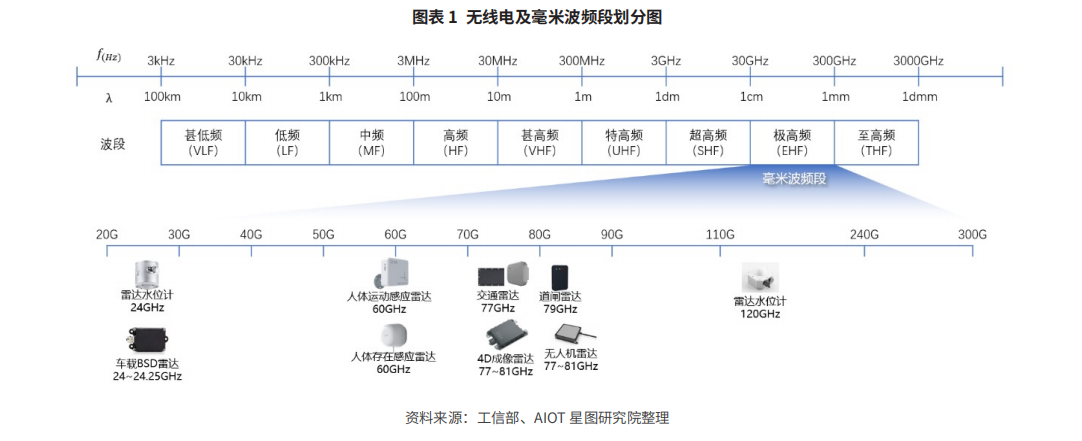

在5G新无线电技术标准中,除了sub-6 GHz频率外,还利用毫米波(mmWave)频率来提高吞吐量。毫米波频率的使用为大幅提高数据吞吐量带来了独特的机会,同时也带来了新的实施挑战。本文探讨sub-6 GHz和毫米波基站无线电之间的架构差异,着重讲述在这些系统上实施DPD面临的挑战和带来的好处。

数字预失真(DPD)是一种成熟技术,通常用于sub-6 GHz无线通信系统,以提高功率效率,但大多数毫米波无线电并不使用DPD。采用ADI波束成型器和收发器构建的包含256个元件的毫米波阵列原型,我们能够证明采用DPD能够将有效各向同性辐射功率(EIRP)提高达3 dB。与不采用DPD,但具有相同目标EIRP的阵列相比,这种阵列的元件数量可以减少30%。

本文旨在比较传统的sub-6 GHz宏蜂窝设计和毫米波基站无线电和天线设计。它进一步介绍了这些设计差异相对于sub-6 GHz无线电将如何影响毫米波阵列中的DPD实施。

除了降低延迟和提高可靠性,对更高数据吞吐量的需求呈指数级增长一直是推动3GPP 5G NR标准发展的强大推动因素之一。虽然4G LTE系统部署在sub-3 GHz频段中,但近年来,将新频谱分配部署在3 GHz至5 GHz范围使得我们能够在5G NR中实现更宽的通道带宽(BW)。与4G LTE相比,sub-6 GHz频段的最大通道带宽已从20 MHz增加到100 MHz。除了更宽的通道带宽外,多根发射和接收天线以及最终的大规模MIMO技术进一步提高了频谱效率。虽然所有这些改进都有助于提供更高的数据吞吐量,但基波限制(分配的sub-6 GHz频谱相对较少)继续将个人用户的峰值吞吐量限制在1 Gbps以下。

在5G NR中,3GPP标准历史上首次为蜂窝移动应用分配了24.25 GHz至52.6 GHz之间的毫米波频率。这个新频率范围被称为FR2,sub-6 GHz频率则被称为FR1。相对于FR1,FR2的可用频谱范围更大。FR2中单个通道的频率可能高达400 MHz,可实现前所未有的吞吐量。但是,使用毫米波频率给基站(BS)和用户设备(UE)带来了新的实施挑战。在这些挑战中,最重要的要属更高的路径损耗和更低的PA输出功率,它们使得基站和UE之间的链路预算非常具有挑战性。

BS与UE之间的路径损耗被定义为 Pl[dB] = 10log10 (Pt/Pr),其中 Pt 和 Pr分别为发射功率和接收功率。在自由空间中,接收功率是距离和波长的函数,也称为弗里斯传输公式,其中 Pr(d,λ) = Pt Gt Gr (λ/4πd)²,Gt 和 Gr分别为发射天线增益和接收天线增益。λ表示波长,d表示发射器和接收器之间的距离。在典型的无线通信环境中,由于附近物体的反射和施工材料造成的损耗,针对路径损耗进行建模和估算将会更加复杂。但是,为了理解毫米波与sub-6 Ghz频段相比具有更高的路径损耗,我们来假设在自由空间中传播、提供相似的天线增益,以及BS和UE之间的距离相等。使用这种方法,可以得出28 GHz时的路径损耗比900 MHz时高出10xlog(28000/900)² = 29.8 dB!

在sub-6 GHz频率下,BS功率放大器输出几十瓦的RF功率,且效率超过40%,这并不罕见。这是通过采用高效率PA架构(例如Doherty)和使用先进的数字预失真技术实现的。相比之下,高线性度AB类毫米波PA通常输出不到1 W的RF功率,且效率低于10%。在毫米波频率下,这些工作条件加剧了BS和UE之间的链路预算挑战。要解决这两大挑战——更高的路径损耗、单个PA功率更低,关键在于将功率更准确地传输到具体的空间位置。使用有源相控阵天线可以实现这一目标,该天线具有波束成型和波束转向能力。

毫米波5G中的天线阵列

天线阵列并不是一个新概念。在GSM部署早期,无源阵列就已经用于蜂窝基站天线,雷达系统使用天线阵列的时间则有数十年。如前文所述,在毫米波频率下,要解决更大的路径损耗和单个PA功率更低的问题,需要使用有源相控阵天线。这是通过在阵列中包含许多天线元件,而每个元件由低功率放大器驱动来实现的。使用更多元件会增加阵列的总辐射功率,同时提高阵列增益并产生较窄的波束。对于相控阵天线理论,本文不予讨论。有关该主题的更多信息,请参阅《模拟对话》系列“相控阵天线方向图”(分三部分)。

有源相控阵天线的高成本限制了其应用范围,目前主要用于航空航天和防务领域。半导体技术的最新发展,加上高水平的集成,使有源相控阵天线能够在5G应用中实现商用。ADI提供有源波束成型器件,它们集成了16个完整的发射和接收通道、相关的PA、低噪声放大器(LNA)、每个路径相位和增益控制,以及TDD开关功能。所有这些全部都集成在一块硅芯片中!这些器件的第一代是使用SiGe BiCMOS技术(ADMV4821)实现的。为了进一步提高功效和成本,第二代器件采用了SOI CMOS工艺(ADMV4828)。这些高度集成、高功效的波束成型器,以及毫米波上/下变频器 (ADMV1017/ADMV1018) 和频率合成器 (ADF4371/ADF4372),为毫米波5G基站构建了完整的RF前端解决方案。

在毫米波频率下,天线元件所占的面积很小。例如,一个简单的28 GHz微带贴片天线通常小于10 mm2。因此,可以在一个相对较小的区域内放置许多天线来提高增益。我们假设一个包含256个元件的天线阵列,双极化辐射元件分8行、16列排列,如图1所示。红线和蓝线分别表示+45°和-45°极化元件。

假设天线元件之间的间距为λ/2,那么该天线阵列的总面积为8(λ/2) × 16(λ/2) = 32λ2。将900 MHz和28 GHz天线进行比较,900 MHz天线阵列的总面积为3.55 m2,28 GHz天线阵列的总面积仅为3.67 × 10-3 m2,几乎小了1000倍!虽然900 MHz下的256元件天线阵列的尺寸令人望而却步,但28 GHz下的类似阵列可以在不到40平方厘米的印刷电路板(PCB)上实现。

28 GHz的256元件双极化毫米波天线阵列是基于多层PCB构建,采用ADI的波束成型器和毫米波上/下变频器。为了降低成本,避免天线和无线电之间形成成本高昂/有损耗的互连,将有源组件部署在PCB的一边,天线元件则部署在PCB的另一边。该板被称为AiB256(AiB代表板上的天线),其图如图2所示。

AiB256上有16个ADMV4828 SOI波束成型芯片,每个芯片提供16个发射和16个接收通道,连接到每个极化区域的128根天线元件,覆盖26.5 GHz至29.5 GHz频率范围。同一极化区域内的64根天线元件分别连接至一个单独的ADMV1018毫米波上/下变频器。因此,总共可以形成四个独立的波束。AiB256的一半阵列的简化框图如图3所示。

为了获得更高的EIRP,可以在中频将两组相同极化的天线(包含64根天线)组合起来,产生总共两个波束,每个波束由128根天线元件构成。该板被广泛用于支持天线校准和内部DPD算法的开发。

Sub-6 GHz和毫米波的基站设计

根据给定频率和期望的覆盖区域设计基站时,通常以波束方向图和有效各向同性辐射功率(EIRP)作为先决条件。典型的900 MHz宏蜂窝基站由一个4Tx/4Rx无线电单元(RU)构成,并连接到外部天线,如图4所示。

天线内部有两列交叉极化(±45°红/蓝)偶极子。4个RF端口中,每个端口为一列极化提供馈电。在这个示例中,信号在6个相同极化的偶极子之间以相同相位和幅度分割。在垂直方向(列)排列更多的元件,使得波束聚集在垂直面(参见图4)。这样设计是可行的,因为大部分UE都要低于天线的高度。通常会让波束以某种幅度向下倾斜,以进一步限制单元覆盖范围,避免与其他单元产生干扰。假设天线元件之间的间距为λ/2,该天线的半功率波束宽度(发射功率相对于波束峰值下降3 dB时的角度)在水平面上通常约为90°,在垂直面上一般小于20°。这种宽波束一般覆盖120°扇区,无需转向即可跟踪UE移动。天线的高度为6 × (λ/2) = 2米,宽度为2 × (λ/2) = 0.33米。假设每个偶极子单元的增益为5 dBi,那么每个极化区域的天线增益约为10 × log(12) + 5 dBi = 15.8 dBi。如果每个PA输出40 W (46 dBm)RF功率,每个极化的EIRP为46 dBm + 3 dB(2列)+ 15.8 dBi = 64.8 dBm。在900 MHz下,这种水平的EIRP应该能很好地覆盖几千米范围。

现在,我们来看看28 GHz AiB256,它的每个极化区域内包含128根天线元件,排列成8行、16列,如图1所示。假设元件之间的距离为λ/2,每个元件的增益为5 dBi,那么天线的总增益约为10 ×log(128) + 5 dBi = 26 dBi。与900 MHz示例相比,天线增益高出10.2 dB。

但是,其波束宽度变窄了。3 dB波束宽度在垂直面仅为12°,在水平面仅为6°。如此狭窄的波束根本无法一次覆盖典型的120°扇区。解决方案是:首先在单元覆盖区域内找到活动UE,将波束指向他们,然后跟踪他们在单元内的移动。5G标准指定了波束采集和跟踪程序,对此,本文不予讨论。为了计算这个无线电的EIRP,我们假设每个发射路径输出13 dBm RF功率。每个极化区域的总功率为13 dBm + 10 × log(128) = 34 dBm。加上26 dBi天线增益,每个极化的总EIRP为34 dBm + 26 dBi = 60 dBm。在典型的室外部署场景中,这个水平的EIRP在28 GHz下可以覆盖几百米范围。

DPD在Sub-6 GHz系统中的价值

5G和4G无线标准都是基于OFDM信号,它们本身具有高峰均功率比(PAPR)。为了以高保真度放大和发射这些信号,并避免污染邻近的通道,必须注意不要压缩或剪辑信号峰值。这需要以低于峰值功率6 dB至9 dB的平均功率运行该PA。在这种深度后退的状态下运行PA会导致效率极低,通常低于10%。

高效PA架构(例如Doherty)可以在低于其峰值功率6到9 dB的功率下保持高效率,但与典型的AB PA相比,它们的线性度大幅降低。如果在部署时不使用任何线性化技术,它们将无法满足应用所需的误差矢量幅度(EVM)和邻道功率比(ACPR)。DPD是最流行的线性化技术之一,广泛用于sub-6 GHz系统。

Sub-6 GHz系统要求64-QAM和256-QAM调制的EVM分别低于8%和3.5%,以符合 3GPP标准38.104。要满足这些EVM要求,信号的PAPR应保持在6 dB到9 dB之间。为了满足3GPP标准38.104,ACPR通常应小于–45 dBc。在前面的900 Mhz 4Tx/4Rx无线电示例中,每个发射器应输出40 W rms功率,如果要在线性区域中运行功率放大器,以满足EVM和ACPR要求,它们的效率通常低于10%。这意味着为了输出40 W RF功率,4个PA中的每个PA都需要消耗超过400 W直流功率。所以,单单这4个PA就会消耗超过1600 W功率!

这对无线电的尺寸、冷却、可靠性和运行成本(OPEX)有着巨大的影响。相比之下,如果使用Doherty PA,并且结合削峰(CFR)和DPD技术,那么PA效率会高于40%。这意味着每个PA消耗不超过100 W直流功率,即可输出40 W RF功率。无线电中的4个PA消耗的直流功率不到400 W。无线电的其余部分通常只会消耗不到50 W直流功率。因此,PA消耗的功率在无线电消耗的总直流功率中的占比超过85%,即使在结合使用Doherty放大器、DPD和CFR时也是如此。

毫米波阵列中DPD的实施及其价值

在AiB256中,有256个发射和接收链,能够生成2个或4个波束,每个波束中部署有128个或64个PA。与sub-6 GHz系统一样,64-QAM和256-QAM调制的毫米波频段EVM要求分别为8%和3.5%。但是,毫米波对ACPR的要求远没有sub-6 GHz频段严格;按照3GPP标准38.104,对于28 GHz频段为28 dBc,对于39 GHz频段为26 dBc。

在ADMV4828波束成型器中,每一类AB PA可提供21 dBm峰值功率。ADMV4828上的PA以大约12 dBm rms输出功率运行,可为峰值功率留出9 dB裕量,从而可满足EVM和ACPR要求。在12 dBm (16 mW)输出功率下,每个发射链消耗约300 mW功率,所以效率为5%。发射链中的一些功率是被用于波束成型的可变移相器消耗的。每条接收路径,包含可变移相器在内,消耗大约125 mW直流功率。

基于上述功率消耗,可以明显看出,与sub-6 GHz无线电相比,在毫米波无线电中,PA消耗的功率在总直流功耗中的占比要小得多。这就产生了一个问题:毫米波无线电是否仍能从使用DPD中获益?

为了回答这个问题,我们需要构建一个适用于毫米波的DPD架构。要将DPD实现方案从sub-6 GHz简单地扩展到毫米波,需要围绕每个PA建立一个DPD环路。在AiB256示例中,这意味着需要256个DPD环路!显然,实施256个DPD环路成本高昂且非常耗电。由于每个PA输出少量功率(一般为12 dBm),因此使用DPD的系统总效率很可能低于不使用DPD的系统。

幸运的是,有一个很好的办法可以解决这个问题。AiB256最多可以输出4个波束,每个波束包含64个PA(参见图3)。这意味着每个PA可以获得与其他63个PA相同的信号,除了用于波束转向的相对相移。如果单个DPD环路环绕由64个PA构成的集群,那么整个AiB256阵列只需要总共4个DPD环路。从本质上讲,DPD环路环绕每个波束,而不是环绕PA。我们将其称为阵列DPD,以便与sub-6 GHz DPD区别开来,后者的每个PA都有一个专用DPD环路。

观察接收器必须“观察”波束的视轴,所有PA的信号在此处同相叠加,所以它可以校正由64个PA的累加远场聚集所造成的失真。我们的早期评估使用远场喇叭天线作为DPD观察接收器(如图5所示),且证明可以通过在波束周围部署单个DPD环路来改善EVM和ACPR。ADI未来的产品可能包括集成观察路径,以简化DPD的实施。

DPD设置使用ADRV9029集成收发器,内置CFR和DPD功能,适用于高达200 MHz带宽的信号。ADI未来的收发器采用DPD时,将支持至少400 MHz带宽。

分析发现,在26.5 GHz至29.5 GHz的频率范围内,毫米波阵列DPD可以将波束EIRP提高3 dB左右(在1.5 dB至3.2 dB之间)。在特定频率下优化波束成型器的输出匹配和偏置设置,可以在保持EVM和ACPR规格的同时,获得高达13 dBm rms的输出功率。但是,无法在广泛的频率范围和多个单元中保持这种性能水平。或者,如果满足适当条件(PA的饱和功率电平保持在21 dBm以上),那么使用DPD可以在相关频段中稳定实现高于14 dBm的输出功率。

当指定毫米波阵列时,每个波束的EIRP就是一项核心要求。如果每个元件的功率相对较小,则需要使用多个元件来实现目标EIRP,这反过来又会使成本、功率和阵列大小增加。阵列中部署的元件越多,产生的波束就越窄。更窄的波束并非始终符合需求;它们会增大波束指向和移动用户跟踪的难度。图6中的曲线图说明了所需的元件数量和阵列直流功耗如何随着DPD从0 dB提高到3 dB而变化,同时保持目标EIRP为60 dBm不变。

如果通过应用DPD实现了3 dB EIRP改善,那么所需元件的数量会减少近30%,功耗则降低约20%。与我们的sub-6 GHz示例中采用DPD能将PA的功耗降低4倍相比,在毫米波阵列中,节能功效并不如此明显。但是,在毫米波阵列中,我们可以获得额外的优势:其元件数量减少30%,这会大大降低阵列硬件的成本和体积。未来,我们可以在毫米波波束成型中使用更高效的PA架构,利用DPD来进一步改善功效。

结论

相对于sub-6 Ghz频率,在5G毫米波阵列中实施DPD会带来新的挑战。在波束周围部署DPD环路,而不是在构成波束的单个PA周围部署,可实现阵列DPD还能带来优势。我们的分析表明,这种部署能帮助实现更高的功率输出、节省系统功率,且能减少硬件数量。但是,我们要提醒大家注意:无论是在应用中,还是在评估时,我们都需要从不同于传统sub-6 GHz的角度来看待毫米波DPD。随着毫米波PA架构日益成熟,这种定位可能会发生变化,但目前我们需要重新定义DPD应用,以及它所带来的优势。

责任编辑:haq

-

DPD

+关注

关注

3文章

40浏览量

15304 -

毫米波

+关注

关注

21文章

1927浏览量

64965 -

5G

+关注

关注

1356文章

48503浏览量

565642

原文标题:为何毫米波需要采用不同的DPD方法?如何量化其值?

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

毫米波雷达信号的传输特性

毫米波雷达的基频和调制技术 毫米波雷达在机器人导航中的应用

毫米波雷达与激光雷达比较 毫米波雷达在自动驾驶中的作用

毫米波雷达工作原理 毫米波雷达应用领域

物联网中的高分辨率精确距离测量方案_毫米波雷达

什么是毫米波雷达?毫米波雷达模组选型

毫米波雷达是声波还是电磁波

简述毫米波雷达的结构、原理和特点

毫米波雷达具有哪些特点和优势

基于毫米波雷达的手势识别算法

一文带你了解毫米波雷达

无线电将如何影响毫米波阵列中的DPD

无线电将如何影响毫米波阵列中的DPD

评论