很多小伙伴对上一篇文章讲的取对数没感觉,觉得这个没什么用。确实很多时候用不着,verilog本身不够灵活,所以很多时候我们也就没想把她写的多简介灵活,而且受限于编译器的支持,很多灵活的语法不能被编译成电路,所以有这种想法情理之中,毕竟花大把时间去玩一个函数发现他局限性很大那确实收益太少。

那么他到底有什么用?

如果大家要设计一个深度1024的fifo,那么地址位宽取多大合适?*╭︎( ˙º˙)╯︎*

当然是10位,log2(1024)

所以可以如下定义

parameter deepth = 1024;

parameter width = $clog2(deepth);

这样就把两个参数关联起来,调整代码的时候提高了可维护性也更方便。

但是到此为止了吗?

不知道大家有没有对做完fft以后取对数很苦恼,比如fft输出实部虚部各16bit,平方和开根号以后暂且也以16bit表示,那么怎么取对数呢?第一种方法是查表,第二种是传到上位机,让他处理。很多时候FPGA上确实不需要取对数这个操作,但是如果受限于高速接口,比如万兆网,pcie等接口速率希望压缩数据的时候对fft结果取对数无疑是一个很有必要的操作。毕竟log10这个对数可以把16位的数压缩到8位以内。所以查表确实可行,但是位数是24位呢,那情况就多了太多了,32位呢?

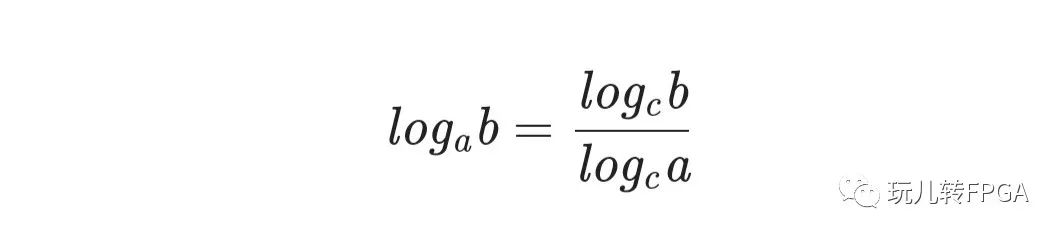

所以取对数这时候就有价值了,但是这是10为底的对数,和2为底的对数有什么关系?当然有关系,换底公式啊!

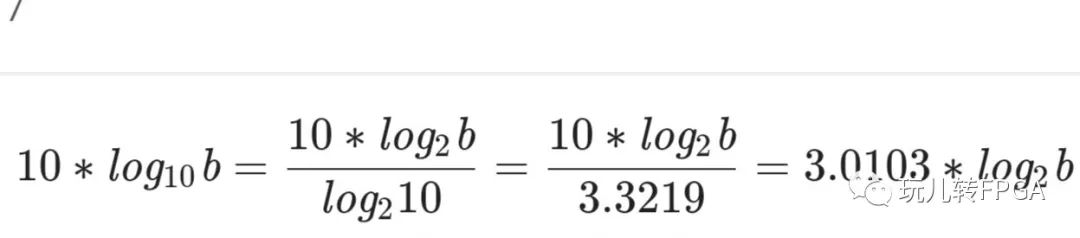

多数时候fft之后我们计算10*log10或者20*log10,那么就等价于如下操作

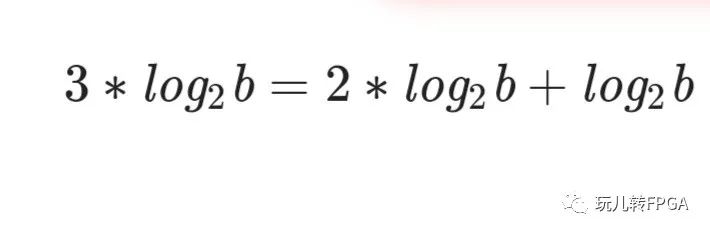

忽略3后面的小数影响的话,那么可以近似为

多震撼的结论,所以数学好真的很有必要啊!当然你想更高精度,可以对换底公式以后的分子分母同时放大10的幂次方倍,然后再往下计算,这里留给读者自行思考。

是不是很累,很复杂?

那么我告诉你,verilog2005有log10的系统函数,哈哈哈哈哈,意不意外???

责任编辑:haq

-

Verilog

+关注

关注

28文章

1351浏览量

110163 -

代码

+关注

关注

30文章

4803浏览量

68769

原文标题:log2在verilog里面到底有什么用?

文章出处:【微信号:HaveFunFPGA,微信公众号:玩儿转FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

24位或者说高分辨率的AD到底有什么用呢?

差分输入和和单端输入在本质上到底有什么区别?

无人机智能巡检系统到底有哪些作用

EWSTM8-2201 or 3101安装说明上有的说选“是”,有的说选“否”,二者到底有什么区别?对工程有什么影响?

IPv6到底有什么用,给我们生活带来哪些变化?

精密医疗器械激光切割机在医疗行业到底有多重要

log2在verilog中到底有什么用

log2在verilog中到底有什么用

评论