小技巧分享:

verilog下取对数其实可用$clog2这个系统函数,和自己找代码里面写入function是同样的效果,但是方便的多。这是verilog 2005就开始支持的标准,所以vivado也是支持的,我试了2017.4及以后的版本都可以支持,放心用。

***友情提示:所有支持verilog2005标准的编译器都可以用这个函数,所以使用之前确定编译器是否支持这个标准,还有考虑好后期可移植性的影响

这个是可编译的函数大家可以把她当做宏定义函数一样看待。这操作好玩吗?好玩就赶紧升级编译器吧,新标准总是有很多的改进,如果想了解一些更有意思的东西欢迎关注我,我是最骚的FPGAer。

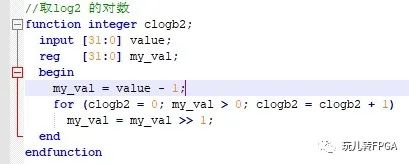

这里附上常用的自定义log2函数,供大家白嫖。图片不清晰尽请担待。

编辑:jq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1631文章

21806浏览量

606691 -

函数

+关注

关注

3文章

4350浏览量

63052 -

代码

+关注

关注

30文章

4841浏览量

69196 -

编译

+关注

关注

0文章

663浏览量

33090

原文标题:verilog2005的骚操作之对数函数

文章出处:【微信号:HaveFunFPGA,微信公众号:玩儿转FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TSC2005EVM和TSC2005EVM-PDK用户指南

电子发烧友网站提供《TSC2005EVM和TSC2005EVM-PDK用户指南.pdf》资料免费下载

发表于 12-19 15:45

•0次下载

Verilog 与 ASIC 设计的关系 Verilog 代码优化技巧

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

Verilog 测试平台设计方法 Verilog FPGA开发指南

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog测试平台设计方法及

Verilog与VHDL的比较 Verilog HDL编程技巧

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构化编程,代码更直观,易于

使用Phase Lab2024A计算示踪扩散系数的操作步骤

计算示例为Fe-Mn二元系,选择固定成分,绘制示踪扩散系数随温度的变化曲线,Mn元素为主变元素,这里取值0.2(摩尔分数),Fe为剩余元素,计算结果将通过温度的倒数1000/T为横坐标,10为底的对数函数值为纵坐标进行曲线绘制。以下是操作的分解步骤和计算结果。 ①第一步

大对数网线有8对的吗

大对数网线确实有8对的。大对数网线是一种用于大量数据传输的通信线缆,其内部包含多对双绞线,这些双绞线以特定的方式排列和绞合,以提供最佳的传输性能和抗干扰能力。 在市场上,大对数网线的对数

SUMIF函数与SUMIFS函数的区别

SUMIF函数和SUMIFS函数都是Excel中用于条件求和的函数,它们可以帮助用户根据特定的条件对数据进行求和。尽管它们的基本功能相似,但在使用场景和功能上存在一些差异。以下是对这两

SUMIF函数使用教程

SUMIF函数是Excel中非常实用的函数之一,能够根据指定条件对数据进行筛选和求和操作。以下是对SUMIF函数使用方法的详细教程: 一、基

回调函数(callback)是什么?回调函数的实现方法

回调函数是一种特殊的函数,它作为参数传递给另一个函数,并在被调用函数执行完毕后被调用。回调函数通常用于事件处理、异步编程和处理各种

发表于 03-12 11:46

•3227次阅读

verilog调用模块端口对应方式

Verilog中的模块端口对应方式,并提供示例代码和详细解释,以帮助读者更好地理解和应用。 首先,我们来了解一下Verilog中的模块和模块端口。一个Verilog模块被定义为包含一组声明和语句的代码块,类似于C语言中的

verilog中for循环是串行执行还是并行执行

在Verilog中,for循环是并行执行的。Verilog是一种硬件描述语言,用于描述和设计数字电路和系统。在硬件系统中,各个电路模块是同时运行的,并且可以并行执行多个操作。因此,在Veril

verilog task和function区别

verilog中的task和function都是用于实现模块中的可重复的功能,并且可以接收参数和返回结果。但是它们在编写和使用上有一些区别。下面将详细介绍task和function的区别。 语法结构

verilog function函数的用法

Verilog 是一种硬件描述语言 (HDL),主要用于描述数字电子电路的行为和结构。在 Verilog 中,函数 (Function) 是一种用于执行特定任务并返回一个值的可重用代码块。函数

verilog中function和task的区别

在Verilog中,Function和Task是用于模块化设计和重用代码的两种重要元素。它们允许开发人员将复杂的操作分解为更小的功能单元,并在需要时调用它们。虽然Function和Task在某些方面

剖析verilog2005的骚操作之对数函数

剖析verilog2005的骚操作之对数函数

评论