超越摩尔,三星的异构集成之路

在近期举办的2021年SamsungFoundry论坛上,三星透露了2/3nm制程工艺的新进展,并公开发布了全新的17nm工艺。三星市场战略副总裁MoonSoo Kang也面向产业合作伙伴,公布了三星在异构集成上的计划,如何为摩尔定律再度添加一个“维度”。

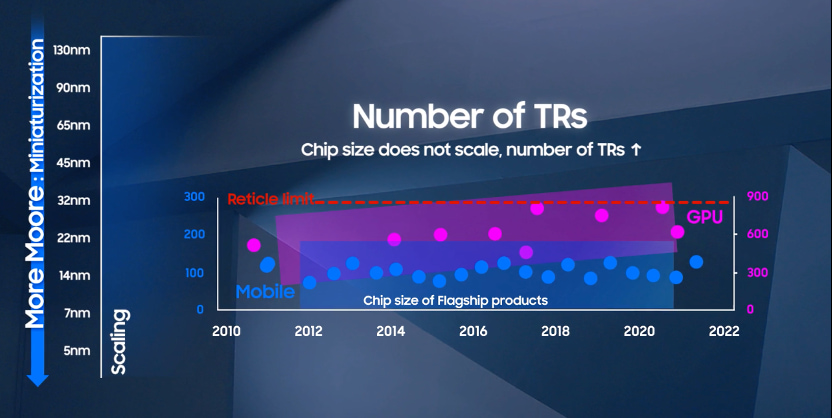

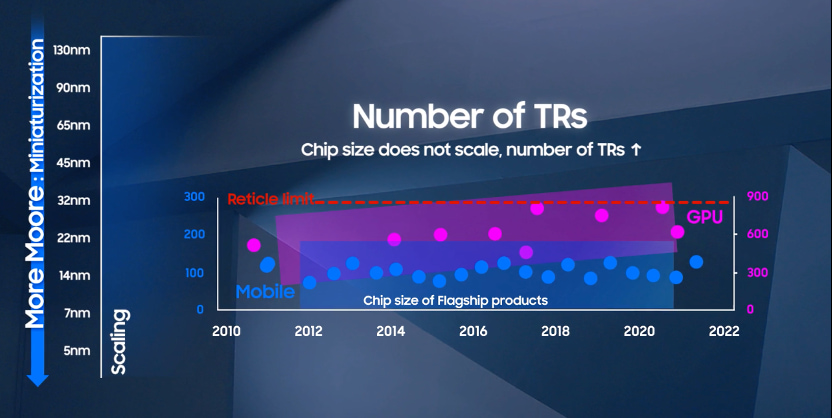

旗舰GPU与移动芯片的面积变化对比 / 三星

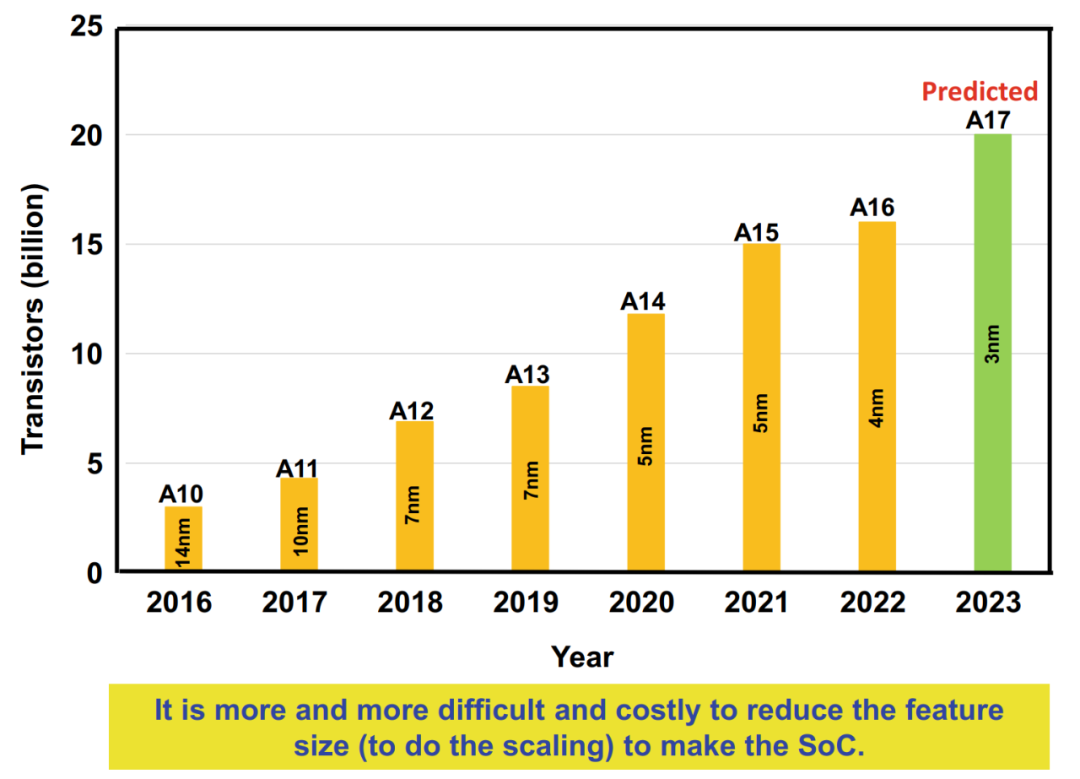

几十年间,半导体产业一直在不懈地推动摩尔定律,以更先进的制程做到更多的晶体管数目,这就是我们常说的“延续摩尔”方案,也是当前计算与电路领域持续创新最大的推动力。

尽管摩尔定律的延续,芯片面积仍在扩大,比如一直在追求算力的GPU,已经快要逼近光罩尺寸的限度了。再加上晶体管数目的增加,使得芯片设计成本和生产成本无休止地增加。在不少人看来,单靠“延续摩尔”不再是一个技术与成本上可持续的方案。

与此同时,更多的功能与特性集成在单个芯片上,却又没有单个制程可以满足所有不同功能的需求,比如模拟、射频、高压等,即便可以满足也无法达到优秀的性能与成本平衡。“延续摩尔”的方案在这类挑战面前束手无策,因此才出现了异构集成这种“扩展摩尔”的方案。通过两种方案的互补,共同做到“超越摩尔”。

Chiplet:降低成本提高良率的救星

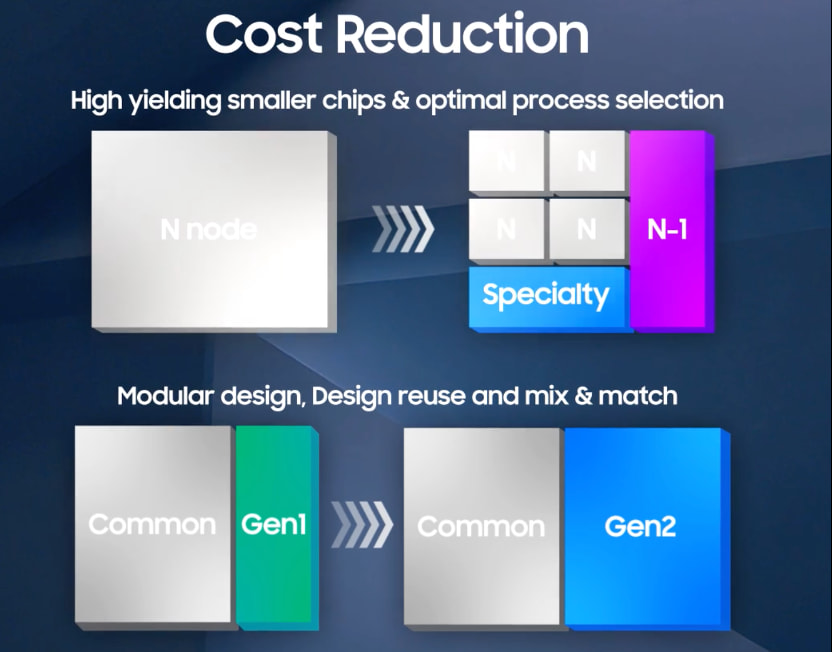

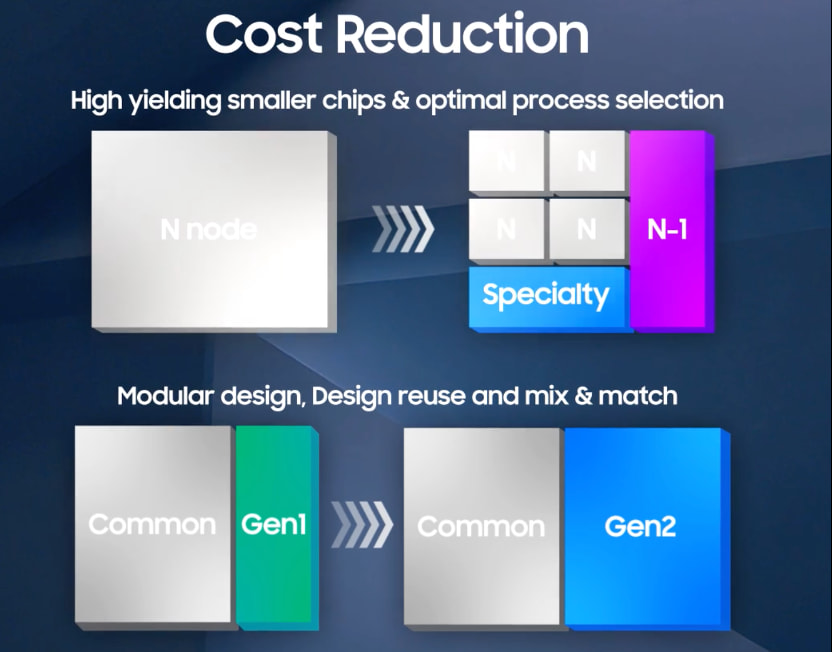

随着单个芯片加入更多特性,即便摩尔定律延续下去,其芯片面积仍在增加,为所有不同功能的设计区块使用同一个制程节点成了抵消的选择,好在如今有了Chiplet这一救星的出现。将一大块裸片分成较小的chiplet,并为每个chiplet使用最优的制程,可以显著提高整个芯片的良率,同时减少生产成本。例如某些特定的接口IP并不会因为采用先进制程而获得面积或性能上的优化,对这些IP使用成熟制程和专用定制制程,可以做到更低的成本以及更优的性能。

Chiplet方案 / 三星

另一个可行方案就是模组化的设计与制造,也就是重复使用相同的组件chiplet。不少IP模组都可以作为chiplet重复使用,只有芯片的其他部分需要重新设计和生产,此举显著减少了设计、开发与生产的成本,芯片厂商可以借此更快实现产品迭代。

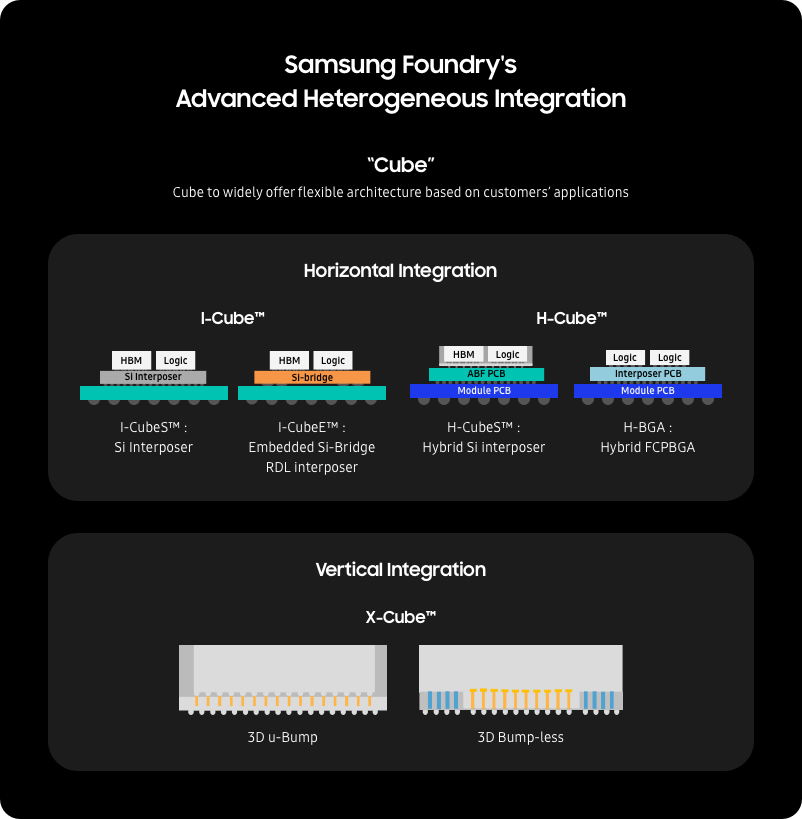

X-Cube:垂直3D集成

异构集成不只是为了成本和良率考虑,也能进一步提升芯片性能。传统的2D设计中,信号路径有几毫米长。而在3D集成下,芯片的堆叠可以将信号路径减少至几微米,大大改进了芯片延迟。除此之外,3D集成中更出色的内联间距可以实现更高的带宽,进一步提高芯片性能。

早在2014年,三星就首次实现了将宽IO内存与移动应用处理器的3D堆叠,也就是三星的Widcon技术。随后,3D芯片堆叠技术继续发展,诞生了一系列HBM内存产品。HBM就是由DRAM与逻辑堆叠,并由微凸块和TSV相连而成的。也正是因为3D堆叠技术,三星得以开发出了3层的CMOS图像传感器,由图像传感器、逻辑与DRAM三种不同的裸片堆叠在一起而成。

2020年,三星推出了X-Cube技术,这项技术使得两个逻辑单元裸片可以垂直堆叠在一起,形成一个单独的3D芯片,由微凸块与TSV连接。X-Cube分为两种形式,两个裸片由微凸块连接或是直接铜键合。

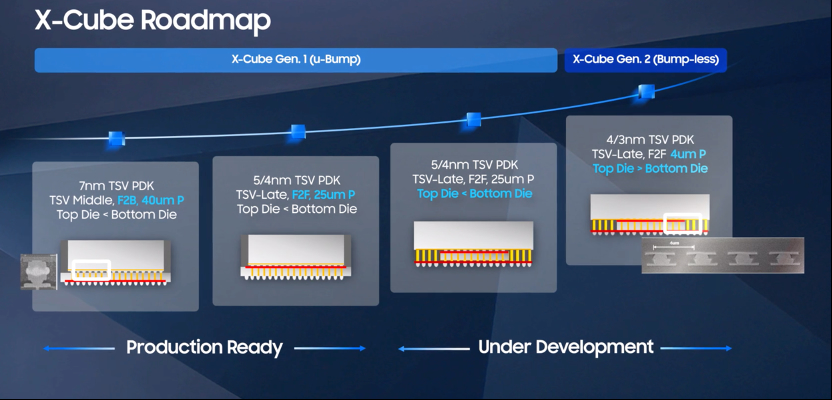

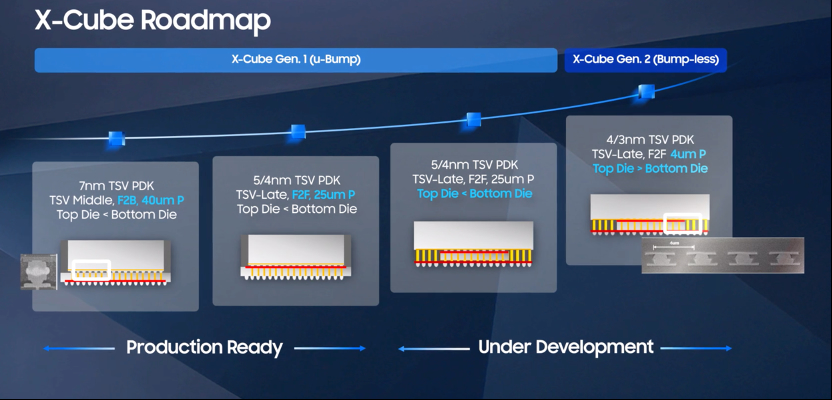

X-Cube路线图 / 三星

第一代X-Cube技术(u-Bump)主要依靠微凸块连接,三星已经发布了针对7nm逻辑制程的TSV PDK,采用F2B结构,凸块间距为40um。面向4/5nm的TSV PDK也已经发布,改用F2F的结构,凸块间距降低至25um。尚在开发中的第二代X-Cube技术(Bump-less)则采用了直接铜键合技术,间距降低至4um。

值得一提的是,英特尔的Foveros3D堆叠技术路线与三星X-Cube大致相同。第一代Foveros的凸块间距在36um至50um之间,而下一代FoverosOmni技术同样可以做到25um的凸块间距。尚在开发的Foveros Direct也采用了直接铜键合的方式,宣称凸块间距降低至10um以下。

过去的X-Cube架构中,底部裸片的面积要大于顶部裸片,然而为了更好了满足客户对芯片分区和散热等不同要求,三星也将在后续提供顶部裸片大于底部裸片的结构。目前三星已经完成了3D堆叠SRAM的验证,在7nm的制程下,可以做到48.6GB/s的带宽,以及7.2ns的读取延迟与2.6ns的写入延迟。

除此之外,三星还提供了一项差异化技术,ISC(集成堆叠电容)。这一电容应用了已经在三星DRAM产品中获得验证的硅电容结构、材料和工艺,具有1100nF/mm2的电容密度,可以有效提高电源完整性。三星的ISC还提供了多种不同的配置,比如分立型、硅中介层型和多晶圆堆叠型,以满足客户不同的结构需求,ISC预计将在2022年进入量产阶段。

I-Cube:横向2.5D组合

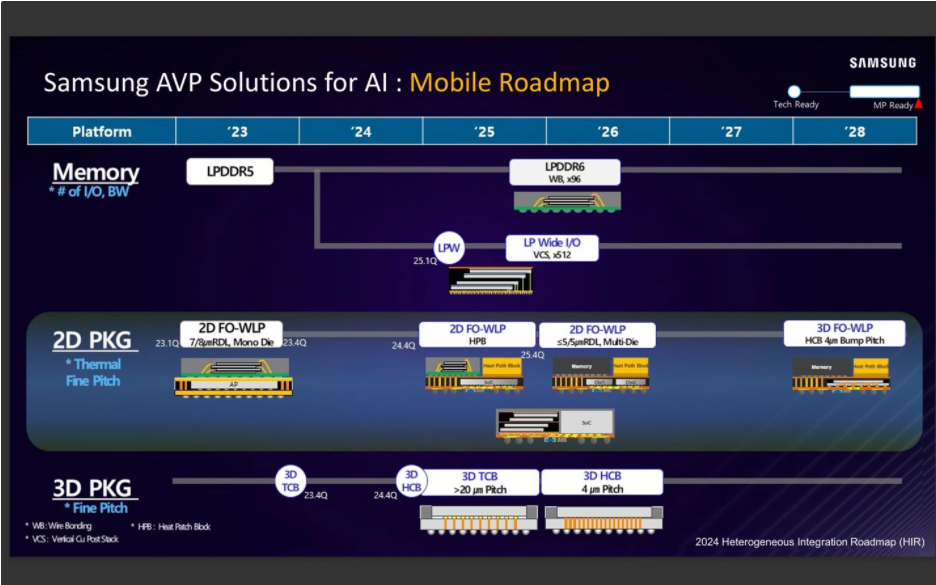

另一方面,为了从横向组合芯片,三星开发了所谓的2.5D技术I-Cube,将逻辑单元与多个HBM集成在同一硅中介层上。目前三星已经成功实现了一个逻辑裸片+两个HBM的I-Cube2量产,成品之一就是百度的昆仑AI芯片。百度的昆仑AI芯片不仅使用了三星的14nm制程,也运用了三星的I-CUBE 2技术。

I-Cube使用了预筛选的技术,在封装的中间阶段进行运算测试,从而提高良率。该技术还采用了无封胶的结构,做到更好的散热性能,据三星强调,与传统的2.5D方案相比,I-Cube的散热效率高上4.5%。此外,与其他代工厂商相比,三星的I-Cube技术还有一些优势,比如与三星内存合作,率先用上最新的内存方案

I-Cube4示意图 / 三星

目前三星已经在计划集成4HBM3模组的I-Cube4量产工作,而6 HBM的I-Cube6也已经做好量产准备,前者预计2022年进入大批量产阶段。三星更是准备了两个逻辑裸片+8个HBM的I-Cube8方案,目前尚处于开发阶段,预计2022年末将正式上线。

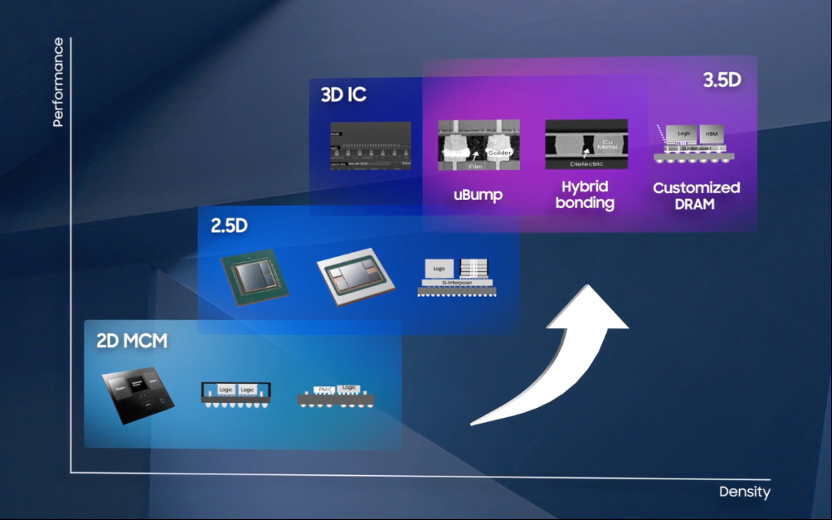

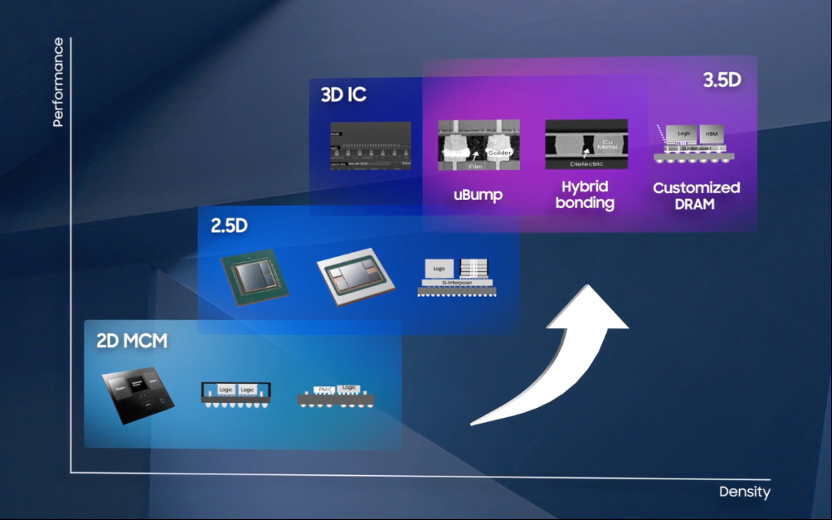

2D至3.5D的封装方案 / 三星

除了2D、2.5D与3D的IC技术之外,三星还在开发全新的3.5D封装技术,这种系统级封装内还将加入堆叠的定制DRAM或SRAM裸片,实现更高的性能与密度。

小结

在开发2.5D/3D集成的多芯片或多Chiplet系统级芯片时,设计者往往还会遇到在传统单芯片设计上罕见的技术障碍,比如多出来的接口IP或潜在的功耗增加。这时候,三星、台积电和刚进入IDM 2.0的英特尔等代工厂商还会提供异构设计的方法和工具,帮助设计者克服这些挑战。在异构集成的大势之下,代工厂也将提供更多的服务模式,增加封装、测试以及一站式的设计服务。

在近期举办的2021年SamsungFoundry论坛上,三星透露了2/3nm制程工艺的新进展,并公开发布了全新的17nm工艺。三星市场战略副总裁MoonSoo Kang也面向产业合作伙伴,公布了三星在异构集成上的计划,如何为摩尔定律再度添加一个“维度”。

旗舰GPU与移动芯片的面积变化对比 / 三星

几十年间,半导体产业一直在不懈地推动摩尔定律,以更先进的制程做到更多的晶体管数目,这就是我们常说的“延续摩尔”方案,也是当前计算与电路领域持续创新最大的推动力。

尽管摩尔定律的延续,芯片面积仍在扩大,比如一直在追求算力的GPU,已经快要逼近光罩尺寸的限度了。再加上晶体管数目的增加,使得芯片设计成本和生产成本无休止地增加。在不少人看来,单靠“延续摩尔”不再是一个技术与成本上可持续的方案。

与此同时,更多的功能与特性集成在单个芯片上,却又没有单个制程可以满足所有不同功能的需求,比如模拟、射频、高压等,即便可以满足也无法达到优秀的性能与成本平衡。“延续摩尔”的方案在这类挑战面前束手无策,因此才出现了异构集成这种“扩展摩尔”的方案。通过两种方案的互补,共同做到“超越摩尔”。

Chiplet:降低成本提高良率的救星

随着单个芯片加入更多特性,即便摩尔定律延续下去,其芯片面积仍在增加,为所有不同功能的设计区块使用同一个制程节点成了抵消的选择,好在如今有了Chiplet这一救星的出现。将一大块裸片分成较小的chiplet,并为每个chiplet使用最优的制程,可以显著提高整个芯片的良率,同时减少生产成本。例如某些特定的接口IP并不会因为采用先进制程而获得面积或性能上的优化,对这些IP使用成熟制程和专用定制制程,可以做到更低的成本以及更优的性能。

Chiplet方案 / 三星

另一个可行方案就是模组化的设计与制造,也就是重复使用相同的组件chiplet。不少IP模组都可以作为chiplet重复使用,只有芯片的其他部分需要重新设计和生产,此举显著减少了设计、开发与生产的成本,芯片厂商可以借此更快实现产品迭代。

X-Cube:垂直3D集成

异构集成不只是为了成本和良率考虑,也能进一步提升芯片性能。传统的2D设计中,信号路径有几毫米长。而在3D集成下,芯片的堆叠可以将信号路径减少至几微米,大大改进了芯片延迟。除此之外,3D集成中更出色的内联间距可以实现更高的带宽,进一步提高芯片性能。

早在2014年,三星就首次实现了将宽IO内存与移动应用处理器的3D堆叠,也就是三星的Widcon技术。随后,3D芯片堆叠技术继续发展,诞生了一系列HBM内存产品。HBM就是由DRAM与逻辑堆叠,并由微凸块和TSV相连而成的。也正是因为3D堆叠技术,三星得以开发出了3层的CMOS图像传感器,由图像传感器、逻辑与DRAM三种不同的裸片堆叠在一起而成。

2020年,三星推出了X-Cube技术,这项技术使得两个逻辑单元裸片可以垂直堆叠在一起,形成一个单独的3D芯片,由微凸块与TSV连接。X-Cube分为两种形式,两个裸片由微凸块连接或是直接铜键合。

X-Cube路线图 / 三星

第一代X-Cube技术(u-Bump)主要依靠微凸块连接,三星已经发布了针对7nm逻辑制程的TSV PDK,采用F2B结构,凸块间距为40um。面向4/5nm的TSV PDK也已经发布,改用F2F的结构,凸块间距降低至25um。尚在开发中的第二代X-Cube技术(Bump-less)则采用了直接铜键合技术,间距降低至4um。

值得一提的是,英特尔的Foveros3D堆叠技术路线与三星X-Cube大致相同。第一代Foveros的凸块间距在36um至50um之间,而下一代FoverosOmni技术同样可以做到25um的凸块间距。尚在开发的Foveros Direct也采用了直接铜键合的方式,宣称凸块间距降低至10um以下。

过去的X-Cube架构中,底部裸片的面积要大于顶部裸片,然而为了更好了满足客户对芯片分区和散热等不同要求,三星也将在后续提供顶部裸片大于底部裸片的结构。目前三星已经完成了3D堆叠SRAM的验证,在7nm的制程下,可以做到48.6GB/s的带宽,以及7.2ns的读取延迟与2.6ns的写入延迟。

除此之外,三星还提供了一项差异化技术,ISC(集成堆叠电容)。这一电容应用了已经在三星DRAM产品中获得验证的硅电容结构、材料和工艺,具有1100nF/mm2的电容密度,可以有效提高电源完整性。三星的ISC还提供了多种不同的配置,比如分立型、硅中介层型和多晶圆堆叠型,以满足客户不同的结构需求,ISC预计将在2022年进入量产阶段。

I-Cube:横向2.5D组合

另一方面,为了从横向组合芯片,三星开发了所谓的2.5D技术I-Cube,将逻辑单元与多个HBM集成在同一硅中介层上。目前三星已经成功实现了一个逻辑裸片+两个HBM的I-Cube2量产,成品之一就是百度的昆仑AI芯片。百度的昆仑AI芯片不仅使用了三星的14nm制程,也运用了三星的I-CUBE 2技术。

I-Cube使用了预筛选的技术,在封装的中间阶段进行运算测试,从而提高良率。该技术还采用了无封胶的结构,做到更好的散热性能,据三星强调,与传统的2.5D方案相比,I-Cube的散热效率高上4.5%。此外,与其他代工厂商相比,三星的I-Cube技术还有一些优势,比如与三星内存合作,率先用上最新的内存方案

I-Cube4示意图 / 三星

目前三星已经在计划集成4HBM3模组的I-Cube4量产工作,而6 HBM的I-Cube6也已经做好量产准备,前者预计2022年进入大批量产阶段。三星更是准备了两个逻辑裸片+8个HBM的I-Cube8方案,目前尚处于开发阶段,预计2022年末将正式上线。

2D至3.5D的封装方案 / 三星

除了2D、2.5D与3D的IC技术之外,三星还在开发全新的3.5D封装技术,这种系统级封装内还将加入堆叠的定制DRAM或SRAM裸片,实现更高的性能与密度。

小结

在开发2.5D/3D集成的多芯片或多Chiplet系统级芯片时,设计者往往还会遇到在传统单芯片设计上罕见的技术障碍,比如多出来的接口IP或潜在的功耗增加。这时候,三星、台积电和刚进入IDM 2.0的英特尔等代工厂商还会提供异构设计的方法和工具,帮助设计者克服这些挑战。在异构集成的大势之下,代工厂也将提供更多的服务模式,增加封装、测试以及一站式的设计服务。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

三星电子

+关注

关注

34文章

15853浏览量

180884 -

异构

+关注

关注

0文章

37浏览量

13061 -

异构集成

+关注

关注

0文章

33浏览量

1862

发布评论请先 登录

相关推荐

异构集成封装类型详解

随着摩尔定律的放缓,半导体行业越来越多地采用芯片设计和异构集成封装来继续推动性能的提高。这种方法是将大型硅芯片分割成多个较小的芯片,分别进行设计、制造和优化,然后再集成到单个封装中。

三星电子公布2024年异构集成路线图,LP Wide I/O移动内存即将面世

7月17日,三星电子公布了其雄心勃勃的2024年异构集成路线图,其中一项关键研发成果引发了业界广泛关注——一款名为LP Wide I/O的创新型移动内存即将面世。这款内存不仅预示着存储技术的又一次

三星计划2025年推出AI集成家电,与苹果角逐智能生态市场

三星电子,这家全球知名的电子产品制造商,正积极布局其家电业务的未来。据行业内部消息透露,三星的家电部门正致力于开发集成大型语言模型(LLMs)的家电产品,并计划在2025年正式发布这一系列创新产品。

华为登顶折叠屏手机市场,三星下滑

据TechInsights的最新数据,华为在2024年第一季度折叠屏手机销量大幅增长,涨幅高达257%,成功超越三星,成为全球折叠屏手机市场的领头羊。

三星电容怎么看型号呢?

现在对于三星电容的挑选型号的方式,完全要多去了解自我的需求,然后在选择适合自己型号的三星电容,这样的选择是比较合理的。那么,三星电容是怎么进行选择的呢!这些方面都是需要咱们了解清楚哦。 看三星

京东方在可折叠面板市场超越三星

根据屏幕供应链咨询公司DSCC的最新报告,京东方(BOE)已经超越三星显示(Samsung Display),成为可折叠面板市场的行业领先者。这一变化反映了市场动态和技术实力的重新布局。

三星电子在韩营业利益被索尼超越

韩国Business Korea报道指出,根据索尼2023财年预测及三星去年业绩,估计索尼的盈利额将达至1.17万亿日元(合79.5亿美元),超过三星的7.49万亿韩元(合56.2亿美元),成为自1999年以来首次超越

三星Galaxy AI集成百度文心大模型

近日,中国三星与百度智能云宣布正式结成AI生态战略合作伙伴,共同推动AI技术在智能手机等设备上的应用。作为这一合作的一部分,三星Galaxy AI深度集成了百度文心大模型的多项能力,为用户带来更加智能、高效的使用体验。

新思科技携手Ansys和三星共同开发14LPU工艺的全新射频集成电路设计

新思科技(Synopsy)近日宣布,携手Ansys 、三星半导体晶圆代工(以下简称“三星”)共同开发了面向三星14LPU工艺的全新射频集成电路(RFIC)设计参考流程

三星显示与三星半导体合作加速OLEDoS技术突破

三星正在加速进军扩展现实(XR)市场。三星电子与三星显示已开始合作开发OLEDoS(OLED on Silicon)。

三星扩建美国芯片工厂,目标2030年超越台积电

据JoongAng Daily报道,三星计划将位于泰勒市的一家半导体芯片工厂扩建为总建筑面积270万平方英尺(约2.5亿坪)。建设工作已经开始了。三星雇用当地的工程企业,正在检查工程进行情况。据泰勒市网站介绍,这座新楼目前的名称是“三星

晶圆厂拼的不只是先进逻辑工艺节点,异构集成技术不可小觑

,绝大多数厂商会选择异构集成的方式,借助先进封装技术实现“超越摩尔”。诸如台积电、英特尔等厂商,也都纷纷推出了3DFabric、Foveros之类的技术,而

超越摩尔,三星的异构集成之路

超越摩尔,三星的异构集成之路

评论