使用独立于内核的外设(CIP)构建硬件状态机

简介

状态机是逻辑单元、存储器单元和反馈的组合。状态机的输入与状态机的当前状态组合在一起,确定下一个状态。当出现状态时钟时,下一个状态成为当前状态,状态机的输出由当前状态决定。

输入 Q 与锁存器 X 的当前输出组合。其结果 g(X,Q)为下一个状态,并锁存在系统时钟的有效边沿。锁存器X 的输出也可以经过其他逻辑(变换 f)来生成输出。这种配置通常称为 Moore 型状态机。

各单元与 Moore 型设计相同,只是增加了从输入到输出的前馈路径。这种配置通常称为 Mealy 型状态机。

通常,因为单个状态可以通过前馈路径提供多个不同的输出,所以 Mealy 型状态机的状态少于 Moore 型设计。通常认为 Moore 型设计更安全,因为其输出与状态时钟同步,从而减少了状态机输出上出现逻辑条件竞争的可能。但是,Mealy 型状态机对输入变化的响应比 Moore 型状态机更快。

今天推荐的应用笔记将探讨几种使用 DMA 的可行设计,这些设计将采用上述任一配置来实现。

主要内容

Moore 型状态机(无输入变换 G)

Moore 型状态机(带输入变换 G)

使用 CLC 和端口的 Moore 型状态机设计

使用定时器外设作为状态机

使用 TMR2 和 CCP 的状态机

使用 TMR1、CCP 和 CLC 的状态机

使用水平同步时序的状态机

责任编辑:haq

-

存储器

+关注

关注

38文章

7507浏览量

163963 -

内核

+关注

关注

3文章

1375浏览量

40313 -

硬件

+关注

关注

11文章

3342浏览量

66278

原文标题:中文应用笔记《AN3398 - 使用独立于内核的外设(CIP)构建硬件状态机》

文章出处:【微信号:MicrochipTechnology,微信公众号:Microchip微芯】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请问多核DSP有几种DMA?

5416与主机通信设想通过DMA的PINGPONG模式,通过USB口传回主机可行吗?

NP+ASIC核心交换机的几种常用可行技术

ZYNQ中不同应用的DMA总结

几种DMA的典型应用场合介绍

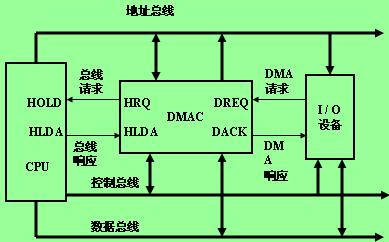

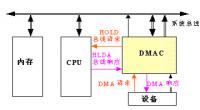

DMA与DMA控制器

DMA在实时图像处理中的应用

多SHARC系统中的DMA通信

dma是什么意思? 什么是dma?

IDC机房电源系统结构的基本原理、优缺点、实现的可行性

几种使用DMA的可行设计探讨

几种使用DMA的可行设计探讨

评论