本文介绍国产FPGA GW1NSR的片上资源和特性,从官网能获取资料的途径,完成这一步可以使读者在自己的项目遇到问题的时候能够独立解决,高云官网提供了综合用的IDE、编程下载工具,以及应用手册、数据手册和参考手册,所有资源都会附上链接。

第二章从新建工程开始一步一步的介绍如何写一个verilog文件实现一个流水灯,读者读完这章可以下载软件敲一下代码,步骤很详细,不懂在本贴下方留言。

第三章介绍IP核的使用,本次是使用片上的硬核CM3处理器,使用IP核配置工具使能SPI总线、UART和GPIO0,用于驱动spi接口的lcd,读完这章读者可以在硬核上使能自己想要的外设。

第四章介绍如何移植rtthread到硬核上。希望读完本文的读者能够基于高云的FPGA芯片和开发工具能够快速上手自己的项目。(本文为星核计划贡献者:秦韦忠作品)

GW1NSR介绍

高云方案商推出的板载GW1NSR的ministar开发板内嵌Cortex-M3硬核非常适合于verilog的学习。

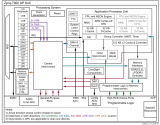

可以看到GW1NSR内嵌了一个CM3的硬核,还有一个DSP,使用verilog语言可以得到任何数字电路,FPGA一般用于IO扩展,因为数字电路是并行的,能够提升MCU的性能,片上集成了一个CM3,其优势是可以减小嵌入式产品的体积,普通采用MCU+FPGA架构的产品因为使用了分立的MCU+FPGA会增加产品体积,加上目前国内MCU的缺货现状,GW1NSR在性能上要高于普通MCU,既可以在硬核上运行串行的业务逻辑,也能用FPGA的资源实现并行的数字逻辑。想要详细的了解这颗芯片的资源,请查看芯片的数据手册。

入门:带你从新建工程到手写一个流水灯

开发环境准备

1.下载和安装软件

2.申请license

3.安装ministar的usb驱动

新建工程和创建verilog文件1.新建工程

2.新建和编写verilog文件

//author:qwz//time:2021.6.8//version:v0.1//desc:clk信号连接到硬件上的晶振,采用异步复位的方式(检测到复位引脚下降沿则执行复位动作),每有一个时钟脉冲clk,计数寄存器cnt+1,计数达到1000_0000次清零计数器,4位led左移一位。module led_flow(input clk,//时钟input rst_n,//复位按键output reg [1:0] led //4位led);reg [23:0] cnt;//时钟脉冲计数器always @(posedge clk or posedge rst_n) beginif(rst_n)cnt <= 24'd0 ;//检测到复位键下降沿清零计数器elsecnt <= (cnt == 24'd1000_0000)?(24'd0):cnt+1'b1;//计数值达到1000_0000清零计数器,否则计数值+1endalways @(posedge clk or posedge rst_n) beginif(rst_n)led <= 2'b01 ;//复位后led[0]亮,led[3:1]灭else if(cnt == 24'd1000_0000)led <= {led[0],led[1]};//计数值达到1000_0000进行4位led进行移位elseled <= led;//计数值未达到1000_0000 led不移位endendmodule

下载验证

下载完成后,此时板子上的两个LED在轮流闪烁。

实战:ip核应用之片上硬核处理器

新建工程同上章,本章主要内容为使用IP核使能片上硬核的spi外设驱动spi的lcd。

注意配置为LVCMOS33,驱动spi芯片需要3.3V电平。FPGA部分的配置就到这里,后面开始写CM3的程序。

FPGA部分的配置就到这里,后面开始写CM3的程序。

下载固件包,下载地址:

http://www.gowinsemi.com.cn/prodshow_view.aspx?TypeId=71&Id=186&FId=t3131

驱动的核心是实现spi的写寄存器和写数据函数,如下,详细驱动代码见文末的工程文件。

//用到高云mcu固件库的spi写函数SPI_WriteData(data),定义了spi的片选宏和lcd驱动的命令/数据使能宏。移植比较简单。void LCD_WR_REG(uint8_t data){LCD_CS_CLR;LCD_RS_CLR;SPI_WriteData(data);LCD_CS_SET;}void LCD_WR_DATA(uint8_t data){LCD_CS_CLR;LCD_RS_SET;SPI_WriteData(data);LCD_CS_SET;}

完成了FPGA和CM3两个部分的工作,FPGA工程综合出了fs文件、CM3工程编译出了bin文件,接着就是下载了。

此时lcd开始显示测试画面,说明驱动正常,cm3工作正常。

移植操作系统rtthread到硬核

本章内容为移植rtthread到GW1NSR的片上CM3上,让产品具有实时性。

1.下载rtthread nano 3.1.3内核源码,并复制到工程目录下。

下载地址:

https://www.rt-thread.org/page/download.html

2.在keil工程中添加源文件

3.添加头文件

4.注释掉systick、hardfault、pendsv中断

完成上面的步骤后编译工程,下载到开发板,rtthread开始在开发板上运行起来了。

总结

本次是第一次使用国产的FPGA,让我吃惊的是IP核比较丰富,这段时间在官网查资料的过程中, 我发现了riscv和arm的软核,发现有些参考手册是2018年发布的,可以知道高云在fpga已经相当长时间的技术积累,才能给用户带来方便的IDE软件和各类参考应用手册。这款ministar开发板挺适合学生使用的,希望高云推出更多这样的比赛赠送开发板给学生使用,助力verilog在我国的推广,推进我们国家数字IC的发展。

-

FPGA

+关注

关注

1664文章

22502浏览量

639176 -

操作系统

+关注

关注

37文章

7437浏览量

129616 -

SPI

+关注

关注

17文章

1900浏览量

102118

发布评论请先 登录

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:特性、参数与应用

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、特性与应用

深入解析IGLOO2 FPGA和SmartFusion2 SoC FPGA:特性、参数与应用

基于4片DSP6678+FPGA KU115 的VPX高速信号处理平台

PT153S是方寸微电子自主研发的一款全国产化USB千兆网卡芯片

Zynq全可编程片上系统详解

【PCIE044】青翼凌云科技基于 JFM7VX690T 的全国产化 FPGA 开发套件

NVMe高速传输之摆脱XDMA设计45:上板资源占用率分析

如何调用FPGA板上的按键资源的

全国产SoC片上系统无线模块技术深度解析与应用指南

如何在资源受限型应用中使用 FPGA

国产FPGA GW1NSR的片上资源和特性

国产FPGA GW1NSR的片上资源和特性

评论