随着智能驾驶和智能座舱时代到来以及AI技术的兴起,汽车智能化成为了当前全球各个企业的目标和需求导向,自动驾驶和智能座舱在当前和未来的汽车开发和应用场景中备受关注,这对AI芯片需求量大大增加,也对当前AI芯片及芯片厂商提出更高挑战。

在自动驾驶和智能座舱领域,目前英伟达、英特尔、德州仪器等不少芯片国际巨头公司已布局良久。在此背景下,国产AI芯片公司如何突破国外技术封锁?本文从国产芯片新星黑芝麻智能关于智能驾驶AI芯片的设计及制造流程来看如何实现弯道超车。

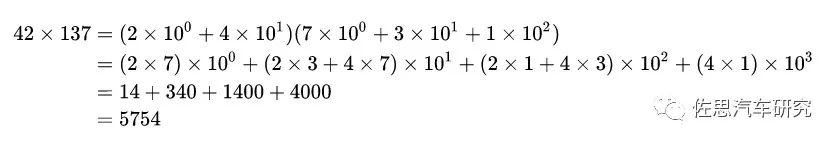

所谓AI芯片,神经网络加速器是其必不可少的一部分,目前所有的神经网络算法在硬件层面最消耗计算资源的就是乘和累加运算,即卷积,分解到硬件就是MAC(Multiply Accumulate)单元。通过这个下面公式可以说明MAC运算指令和 AI 算力之间的关系。

上面就是一个卷积,第二个等号右边每个括号里的系数构成的序列 (14,34,14,4),实际上就是序列 (2,4) 和 (7,3,1) 的卷积。所谓AI算力就是每秒执行多少万亿次指令,这些指令通常就是MAC运算的指令。

AI芯片的核心就是MAC运算单元,流程就是从内存中读取训练好的模型的滤波权重值和输入数据,两者相乘,然后重复这个流程并将乘积累加,再写入内存。

设计一款数字芯片,流程基本上是确定市场定位、确定性能与功能目标即设计规格参数、架构与算法设计、任务划分、购买IP、RTL编码与功能验证即RTL仿真、综合门级仿真、静态时序分析与仿真。这是前端工序,后端是RTL转门级网表文件、数据导入、布局规划、单元布局、时钟综合树、布线、物理验证、版图文件即GDSII交付晶圆代工厂。

也可以分为三级,第一级行为级(Behavior Level):通过行为级算法描述数字系统。也就是逻辑构思,人脑的思维流程。这一阶段主要工具为C/C++/Matlab,熟悉这些工具的人很多,很好找。

第二级寄存器传输级(Register Transfer Level):在寄存器传输级,通过寄存器之间的数据传输进行电路功能设计,例如有限状态机。工具是VHDL/Verilog/System Verilog,熟悉这些工具的人很少,这要求既要懂上层的逻辑结构,也要懂下层的电路实现。

第三级门级(Gate level):数字系统按门级(AND,OR,NOT,NAND等等…)描述。通常不会进行门级设计,门级网表一般是通过逻辑综合的输出。RTL可以用Verilog或VHDL描述。实际上还有更细分的系统级(System Level)或功能模块级(Functional Model Level)。

芯片制造流程

了解上述芯片软件设计之后,大家就会知道制作出一张芯片难点甚多,尤其在设计以及细节的把控上都是我国芯片被卡脖子的地方。对于芯片制造我们需要了解芯片的上下游,芯片的制造可以理解成点石成金的过程,只不过此处的石是硅石,其材料主要是硅。

其中最重要的是第1步二氧化硅到硅的过程,所以造芯片的第1步就是要把二氧化硅还原成硅锭,从目前所使用的工艺来看,硅锭圆形横截面的直径为200毫米。在保留硅锭的各种特性不变的情况下增加横截面的面积是具有相当大难度的。

在经过提成,去拉法等获得一根长长的硅棒,然后经过切割,切片越薄,用料越省,自然可以生产的处理器芯片就更多。切片还要镜面精加工的处理来确保表面绝对光滑,之后检查是否有扭曲或其它问题。这一步的质量检验尤为重要,它直接决定了成品芯片的质量。

研磨等制成像光盘一样的硅片,在送往晶圆厂通过光刻和石刻雕刻出晶体管的物理结构。光刻是芯片制造过程中工艺非常重要且复杂的一个步骤,光刻蚀过程就是使用一定波长的光在感光层中刻出相应的刻痕,由此改变该处材料的化学特性。

这项技术对于所用光的波长要求极为严格,需要使用短波长的紫外线和大曲率的透镜。每一步刻蚀都是一个复杂精细的过程。设计每一步过程所需要的数据量都可以用10GB单位来计量。

在残留的感光层物质被去除之后,剩下的就是充满的沟壑的二氧化硅层以及暴露出来的在该层下方的硅层。感光层同时还要被短波长光线透过掩模刻蚀。

再经过一部刻蚀,并通过离子注入和覆膜等手段赋予其电特性,掺入的物质原子进入硅原子之间的空隙,彼此之间发生原子力的作用,从而使得硅原料具有半导体的特性,在其上刻划代表着各种逻辑功能的晶体管电路。形成一张芯片,最后将它们切割分离并进行封装测试就完成了一个个芯片的制造。

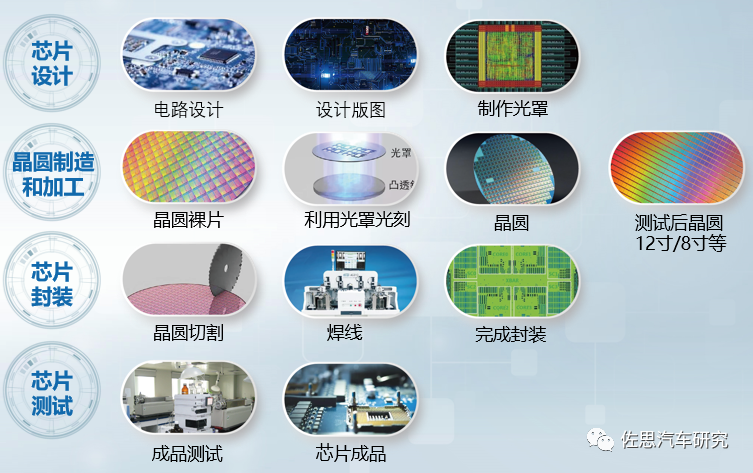

图 3 黑芝麻智能驾驶芯片制造的基本过程

上图是以黑芝麻智能驾驶芯片制造流程为例,在制造工艺流程方面简单总结为:

晶圆制造与加工:

晶圆制造:融化,提纯,拉晶获得单晶硅硅棒,对硅棒进行切片,研磨等获得晶圆。

晶圆加工:光刻改变晶圆材料的化学特性,上述设计的电路制作成一片片光罩,使用强光透过光罩后照在晶圆上,在曝光过程结束后加入显影液,正光刻胶的感光区、负光刻胶的非感光区,会溶解于显影液中。

这一步完成后,光刻胶层中的图形就可以显现出来,显影工序使将在曝光过程中形成的隐性图形成为光刻胶在与不在的显性图形。显影中进行的是选择性溶解的过程,最重要的是曝光区和未曝光区之间溶解率的比值(DR)。

下一步是刻蚀和离子注入,刻蚀对于器件的电学性能十分重要。如果刻蚀过程中出现失误,将造成难以恢复的硅片报废,因此必须进行严格的工艺流程控制。

半导体器件的每一层都会经历多个刻蚀步骤,离子注入是一种将特定离子在电场里加速,然后嵌入到另一固体材料之中的技术手段。重复这些步骤,然后就出现了一个多层立体架构,这就是目前使用的芯片的最初状态了。

芯片封装:

芯片封装是将Foundry厂生产的晶圆切割成一个个小的晶片,通过不同的封装技术对晶片进行塑封封装从而得到我们看到的芯片。

芯片测试:

芯片测试包括:良率测试,功能测试,性能测试,可靠性测试等。

芯片制造最近几年的变化随着半导体行业技术发展,工艺从微米进入纳米时代,根据行业数据来看,业界最先进的工艺制程5nm已经在2020年量产,3nm的已经进入试产阶段。

而且随着CMOS工艺的演进,栅氧厚度也要不断缩小。薄到一定厚度的栅氧就不再是理想的绝缘体,会出现明显的泄漏。在40nm进入28nm的时候,业界开始普遍采用HKMG技术。技术路线分为Gate-first和Gate-last。

工艺进入到16nm/14nm的时候,晶体管结构从2D变为3D FinFET能够带来更好的leakage current控制和更好的性能,成为先进工艺节点必选的晶体管结构。

而目前最先进的量产工艺主要是7nm/5nm,更小的pitch让EUV技术越来越成为主流TSMC从N7+开始采用EUV,最初的7nm工艺(N7/N7P)仍然采用DUV,三星则是在其第一代7nm工艺上就采用了EUV技术。

GAA(Gate All Around)的名称来自晶体管结构,这个全新设计将栅极完全包裹在通道周围,可实现更好的控制。三星相对TSMC来说,会更早采用GAA技术。TSMC则会从2nm开始采用GAA,这是未来的趋势之一。

半导体工艺的不断进步,会带来PPA(Performance Power Area)的提升,进而提升芯片以及系统产品的关键指标和用户体验,这对算力要求超高的智能驾驶芯片来说,有着决定性的影响。

对于智能辅助驾驶和智能驾驶车辆来说,车规级芯片需要复杂SOC芯片兼具高算力,高集成度,高可靠性的要求,同时需要控制芯片体积和功耗,当然还要考虑芯片发热情况。

编辑:jq

-

德州仪器

+关注

关注

123文章

2051浏览量

145695 -

Mac

+关注

关注

0文章

1131浏览量

55621 -

自动驾驶

+关注

关注

795文章

15043浏览量

181906 -

AI芯片

+关注

关注

17文章

2178浏览量

36875 -

智能座舱

+关注

关注

4文章

1375浏览量

17366

原文标题:一款智能驾驶AI芯片的设计与制造流程

文章出处:【微信号:BlackSesameTech,微信公众号:黑芝麻智能】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

P4SMA16CA 双向 TVS 瞬态抑制二极管芯片设计与制造工艺全流程解析

AI服务器PCBA加工技术解析:高算力时代的核心制造能力

【智能检测】基于AI深度学习与飞拍技术的影像测量系统:实现高效精准的全自动光学检测与智能制造数据闭环

AI质检+MES如何重构智能制造质量闭环

边缘AI算力临界点:深度解析176TOPS香橙派AI Station的产业价值

半导体制造中的“AI质检员”:一文解析 AI 如何优化芯片“出厂体检”

解析智能驾驶AI芯片的设计与制造的流程

解析智能驾驶AI芯片的设计与制造的流程

评论