编者按:

模数转换器 (ADC) 将模拟世界连接到数字世界,因此是连接到现实世界的任何电子系统的基本部件。它们也是决定系统性能的关键因素之一。本文将说明三角积分ADC如何能够生成超低噪声结果。

三角积分 (ΔƩ) 集成电路拓扑仍在模数转换器 (ADC) 中广泛使用,为过程控制、精密温度测量和称重仪应用提供高分辨率、高集成度和低功耗的解决方案。

关于这种转换器有一个令人费解的事实,它从1位转换开始,理论信噪比 (SNR) 为7.78dB,相当于5V系统中存在2V (VRMS) 噪声。在此基础之上,该ADC可发展为真正的24位三角积分转换器,提供146dB的理论SNR,相当于5V系统中存在244nV的RMS噪声。

分辨率能够从1位跃升至24位,主要依赖过采样算法、噪声整形调制器和数字滤波器来降低量化噪声并提高SNR。通过改用放大器输入级馈入12位或16位逐次逼近寄存器(SAR) ADC,这种方法可以规避ΔƩ转换器的复杂性及其相关的噪声。此设计路径行之有效,但需要在印刷电路板上使用更多的集成电路并增加BOM成本。

有一种更好的方法可以解决噪声问题:利用超低噪声ΔƩ ADC,该问题可以迎刃而解。

本文将简要讨论低噪声目标应用以及如何在内部设计ΔƩ ADC来满足这一要求。然后介绍Texas Instruments的两款ΔƩ ADC,其中一款强调24位精度,另一款强调32位精度,同时还将说明如何利用这两款产品中强大的数字滤波功能。

ΔƩ ADC的适用场景

从模拟的角度来看,工程师在测量温度、压力、测压元件和光学传感器的输出时,需要不同的精度。从根本上讲,放大器增强了设计人员量化这类较小模拟量(多数情况下接近于 DC)的能力。渐进式数字化带来了视角和功能上的变化,同时增强了存储和修改传感器信号的能力。

为实现数字捕获,典型的传感器信号路径始于传感器,经过增益、多路复用和滤波器级,然后到达ADC(图1a)。

图1a中的转换器是一个SAR ADC,可以执行12位到18位转换,并且能以高达10兆次采样/秒 (MSPS) 的转换速率运行。16位转换器可提供216,即65,536个段。在5V系统中,最低有效位(LSB) 为5V/216298,即76.3μV,理论SNR等于98dB。通过在SAR转换器之前执行模拟增益,可以实现更高的精细度。

ΔƩ信号链(图1b)利用单个转换器提高了信号链的分辨率,同时也降低了BOM成本。ΔƩ ADC可提供16位到32位转换。在此信号链中,24位ΔƩ ADC可提供224,即16,777,216个段。因此,在5V系统中,LSB为5V/224,即298nV,理论SNR等于146dB。此分辨率水平为转换器提供了更加接近传感器能力的精细度。

由于内部数字滤波器需要时间来实现滤波计算,因此24位ΔƩ ADC的速度较慢。该转换器的典型输出数据速率范围为几赫兹至1MSPS。请注意,模拟滤波器现在采用的是便宜的一阶电阻电容 (RC) 滤波器,而不是复杂的三重运算放大器五阶模拟滤波器。

这两种方法的噪声之间区别很明显:ΔƩ ADC的低噪声性能优于SARADC(表1)。

* 备注:SNR = 6.02N + 1.76,其中N是位数

在温度、压力和测压元件这类传感器解决方案中,若不太注重速度规格,但精度至关重要,那么ΔƩ ADC可提供出色的解决方案。该ADC可通过使用数字而不是模拟降噪技术,实现低至上述小电压值的转换。

ΔƩ ADC的内部构造

ΔƩ ADC的内部80%为数字构造。通常,转换器接收输入信号,并立即将该模拟信号转换为数字信号。然后,转换器将该数字信号与后续的调制器转换合并到一个数字滤波器级,在该滤波器级中,累加的1位信号变为多位。接下来,转换器通过数字输出级,以串行方式将最终的多位转换发送到等待的微控制器。

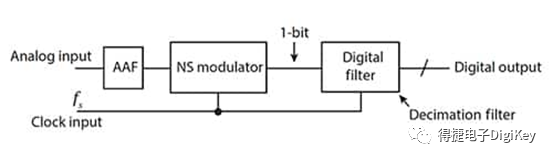

模拟信号首先通过外部的一阶抗混叠滤波器 (AAF)。然后,噪声整形 (NS)调制器获取模拟信号,并以转换器的时钟速率生成1位信号流进入数字滤波器(图2)。

图2:典型ΔƩ使模拟信号通过一阶AAF,使用NS调制器生成1位信号流,然后在连接到微控制器的数字输出端产生一个多位结果。(图片来源:CMOS:Mixed-Signal Circuit Design,2nd Edition,J. Baker,ISBN 978-0-470-29026-2)

数字滤波器按时钟输入1位信号流中的多个代码,并在数字滤波器中创建完整的多位结果。这些多位结果将通过数字输出进行串行传输。

ΔƩ调制器

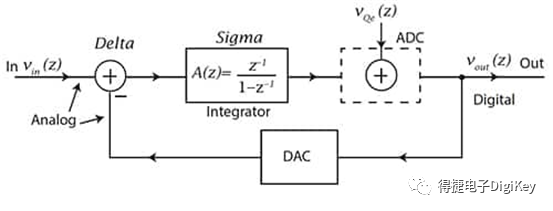

积分器/反馈回路的数量决定了ΔƩ调制器的阶数。一阶ΔƩ ADC调制器只有一个积分器和反馈环路(图3)。

图3:一阶调制器具有一个模拟积分器以及1位ADC和反馈回路中的DAC。VQe(z) 是量化ADC噪声。(图片来源:CMOS: Mixed-SignalCircuit Design,2nd Edition,J.Baker,ISBN 978-0-470-29026-2)

在图3中,模拟信号 (VIN(z)) 进入调制器的Delta(Δ) 部分。然后,模拟信号经过积分器级或Sigma (Ʃ) 级到达一个1位ADC(根据图2,采样率为fS),该ADC可以是比较器。现在,这一经过时钟数字化处理的信号反馈到1位数模转换器 (DAC),同时继续前往Δ级的VOUT(z)。1位DAC提供了一个需要从模拟输入信号VIN(z) 中扣减的模拟电压。该一阶调制器的传递函数为:

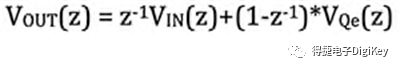

公式1

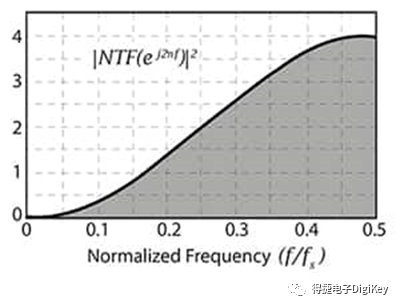

由于存在积分器和反馈回路,调制器在本身的数字输出数据流上实现了噪声整形算法(图4)。

图4:在位于ΔƩ调制器输出端的噪声整形函数中,噪声传递函数 (NTF) 等于1-z-1,其中0.5归一化频率等于FS/2。(图片来源:Understanding Delta-Sigma Data Converters, Schreier,Temes,ISBN 0-471-46585-2)

在图4中,噪声整形特性是降低转换1位量化噪声的第一步。随着噪声成功推至更高频率,由一个低通数字滤波器完成了降噪过程。

高阶调制器包含更多积分器和反馈回路。例如,三阶调制器具有三个积分器和三个反馈回路。噪声整形函数通过降低DC附近的噪声并增加整形噪声,随调制器阶数的变化而变化。

高阶调制器以增加硅硬件、降低稳定性和信号范围为代价,提供了更高的性能。

ΔƩ数字滤波器

ΔƩ ADC在运行时采用了过采样 (OS)。过采样是调制器采样率 (FS) 与ADC输出数据速率 (FD) 之比,如公式2所示:

公式2

公式2

过采样通过使用低通数字滤波器,以数字方式限制经过噪声整形的数据的带宽,来改善ΔƩ ADC的噪声。

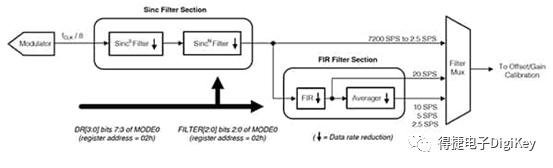

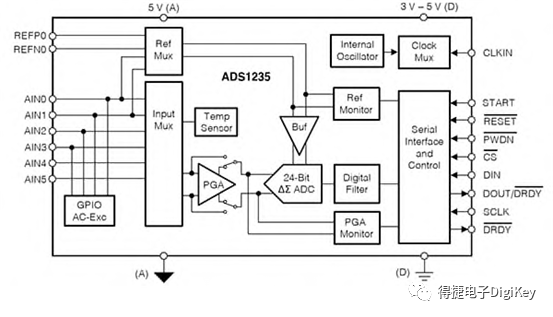

在ΔƩ ADC中,两个常用的数字滤波器是sin(pf)/pf(sinc) 和线性相位有限冲激响应 (FIR) 滤波器。在TexasInstruments的ADS1235 24位ΔƩ ADC、ADS1262和ADS1263 32位ΔƩ ADC(其中ADS1263集成了一个适用于背景测量的24位辅助ΔƩ ADC)中,数字滤波器实现提供了以下选择:专门使用sinc滤波器,或使用sinc滤波器后跟FIR滤波器的组合(图5)。

图5:ADS1235 24位ΔƩ ADC可以专门使用sinc滤波器,或使用sinc滤波器后跟FIR滤波器的组合。(图片来源:TexasInstruments)

在图5中,sinc(表示“Sinc”)滤波器是低通数字滤波器。sinc 滤波器的输出 (w(n)) 可使用公式3计算:

公式3

z域传递函数为:

公式4

频率响应为:

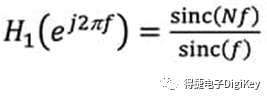

公式5

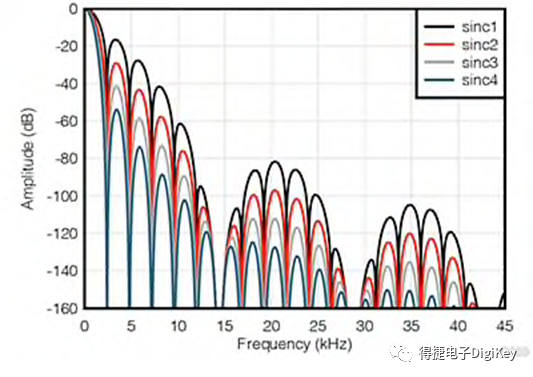

在图5中,SincN等同于串联N个相同的sinc滤波器。sinc滤波器的幅度与频率响应图形具有梳状外观(图6)。

图6:在每秒2400次采样 (SPS) 的ADS1262/63中,多个sinc数字滤波器产生了梳状频率响应;其中sinc2等效于串联两个相同的sinc滤波器,sinc3等效于串联三个相同的sinc滤波器,依此类推。(图片来源:Texas Instruments)

在图6中,峰值和零点是sinc滤波器响应的特征。频率响应零点出现在f(Hz) = N ·FD,其中N = 1, 2, 3, 。..。在零频率处,滤波器的增益为零。

sinc滤波器(串联)会增加衰减,导致延时增加。例如,如果在外部时钟速率为7.3728MHz的特定sinc滤波器计算中,产生的输出数据速率为14400SPS,则第二个sinc滤波器的输出数据速率为7200SPS。

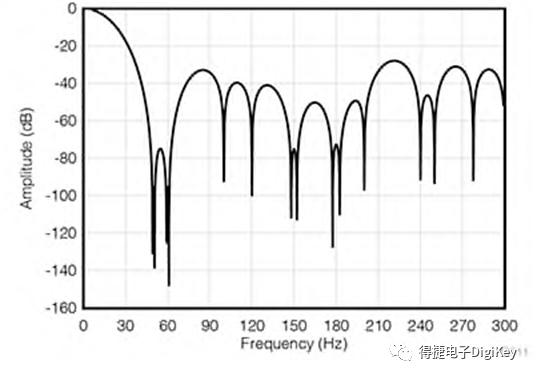

低通FIR滤波器是基于系数的滤波器。该滤波器具有50Hz和60Hz的同时衰减功能,以及2.5SPS至20SPS数据速率下的谐波功能。FIR滤波器数据速率的转换延时相当于一个周期。FIR滤波器从sinc滤波器接收经过预滤波的数据,并对数据进行抽取,以产生10SPS的输出数据速率(图7)。

图7:在ADS1262/63中,FIR滤波器可衰减50Hz和60Hz信号以降低线路频率干扰,并提供一系列靠近这些频率的响应零点。零点在50Hz和60Hz谐波处重复出现。(图片来源:Texas Instruments)

FIR滤波器会衰减50Hz和60Hz信号以降低线路频率干扰,并提供一系列靠近这些频率的响应零点。响应零点在50Hz和60Hz谐波处重复出现。

精密的低噪声ΔƩ ADC

先前提到的Texas Instruments的ADS1235差分输入24位转换器是低噪声ΔƩ ADC的极好例子。

ADS1235是一款精密的7200SPS ΔƩ ADC,具有三个差分或五个单端输入,以及一个集成式可编程增益放大器 (PGA),其增益包括1、64和128。该器件还包括诊断功能,例如PGA超量程和参考监视器。该ADC为包括称重仪、应变片和电阻式压力传感器在内的高精度设备提供了高精度、零漂移的转换数据(图8)。

图8:具有六通道模拟输入和GPIO输入多路复用器的ADS123524位ΔƩ ADC方框图。(图片来源:Texas Instruments)

对于ADS1235,影响噪声性能的重要因素包括数据速率、PGA增益和斩波模式。数据速率较慢会在数字滤波器中引入转折频率,从而降低噪声。此外,由于在斩波模式下执行的两点数据平均化,与正常操作相比,噪声降低了√2倍。

在低频、2.5SPS数据速率和1V/V PGA增益条件下,5V系统中的sinc3数字输出的转换器噪声为0.15mVRMS(0.3mV峰峰值 (PP)),有效分辨率为24位,无噪声分辨率为24位。该器件的理论和实际SNR均为146dB。事实上,在这些条件下,稳定的四阶调制器和sinc1至sinc4滤波器均可产生24位有效分辨率,以及24位无噪声分辨率。

ADS1235已针对2.5SPS数据速率实现了近乎完美的24位转换。此系列中的下一代ΔƩ ADC是TexasInstruments的ADS1262/63。这些器件之间的主要区别在于ADS1262/63改善了低噪声电路,并提供了扩展的32位输出数据寄存器。

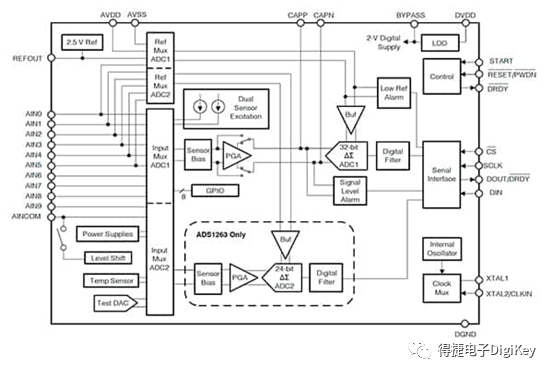

ADS1262/63具有改进的低噪声CMOS PGA,其增益包括1、2、4、8、16和32。模拟前端(AFE) 非常灵活,包含两个传感器激励电流源,非常适合直接RTD测量(图9)。

图9:具有十通道模拟输入多路复用器的ADS1262和ADS126332位ΔƩ ADC方框图。ADS1263具有第二个片上24位ΔƩ ADC。(图片来源:Texas Instruments)

与ADS1235一样,PGA增益、数据速率、数字滤波器模式和斩波模式是影响ADS1262/63噪声性能的重要因素。ADS1262/63具有32位分辨率,真正展现了低噪声深度功能。

首先,稳定的四阶调制器和sinc1至sinc4滤波器都能实现32位有效分辨率以及24位无噪声分辨率。通过配置低频率、2.5SPS数据速率和1V/V PGA增益(已旁通),5V系统中的sinc3数字输出的转换器噪声仅为0.08mVRMS(0.307mVPP)。该器件以26.9位超越了有效分辨率,以及25位无噪声分辨率。对于此32位系统,理论SNR为387dB,实际SNR等于164dB。

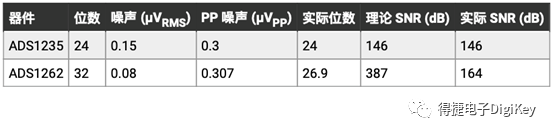

24位和32位转换器的噪声之间区别非常明显,其中32位ΔƩ ADC的低噪声性能优于24位 ΔƩ ADC(表2)。

* 备注:SNR =6.02N + 1.76,其中N是位数

表2:满量程输入电压5V的ADC RMS噪声、峰值噪声和SNR的比较结果。(数据来源:Digi-Key Electronics)

总结

ΔƩ ADC仍在不断增加功能,持续提升低噪声极限。本文介绍了如何将这种近乎数字化的低噪声ADC直接对应到温度、压力和测压元件应用中。在讨论精密型24位ΔƩ ADC和32位ΔƩ ADC的具体细节的同时,概括了实现超精密特性的途径。

责任编辑:haq

-

转换器

+关注

关注

27文章

8694浏览量

147093 -

adc

+关注

关注

98文章

6496浏览量

544473

原文标题:话说ADC之四 | 突破ΔƩ ADC低噪声性能极限,应该怎么做?

文章出处:【微信号:得捷电子DigiKey,微信公众号:得捷电子DigiKey】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

LMX2595 ramp输出8G-12G三角波,输出的扫频结果为什么不准确?

AMC1204-Q1针对电流分流测量的20MHz,二阶,隔离型三角积分调制器数据表

三角波发生器的组成和应用

求助,求推荐超低噪声跨阻放大器

ADC354x 14位10MSPS至65MSPS低噪声、超低功耗ADC数据表

三相负载与三角联结的关系

ADC3564 14位、125MSPS、低噪声、超低功耗ADC数据表

ADC358x 18位0.5MSPS至65MSPS低噪声、超低功耗ADC数据表

变压器“三角形接线”和“星形接线”接法详解

基于激光三角测距法的激光雷达原理

三角积分ADC如何能够生成超低噪声结果

三角积分ADC如何能够生成超低噪声结果

评论