CadenceLIVE China用户大会开幕,燧原科技又有两篇论文获得了本次“CadenceLIVE杰出论文奖”,其中《Tempus-PI 仿真和实测关键时序路径的一致性研究》则获得“Best Paper”的殊荣。

此外,在今天下午举行的各个技术分论坛上,燧原科技分别在“数字设计与Signoff”和“PCB、封装和系统分析”会议上发表了演讲。

Tempus-PI 仿真和实测关键时序路径的一致性研究

芯片设计向着更高的集成化、更高的频率以及更加复杂的签核 (signoff) 流程发展。其中静态时序分析 (STA) 是数字芯片设计signoff 中最关键的环节之一。对于关键路径的定位,仿真优化都是影响芯片性能的重要步骤。同时,随着芯片设计复杂化,技术节点向纳米量级发展,电源传输网络造成逻辑单元的电压降分析也变得越来越系统化,精细化。因此由于电压降引入的时序变化也越来越多的需要考量,尤其是关键路径上的电压降。

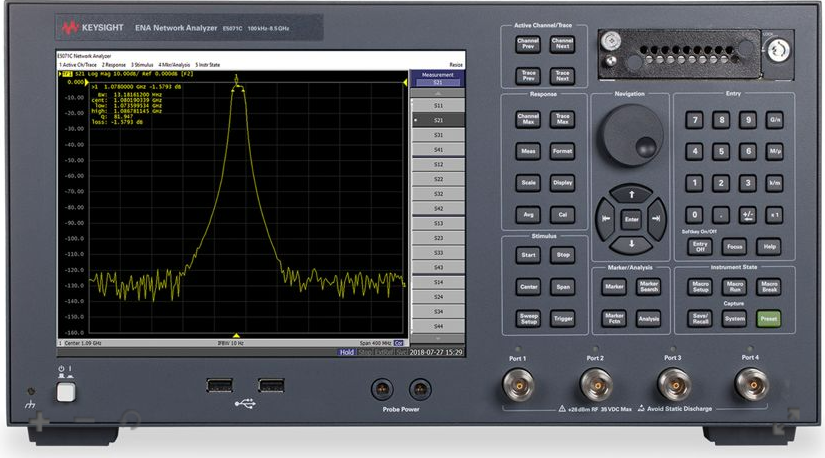

传统的静态时序分析会将电压的不一致性作为减弱参数形式,以一定的余量帮助使用者覆盖大部分真实芯片中的情况。但是随着芯片越来越大,软硬件的功能越来越多,由于电压降引起的时序违例越来越多。很多情况下IR的分析是符合标准的,现在主流的大规模芯片如AI芯片都是基于12nm、7nm或者更小的技术节点,封装还会引入3DIC,电压降分析越来越复杂也越来越重要。与此同时,时序分析也将会引入电压降的影响。Tempus-PI提供一个真正的时序和电压降协同仿真的签核流程,以此来帮助找到真正的电压敏感的关键路径。该仿真工作的结果得到了芯片测试的一致性验证。

基于信号与电源完整性的有效分析优化2.5D-3D的设计

高带宽内存 (HBM) 存储系统已成为某些超级计算机中用于高性能图形加速、网络设备以及高性能数据中心的最广泛使用的存储器件。与传统的存储器接口相比,HBM可实现更高的带宽,同时消耗更少的功耗。HBM广泛应用于高级封装中,结合中介层基板芯片 (Interposer)实现存储器的数据读写。而Interposer的设计随着HBM的速率上升,信号完整性 (SI) 和电源完整性 (PI) 带来的挑战越来越大。Interposer的设计人员在初始设计时,为了克服SI 和PI的挑战,需要有效的仿真方法学指导设计。

本文从SI和PI 角度讨论如何设计仿真,首先从信号完整性的角度讨论了设计的考量点,其次从电源完整性的角度讨论电源噪声在高速传输信号中的影响,并提出了如何仿真与预测大量同步开关噪声等电源噪声对眼图的影响,最后基于芯片的测试结果对比仿真给出结论。

责任编辑:haq

-

电源

+关注

关注

184文章

17605浏览量

249549 -

电压

+关注

关注

45文章

5567浏览量

115604

原文标题:燧原科技荣获CadenceLIVE “Best Paper Award”

文章出处:【微信号:gh_1222367b8780,微信公众号:燧原科技Enflame】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一致性测试系统的技术原理和也应用场景

电感值和直流电阻的一致性如何提高?

新品发布 | 同星智能正式推出CAN总线一致性测试系统

铜线键合焊接一致性:如何突破技术瓶颈?

为什么主机厂愈来愈重视CAN一致性测试?

锂电池组装及维修的关键:电芯一致性的重要性

QSFP一致性测试的专业测试设备

铜线键合焊接一致性:微电子封装的新挑战

企业数据备份体系化方法论的七大原则:深入理解数据备份的关键原则:应用一致性与崩溃一致性的区别

深入理解数据备份的关键原则:应用一致性与崩溃一致性的区别

Tempus-PI仿真和实测关键时序路径的一致性研究

Tempus-PI仿真和实测关键时序路径的一致性研究

评论