Cadence 和 TSMC 联手进行 N3 和 N4 工艺技术合作, 加速赋能移动、人工智能和超大规模计算创新

双方共同客户现可广泛使用已经认证的 N3 和 N4 流程 PDK 进行设计

完整、集成化的 RTL-to-GDS 流程,面向 N3 和 N4 工艺技术,旨在达成最佳 PPA 目标

中国上海,2021 年 10 月 22 日—楷登电子(美国 Cadence 公司,NASDAQ:CDNS)宣布,其数字和定制/模拟流程已获得 TSMC N3 和 N4 工艺技术认证,支持最新的设计规则手册(DRM)。通过持续合作,Cadence 和 TSMC 发布了 TSMC N3 和 N4工艺相应的工艺设计套件(PDK),以加速移动、人工智能和超大规模计算应用的创新。此外,两家公司的共同客户已经成功流片,验证了 Cadence 流程和 TSMC 工艺技术所带来的优势。

Cadence 数字和定制/模拟先进工艺节点解决方案支持 Cadence 智能系统设计(Intelligent System Design)战略,旨在系统级芯片(SoC)上实现卓越设计,如需了解更多信息,请访问:

www.cadence.com/go/advndtsmc34(复制至浏览器打开或点击文末阅读原文)。

N3 和 N4 工艺的数字流程认证

Cadence 与 TSMC 密切合作,为 TSMC 先进的 N3 和 N4 工艺技术优化数字流程,以帮助客户实现功耗、性能和面积(PPA)目标并加快产品上市。完整、集成的 RTL 到 GDS 流程包括 CadenceInnovus Implementation System 设计实现系统、Liberate Characterization Solution、Quantus Extrction Solution 寄生提取解决方案、Quantus Field Solver、Tempus Timing Sighoff Solution 时序签核解决方案和 ECO Option,以及 Voltus IC Power Integrity Solution。此外,Cadence Genus Synthesis Solution 综合解决方案和预测性的 iSpatial 技术也可用于 N3 和 N4 工艺技术。

该数字全流程使客户能够成功地基于 TSMC 的 N3 和 N4 工艺进行设计,其中包括:

高效处理大型设计库

在多种单元高度、阈值电压和驱动强度中,Cadence 流程有效地处理这些大型库,确保日益复杂的设计能够实现最佳运行时间。

时序分析准确度

N3 技术需要在库单元表征和静态时序分析(STA)期间有额外的准确性。Cadence 流程经过了加强改进,可以解决所有 N3 时序表征和签核的要求。

准确的电源签核

增加了对 N3 工艺要求的精确漏电计算和新 N3 单元的静态功耗计算的支持。N3 功耗计算的准确度包括不同的功耗成份,例如开关功耗、内部功耗和泄漏功耗,已经在多个工作工艺环境、温度和电压下得到验证。Cadence 流程符合所有 N3 电源签核的要求。

N3 和 N4 工艺的定制化/模拟工具套件认证

Cadence 持续与 TSMC 工程师的长期合作,提供全面的定制 IC、模拟、EM-IR 和混合信号设计解决方案,以解决在 TSMC N3 和 N4 工艺中,设计定制和模拟 IP 时遇到的挑战和复杂问题。通过这次合作,Cadence Virtuoso Design Platform、Spectre Simulation Platform 和 Voltus-Fi Custom Power Integrity Solution 已经达到了最新的 TSMC N3 和 N4 工艺的 PDK 要求。

N3 和 N4 工艺技术的定制 IC 设计流程包括以下设计解决方案:

Spectre Simulation Platform

提供全面的时域和频域分析能力,包括交流、直流和瞬态仿真,重点是利用 Voltus-Fi Custom Power Integrity Solution 管理大型器件和互连寄生网络、谐波平衡、噪声分析和 EM-IR。

Virtuoso Schematic Editor

提供设计捕捉,并驱动 Virtuoso Layout Suite,实现原理图驱动的版图设计。

Virtuoso ADE Suite

与 Spectre X Simulator 集成,有效的管理环境仿真、统计分析、设计中心化和电路优化。

Virtuoso Layout Suite EXL

为高效的版图实现提供了先进的版图环境,利用交互式的、辅助的性能,提升了独特的基于行的实现方法,用于布局、布线、Filler 和 Dummy 的插入。

混合信号实现流程

在 Virtuoso Design Platform 和 Innovus Implementation System 之间紧密集成,通过一个共同的混合信号开放数据库,为混合信号设计提供更强大的实现方法学,提高工程生产力。

此外,Virtuoso 和 Spectre 平台均已获得 TSMC N3 和 N4 工艺技术的认证。

“通过与 Cadence 的持续合作,我们的客户能够利用经认证的流程为我们先进的 N3 和 N4 工艺技术提高生产力。”TSMC 设计基础管理副总裁 Suk Lee 说,“TSMC 和 Cadence 的共同努力,将帮助新一代移动、人工智能和超大规模计算应用的客户,轻松地实现 PPA 目标并快速将差异化产品推向市场。”

“通过与 TSMC 的紧密合作,利用 TSMC 的 N3 和 N4 工艺技术以及我们的数字工具流程和定制/模拟流程方案,我们的客户可以获得最先进的技术和能力,打造极具竞争力的设计。”Cadence 公司资深副总裁兼数字与签核事业部总经理滕晋庆 Chin-Chi Teng 博士表示,“我们不断汲取共同客户的意见,以了解他们的实际设计要求,他们的反馈使我们能够相应地调整我们的流程,进而帮助他们实现卓越的系统级芯片设计。”

责任编辑:haq

-

TSMC

+关注

关注

3文章

177浏览量

84494 -

工艺

+关注

关注

4文章

592浏览量

28779 -

电压

+关注

关注

45文章

5598浏览量

115702

原文标题:Cadence数字和定制/模拟流程获TSMC最新N3和N4工艺认证

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

求助,关于TLV320AIC3106滤波器配置有一些疑问求解

单端正激式变换器为什么要N3线圈?

概伦电子NanoSpice通过三星代工厂3/4nm工艺技术认证

台积电N3P工艺新品投产,性能提质、成本减负

台积电升级4nm N4C工艺,优化能效与降低成本

台积电2023年报:先进制程与先进封装业务成绩

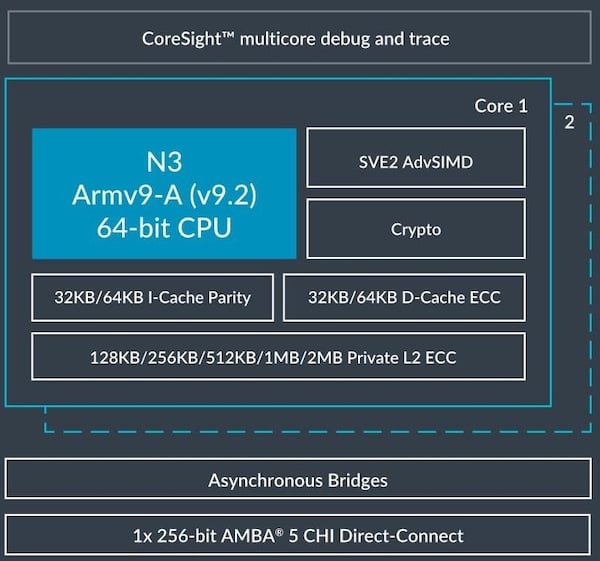

Arm新Arm Neoverse计算子系统(CSS):Arm Neoverse CSS V3和Arm Neoverse CSS N3

stm32 gpio直接驱动数码管做动态扫描没有反应是哪里的问题?

楷登电子Cadence推出业界首个全面的AI驱动数字孪生解决方案

CMOS工艺技术的概念、发展历程、优点以及应用场景介绍

Cadence数字和定制/模拟流程通过Intel 18A工艺技术认证

Arm发布Neoverse V3和N3 CPU内核

OPPO Find N3体验报告:轻薄折叠大屏,非凡旗舰影像

楷登电子数字和模拟流程获TSMC N3和N4工艺技术认证

楷登电子数字和模拟流程获TSMC N3和N4工艺技术认证

评论