对于任何一项设计,要想尽可能实现最低的功率包络,都需要在设计周期早期准确估算功耗。早期估算有助于选择合适的器件、充分发挥架构优势、更改设计拓扑,以及使用不同 IP 块。在设计阶段早期妥善权衡取舍,可以帮助用户在满足规格要求的同时,将自身产品更快速推向市场。

本文档旨在介绍如何根据 Versal ACAP 架构的描述来使用 Xilinx Power Estimator (XPE)。

UG1275

赛灵思提供了 2 种类型的功耗估算工具:通常用于在设计实现之前进行估算的 XPE,以及准确性更高、适合在设计实现期间使用的 Vivado Report Power。二者都包含丰富的功能,能够助力创建低功耗 ACAP 设计。

针对整个设计周期内的各种功耗难题,赛灵思建议采用如下功耗方法论 (Power Methodology) 解决。

在工程的概念设计和架构探索阶段,利用有限的设计架构详情来评估功耗预算至关重要。XPE 可以解决大部分早期功耗估算难题。它通常适用于工程的预设计和预实现阶段,有助于根据应用的具体需求进行架构评估、器件选择、选择合适的电源组件,以及散热管理解决方案。

XPE 能够考量使用者进行设计的资源使用情况、翻转率、I/O 负载和其它各种因素。通过将这些因素与器件模型相结合,即可计算估算的配电功耗。

保证有效执行功耗估算的设计注意事项

XPE 中的设计输入分类为以下 3 个类别:

● 设计创建:设计创建表示手动输入功耗估算,随后开始依次选择正确的器件、散热条件规格以及更重要的是,配置平台管理控制器。完成设计配置后,使用“快速估算 (Quick Estimate)”和“IP 管理器 (IP Manager)”来创建设计,然后在各块工作表上进行优化。

● 设计移植:设计移植首先需将上一代 XPE 设计 (.xpe) 导入“汇总 (Summary)”工作表。导入流程仅检索与 Versal架构相关的数据,主要是可编程逻辑 (PL) 和处理器系统 (PS) 配置。因此,它需要完成器件选择和配置,以便完成设计创建,此外还需要通过 IP Manager 或者通过在块工作表中手动输入来添加所需的新的块。

● 设计分析:设计分析因 Vivado 中创建的 Versal ACAP 设计而异,通过将设计分析导入 XPE 即可进行进一步的分析或后处理。

使用处理器系统工作表

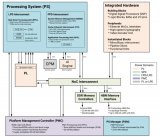

Versal ACAP 将功能丰富的 64 位双核 Arm Cortex-A72 和双核 Arm Cortex-R5F 处理器系统 (PS)、赛灵思可编程逻辑 (PL) 架构以及 AI 引擎 (AI Engine) 全都集成到单一器件内。

低功耗域和全功耗域

处理器子系统 (PS) 工作表分为 2 个域:低功耗域 (Low Power Domain) 和全功耗域 (Full Power Domain)。这些功耗域可开启和关闭。以下图例分别展示了低功耗域和全功耗域。

处理器和 PLL

Versal 架构的 PS 为全功耗域集成了功能丰富的 64 位双核 Arm Cortex-A72 (APU),并为低功耗域集成了双核 ArmCortex-R5F (RPU) 处理器系统 (PS)。在全功耗域中可使用 APU PLL 来为 Arm Cortex-A72 核、L2 高速缓存、FPD 互连结构和 CCI 生成时钟。在低功耗域中可使用 RPU PLL 来为 Arm Cortex-R5F 核、TCM、OCM 和 LPD 互连结构生成时钟。

注:使用 A72 时,必须启用 L2 高速缓存,XPE 会自动将其启用并向 FPD 添加电源。

存储器和 I/O 接口

Arm Cortex-A72 和 Cortex-R5F CPU 系统还包含片上 TCM、OCM 存储器、L2 高速缓存和丰富的外设连接接口。

高速缓存一致性互连 (CCI)

所谓 CCI 表示将部分互连和一致性功能组合到一起的块。“负载 (Load)”字段值取决于应用,范围为 0% - 100%。此Load 值与“互连负载 (Load for Interconnect)”值相同。允许的最大频率与对应速度等级的 APU 频率范围相同。

责任编辑:haq

-

赛灵思

+关注

关注

32文章

1794浏览量

131253 -

XPE

+关注

关注

0文章

7浏览量

11060 -

ACAP

+关注

关注

1文章

54浏览量

8162

原文标题:XPE 助力设计早期准确功耗估算

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何通过PMC_GPIO唤醒AMD Versal™ Adaptive SoC Linux系统

使用 AMD Versal AI 引擎释放 DSP 计算的潜力

使用AMD Versal AI引擎加速高性能DSP应用

AMD推出第二代Versal Premium系列

ALINX VERSAL SOM产品介绍

一个更适合工程师和研究僧的FPGA提升课程

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

AMD发布第二代Versal自适应SoC,AI嵌入式领域再提速

AMD Versal SoC刷新边缘AI性能,单芯片方案驱动嵌入式系统

在Vivado中构建AMD Versal可扩展嵌入式平台示例设计流程

AMD Versal AI Edge自适应计算加速平台之PL LED实验(3)

AMD Versal AI Edge自适应计算加速平台PL LED实验(3)

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal AI Edge自适应计算加速平台之Versal介绍(2)

如何根据Versal ACAP架构的描述来使用XPE

如何根据Versal ACAP架构的描述来使用XPE

评论