一、前言

I2C总线是由Philips公司开发的一种简单、双向二线制同步串行总线。它只需要两根线即可在连接于总线上的器件之间传送信息。

二、I2C总线开发设计需要注意点

1、总线容量及驱动能力

I2C总线的外围扩展器件都是CMOS器件,总线有足够的电流驱动能力,因此总线上扩展的节点数不由电流负载能力决定,而由电容负载确定。

总线上每个实际节点器件的总线接口都有一定的等效电容,等效电容的存在会造成总线传输的延迟,导致数据传输出错。

通常总线负载能力为400pF,通常各个I2C器件都会有它自己的电容值,一般为不大于20pF,据此可计算出总线长度及节点数目的限制数量。总线上的每个外围器件都有一个器件地址,因此总线上扩展外围器件时也要受器件地址限制。

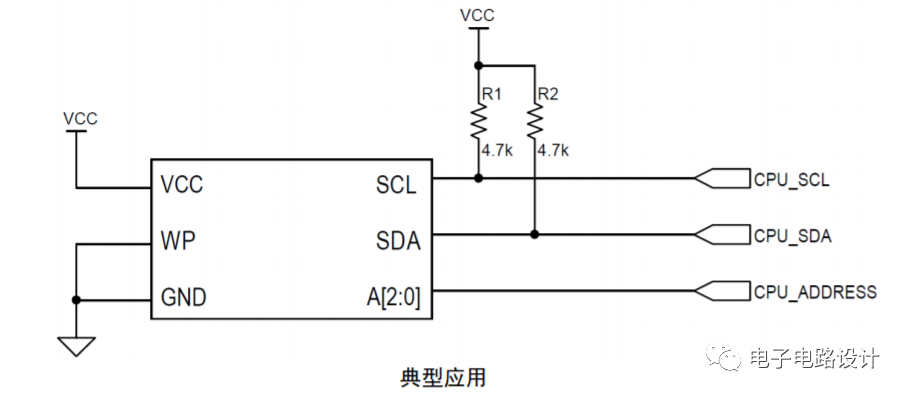

2、I2C总线的电气结构

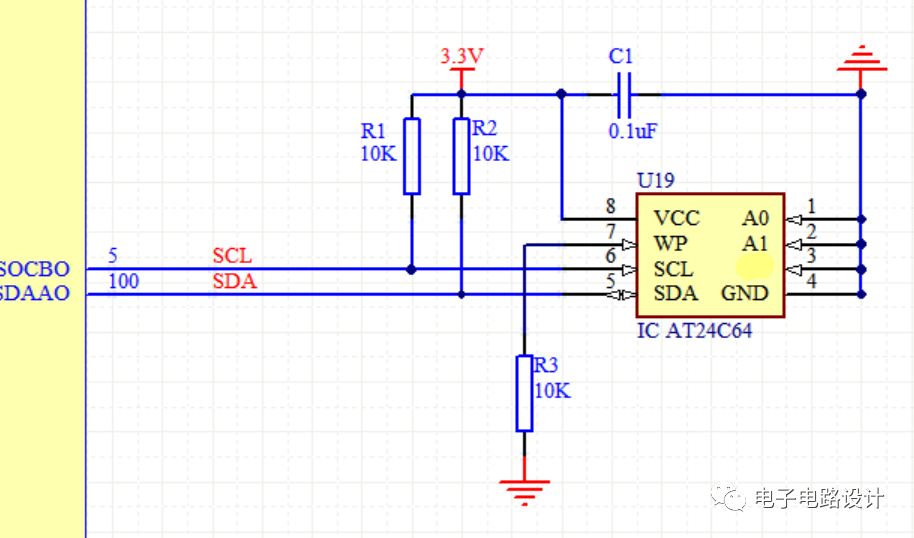

I2C总线为双向同步串行总线,因此I2C总线接口内部为双向传输电路,如图。所示。总线端口输出为开漏结构,故总线上必须有上拉电阻,上拉电阻与电源电压、SDA、SCL以及总线串接电阻有关,可参考有关数据手册进行选择,通常可选4.7K到10K。

3、每个节点都有一个固定的节点地址。

I2C总线为双向同步串行总线,因此总线上的单片机都可以成为主节点,其器件地址由软件给定,存放在总线的地址寄存器件中,称为主器件的从地址。在总线的多主系统中,单片机作为从节点时,其从地址才有意义,所以总线上所有的外围器件都有规范的器件地址。

4、I2C总线时序

I2C总线上数据传递时,总线上传送的每一帧数据均为一个字节。但启动总线后,传送的字节数没有限制,只要求每传送一个字节后,对方回应一个应答位。在发送时,首先发送的是数据的最高位。每次传送开始有起始信号,结束时有停止信号。在总线传送完一个字节后,可以通过对时钟线的控制使传送暂停。

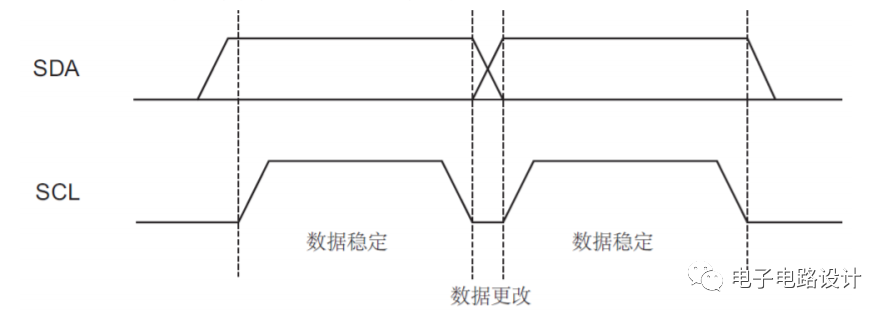

①时钟和数据发送:

SDA引脚通常使用外部设备拉高。SDA引脚上的数据只能在SCL为低电平时进行更改,SCL为高电平时数据更改将指示开始或停止条件。如图所示。

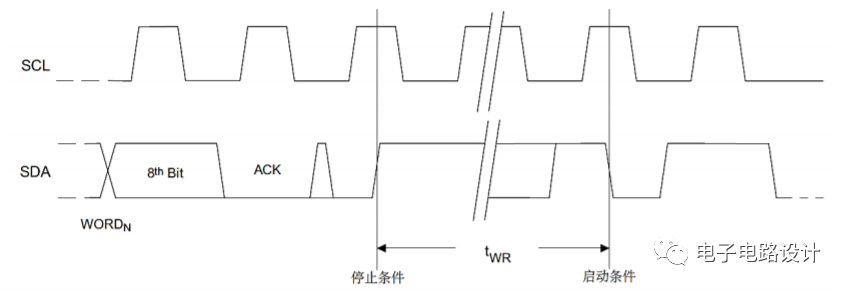

②起止条件:

SDA由高到低且SCL为高是启动条件,必须先于任何其他命令。SDA由低到高且SCL为高是停止条件,在一个读序列后,停止命令会使EEPROM进入待机模式。如图所示。

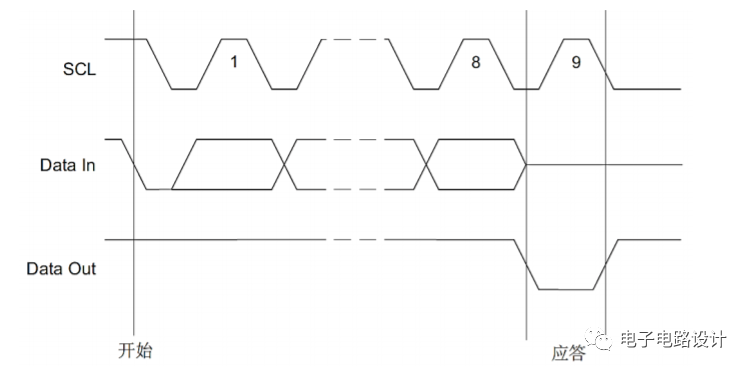

③应答:

所有地址和数据字均以8bit字连续传输到EEPROM,EEPROM发送一个“0”来应答,以确认它已收到每个字。应答发生在第九个时钟周期如图所示。

三、设计实例

我们对于AT24C256肯定不会陌生,这是ATMEL公司256kbit串行电可擦的可编程只读存储器,8引脚双排直插式封装,具有结构紧凑、存储容量大等特点,可以在2线总线上并接4片该IC,特别适用于具有高容量数据储存要求的数据采集系统。

EEPROM存储器设备既可以接收又可以发送数据。每个挂接在总线上的器件都有唯一一个地址识别。

主机访问EEPROM时,主机在向EEPROM发送完控制字节和地址信息后,紧接着向EEPROM存储器发送起始条件和控制信号并发送读标志位信号,切换数据的收发方向。接着在收到EEPROM的响应信号后便可以读出需要的数据了。

四、总结

通过以上实例,我们可以知道I2C优点主要表现在:

1、简化了硬件电路。在这种总线中只需要两根线,即串行数据线(SDA)和串行的时钟线(SCL)。

2、每个挂在总线上的I2C器件都有一个唯一的地址,并可以通过软件寻址。

3、因为在总线上可能有多个主I2C器件,因此I2C总线接口协议中有冲突监测和仲裁机制,以防止通信中的数据丢失或发生错误。

4、这种串行的两线双向的总线在标准模式下的速率为100kbit/s,在快速模式下的速率为400kbit/s,在高速模式下为3.4Mbit/s。

5、I2C器件中有滤波抗扰措施来保证数据的完整性。

6、在总线上挂接的器件数目是有限的,即总线上的容抗不能超过400pF。

编辑:jq

-

存储器

+关注

关注

38文章

7538浏览量

164521 -

传输电路

+关注

关注

0文章

10浏览量

10739 -

I2C总线

+关注

关注

8文章

406浏览量

61235 -

SDA

+关注

关注

0文章

124浏览量

28313

原文标题:什么是I2C总线,它有着哪些特点,设计时需要哪些细节呢?

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

I2C总线通信原理 如何设计I2C总线电路

基于I2C总线的智能家居应用

I2C总线的优缺点分析

如何选择I2C总线拉电阻

I2C总线与Arduino的接口示例

I2C总线的工作模式介绍

I2C总线协议详细解析

I2C总线故障排除技巧

I2C总线与单片机的连接

I2C总线与SPI总线的比较

I2C总线上拉电阻阻值如何确定?

什么是I2C总线 I2C总线开发设计需要注意点

什么是I2C总线 I2C总线开发设计需要注意点

评论