损耗的定义

损耗与效率为了更好地理解,我们来看一下效率的定义、以及效率与损耗之间的关系。效率是输出功率与输入功率之比。这是因为在将输入功率转换为所需的输出时会产生损耗。所以,如果用比例来表达损耗的话,可以用几个公式来表示,比如效率的倒数;功率值的话则是输入功率减去输出功率后的值等。

效率=输出功率÷输入功率 [%]损耗=1-效率 [%]损耗=输入功率―输出功率[W]损耗=输出功率×(1 效率)÷效率 [W]

损耗与结温提起为什么需要对损耗进行评估和探讨,这是因为损耗会转换为发热量。也就是说,重要的最大额定值—结点(Junction,芯片)温度,在确认是否在规定值内,是否在可使用的条件内时,发热量是重要的探讨事项。结温Tj通过以下公式来表示。

Tj [℃]=Ta [℃]+(θj-a [℃/W]×損失 [W])

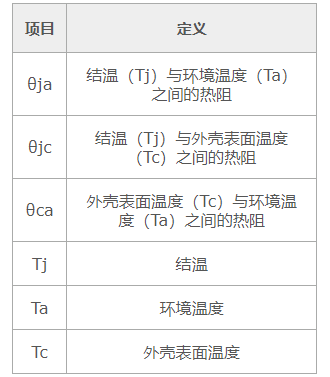

在这里特意用括号将“θj-a [℃/W]×损耗 [W]”项括起来了,该项即表示“发热量”。即“环境温度Ta+发热量”为Tj。下面是封装的热阻及其定义。

热阻θj-a因封装和安装PCB板条件而异。通常,在各IC的技术规格书中会给出标准值。

发生部位

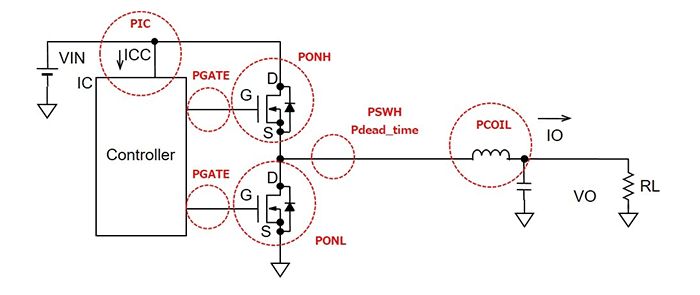

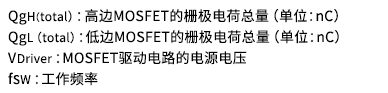

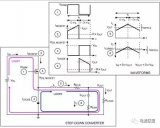

下面是同步整流降压转换器的电路简图以及发生损耗的位置。关于发生位置,用红色简称来表示。

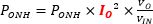

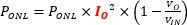

PONH是高边MOSFET导通时的导通电阻带来的传导损耗,也称为“导通损耗”。

PONL是低边MOSFET导通时的导通电阻带来的传导损耗。

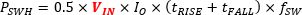

PSWH是MOSFET的开关损耗。

Pdead_time是死区时间损耗。当高边和低边MOSFET同时导通时,VIN和GND处于接近短路的状态,并流过称为“直通电流”等的过电流。为了避免这种情况,几乎所有的控制器IC在高边和低边的导通/关断切换时,都会设有两者都关断的一点点时间,这就是“死区时间”。为了安全起见是需要死区时间的,但会成为损耗。

PIC是电源用IC(在这里为功率晶体管外置同步整流降压转换器用控制器IC)的电源电流。基本上是IC本身消耗的电流,是自身消耗电流。

PGATE是外置MOSFET的栅极电荷损耗。原则上MOSFET的栅极是不流过电流的,但需要用来驱动栅极电容的电荷,这会成为损耗。需要同时考虑高边和低边。

将这些损耗全部加在一起就是同步整流降压转换器的损耗。

损耗合计:

P=PONH+PONL+PSWH+Pdead_time+PIC+PGATE+PCOIL

PONH:高边MOSFET导通时的导通电阻带来的传导损耗

PONL:低边MOSFET导通时的导通电阻带来的传导损耗

PSWH:开关损耗

Pdead_time:死区时间损耗

PIC:自身功率损耗

PGATE:栅极电荷损耗

PCOIL:电感的DCR带来的传导损耗

同步整流降压转换器的传导损耗

输出端MOSFET的传导损耗

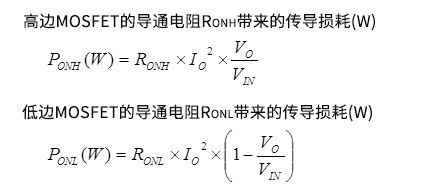

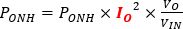

输出端MOSFET的传导损耗是高边和低边MOSFET导通时的导通电阻(RDS(ON))带来的,也称为“导通损耗”。在这里使用以下符号来表示。

PONH:高边MOSFET导通时的导通电阻带来的传导损耗。

PONL:低边MOSFET导通时的导通电阻带来的传导损耗。

导通电阻是表示MOSFET特性的重要参数之一,并且MOSFET一定存在导通电阻。因此显而易见,具有电阻的导体中会有电流流过,而这部分会产生损耗。

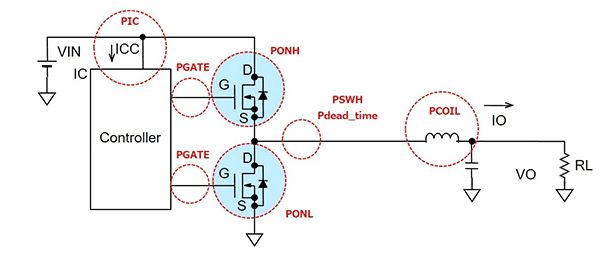

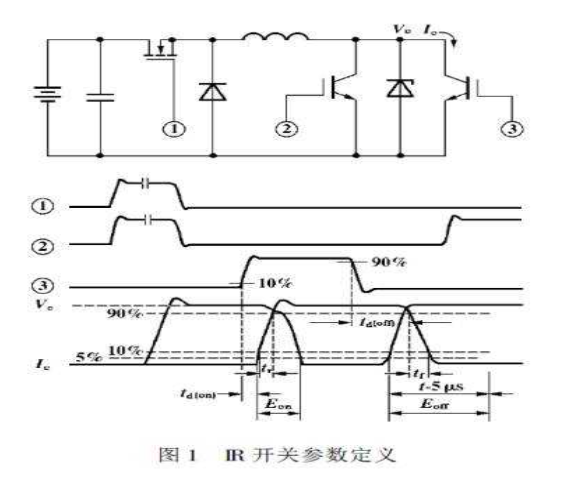

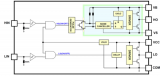

下面来求MOSFET的传导损耗。下面电路图中的IONH(红色)表示高边MOSFET导通时的电流。IONL(蓝色)为低边MOSFET导通时的电流。波形图中的LX是开关节点的电压波形,IONH和IONL是伴随着开关的各电流波形,IL是电感电流,这是一个标准型示例。

在同步整流中,高边开关导通时低边开关会关断,低边导通时高边会关断。开关节点波形的红色部分表示流过IONH,蓝色部分表示流过IONL。也就是说,这期间流过MOSFET的电流和MOSFET的导通电阻带来的功率损耗成为各自的传导损耗。以下为计算公式示例。

可以看出,结果是根据欧姆定律,I2、R乘以导通期间后的值。电流模型使用了平均电流Io。

顺便提一下,在二极管整流(非同步整流)的情况下,同步整流的低边MOSFET仅成为二极管,因此可以用同样的思路来求损耗。二极管中没有“导通电阻”这个参数,因此根据正向电压Vf计算。在这里由于电压(Vf)是已知的,因此可以通过V、I来计算。另外,当开关为双极晶体管时,也可以按照和二极管相同的思路根据VCE来计算。

在实际的计算中重要的是:导通电阻的值根据Io值中的导通电阻来计算。一般情况下在MOSFET的技术规格书中会给出导通电阻RDS(ON)和IDS的曲线图,可以利用这些数据。二极管的Vf和双极晶体管的VCE也同样可以使用技术规格书中给出的数据。

同步整流降压转换器死区时间的损耗

死区时间损耗

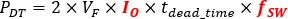

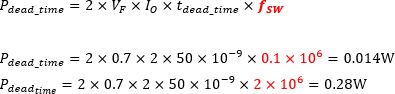

死区时间损耗是指在死区时间中因低边开关(MOSFET)体二极管的正向电压和负载电流而产生的损耗。在这里使用Pdead_time这个符号来表示。

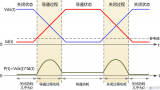

同步整流方式是高边开关和低边开关交替ON/OFF。理想的开关状态是两边的开关不会同时ON或同时OFF。然而在实际运行过程中这种理想状态是很难的,而且,为了安全运行还特意设置了两边开关同时OFF的期间。将这个期间称为“死区时间”。这里提到“为了安全运行”是因为如果两边的开关同时ON的话,通常会有被称为“直通电流”、“Shoot Through”、“Flow-through Current”等的电流通过高边开关和低边开关从VIN流向GND。很容易想象,这与VIN和GND短路的状态几乎相同,大电流流过,开关MOSFET可能损坏。为了避免这种情况,会在同步整流式DC/DC转换器IC中配置一种控制电路,使两边的开关不同时导通(ON),即两边先关断(OFF)之后相应的开关导通。

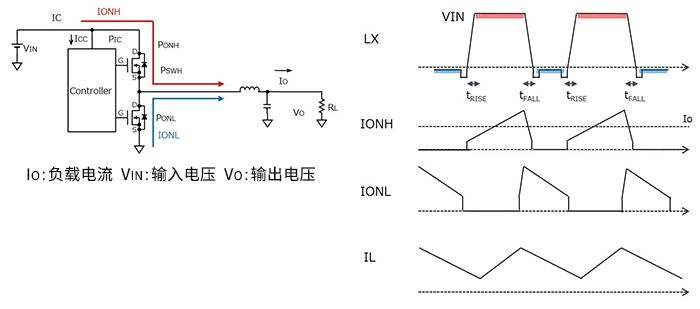

下面再回到死区时间的话题。在死区时间内,两边的开关是OFF的,所以无论从哪边开关到输出端应该都不会有电流流过。然而,实际的开关是MOSFET,MOSFET中有被称为“体二极管”的寄生二极管。下图中连接在MOSFET漏源极之间的二极管就是体二极管。

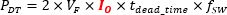

两边的开关为OFF状态时,低边MOSFET的体二极管相对于负载电流是正向的,电流通过这个体二极管流向负载。该损耗=Pdead_time可利用下列公式计算出来。

从公式中可以看出,无论哪项越小损耗都会越少。IC的死区时间控制是设置为确保安全、损耗最小的时间。

同步整流降压转换器的控制IC功率损耗

控制IC的自身功率损耗

在该例中,使用同步整流式控制IC、即未内置功率开关的控制器型IC作为电源用IC。控制电源电路用的IC也需要电源来运行,当然也会消耗电力,而且,其功耗也会成为损耗的一部分。即上图中的PIC。

在这里,我们来探讨电源IC在纯粹的控制工作中消耗的电力。这是因为控制IC含有用来开关外置MOSFET的栅极驱动器,通常,当功率开关连续开关时,栅极驱动器的功耗占主导地位。因此,在电源始终供给相应的负载电流的应用中,控制IC自身的功耗通常不会造成什么问题。然而,在轻负载时的间歇工作和周期非常长的PFM工作中,IC自身的功耗占主导地位,对效率会产生巨大影响。所以,当需要考虑轻负载时的效率时,就需要把握IC自身功耗带来的损耗。

计算公式非常简单。这是IC最简单的功耗计算,但可能需要进行一些探讨。

为了确保与其他部分之间的整合性,这里给出了开关的波形,不过有的IC的技术规格书中给出的测量条件,可能是停止开关的条件。

另外,由于IC引脚的关系,控制电路用的电源引脚和栅极驱动器用的电源引脚可以是分开的或复用的。GND也一样。区分自身功耗和驱动器功耗有时并不容易。不管怎样,都需要参考技术规格书中自身消耗电流相应的项目条件进行测量。

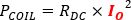

同步整流降压转换器的栅极电荷损耗

功率开关MOSFET的栅极驱动相关的损耗,即下图的高边和低边开关的“PGATE”所示部分。

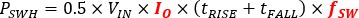

栅极电荷损耗

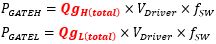

栅极电荷损耗是由该例中外置MOSFET的Qg(栅极电荷总量)引起的损耗。当MOSFET开关时,电源IC的栅极驱动器向MOSFET的寄生电容充电(向栅极注入电荷)而产生这种损耗(参见下图)。这不仅是开关电源,也是将MOSFET用作功率开关的应用中共同面临的探讨事项。

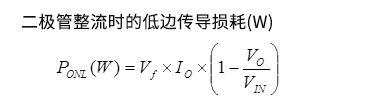

损耗是MOSFET的Qg乘以驱动器电压和开关频率的值。Qg请参考所使用的MOSFET的技术规格书。驱动器电压或者实测,或者参考IC的技术规格书。

从该公式可以看出,只要Qg相同,则开关频率越高损耗越大。从提供MOSFET所需的VGS的角度看,驱动器电压不会因电路或IC而有太大差异。MOSFET的选型和开关频率因电路设计而异,因此,是非常重要的探讨事项。

为了确保与其他部分之间的一致性,这里给出了开关的波形,但没有表示栅极电荷损耗之处。

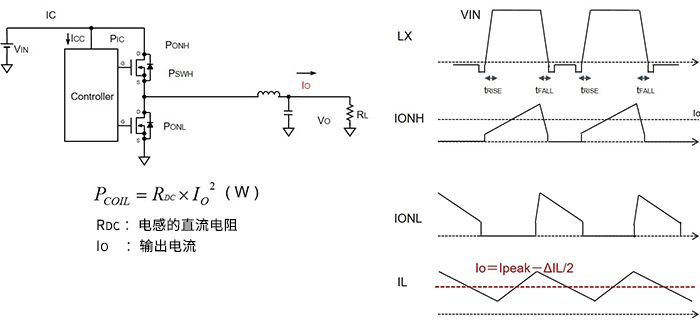

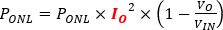

电感的DCR带来的传导损耗

输出电感DCR相关的损耗,即下图中浅蓝色的“PCOIL”所示的部分。

电感的DCR带来的传导损耗

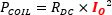

电感的DCR(即直流电阻)是线圈的电阻。所以,只是因流过电感的电流和DCR而产生损耗。损耗发生的位置也只是电感本身。所流过的电流基本上是输出电流Io。Io可根据电感电流IL求得。

无需赘述,需要根据欧姆定律计算。

电源IC的功率损耗计算示例

此前计算了损耗发生部分的损耗,本文将介绍汇总这些损耗并作为电源IC的损耗进行计算的例子。

电源IC的功率损耗计算示例(内置MOSFET的同步整流型IC)

图中给出了从“电源IC的损耗”这个角度考虑时相关的部分。本次以输出段的MOSFET内置型IC为例进行说明。相关内容见图中蓝色所示部分。电感除外(因为电感是外置的)。如果计算此前的说明中使用的控制器型IC的损耗的话,是不包括MOSFET和电感损耗的。

要计算损耗时,需要有单独计算时公式各项相应的值。原则上使用技术规格书中给出的值。

一般情况下,技术规格书的标准值(即IC参数的值)中,包括最小值、典型值、最大值。有些参数只有最小值或最大值,或只有典型值,并非所有的参数都具备这三种值。

关于应该使用这些值的哪个值,可能会有不同的看法,但我认为应该考虑到值的变化/波动,计算最差条件下的损耗。

此次将使用上图给出的值。这些均是以最差条件为前提的值。计算步骤是先按照每种损耗的公式计算各自的损耗,然后再将损耗结果相加。

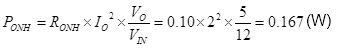

① 高边MOSFET的传导损耗

② 低边MOSFET的传导损耗

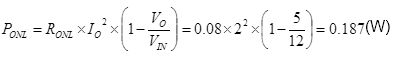

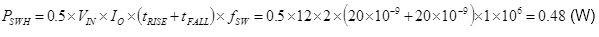

③ 高边MOSFET的开关损耗

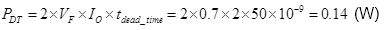

④ 死区时间损耗

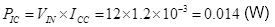

⑤ IC控制电路的功率损耗

⑥ 栅极电荷损耗

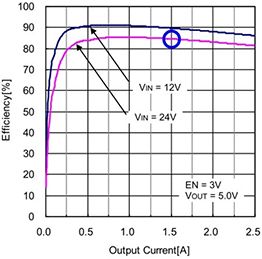

电源IC的功率损耗总和:

在本示例中,电源IC的功率损耗约为1W。只要用于计算的数据完整,功率损耗计算并不难。

损耗的简单计算方法

在很多情况下,电源IC的技术规格书中给出的是在标准的应用电路中测试得到的效率曲线图(效率 vs 输出电流)。如果所使用的电路条件与规格书中的效率曲线的条件相同或近似,则在自己设计的电路中也可能得到基本相同的效率曲线。利用这个效率曲线,可以简单计算损耗。这里也以内置MOSFET的同步整流降压转换器为例进行计算。

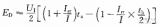

首先,请看根据效率计算损耗的公式,这同时也是为了整理效率和损耗的关系。

输入功率 [W]=输出功率[W]+损耗[W]效率(×100,以“%”表示)=输出功率[W]÷输入功率[W]损耗 [W]=输出功率[W]×(1-效率)÷效率

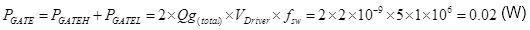

接下来,根据下面的条件,使用效率曲线进行计算。

使用条件:Vin=24V,Vout=5V,Iout=1.5A

从曲线图中可以看出效率为:84%(蓝色圆圈)

损耗 [W]=输出功率[W]×(1-效率)÷效率 =(5V×1.5A)×(1-0.84)÷0.84=1.43W

这里计算出的损耗是电路的损耗(效率也一样),因此,需要减去外置输出电感的DCR带来的传导损耗(PCOIL)。

如上所述,可以根据效率曲线大致算出损耗。前面提到要减去外置电感的损耗,但更准确一点讲,估算值中包含其他外置部件和PCB的薄膜布线等的损耗。然而,由于电源IC本身的损耗比这个值小(通常只是很小的值),因此用于估算值的量并没有什么问题。

功率晶体管为外置的情况下,可以用相同的思路估算,但一般需要另行求出功率晶体管的损耗,因此所花的时间也可能与单独计算差不多。

最后,计算值的小数原则上要向上舍入,而非向下舍入。至于使用到小数点后几位数,可根据整体的功率来判断有效(有影响)的位数。这是为了将误差控制在安全范围,需要注意的是损耗和发热等负面因素。当然,在进行可否判断时需要考虑到余量而非界限值。

封装选型时的热计算示例1

从本部分开始,将介绍根据求得的损耗进行热计算,并判断在实际使用条件下是否在最大额定值范围内及其对应方法等。原本之所以求损耗(效率),是为了确认最终IC芯片和晶体管芯片的结温Tj未超出最大额定值,并确认电源电路在要求条件下准确且安全地工作。

使用在“电源IC的功率损耗计算示例”中计算得到的结果。为方便起见,下面给出计算损耗时的条件和损耗的计算结果。

电源IC的功率损耗总和:

如右表所示,输出电流IO为2A。工作环境温度Ta为最高85℃。在这样的条件下,电源IC的封装考虑采用HTSOP-8封装。HTSOP-8是标准的表面贴装型SO封装,是背面露出金属板的封装类型。

热计算说到底是求IC芯片的结温Tj。在IC的技术规格书中,多会提供容许损耗曲线图,容许损耗最终也会归结到Tj。下面是Tj的计算公式。不难看出这个公式并非特殊的公式,而是普遍的用来表示Tj的公式。

Tj=Ta+θja×P

Ta:环境(周围)温度 ℃

θja:接合部-环境间热阻 ℃/W

P:消耗(损耗)功率 W

热阻值是计算所需的信息。多数情况下会在IC的技术规格书的条件中有提供。下表是从技术规格书中摘录的。此外,这里还提供了这些条件下的容许损耗曲线图。

从所提供的内容可以看出,热阻θja因安装PCB板的层数而异。本文中的假设前提为1层PCB,因此使用“条件①”来计算。

Tj=Ta+θja×P⇒85℃+189.4℃/W×1.008W=275.9℃

Tjmax为150℃,因此从计算结果看严重不符合。先在公式中试着代入数值进行了计算,在列举条件过程中就可以看出其结果。在容许损耗曲线图中,一个损耗1.008W的线已经超出了①条件下的容许范围。另外,Ta=85℃的线与①的交点,表示①的条件下的容许功率,可以一目了然地看出,1.008W已经远远超过这个范围。进一步讲,当知道θja为189.4℃/W时,损耗1.008W的话仅发热量就能超过Tjmax的150℃限值,这种条件下是无法实际使用的,这在计算前就已经看出来了。

不过,通过该计算可以明白“将什么、做到怎样的程度、如何做比较好”,因此还是有必要计算的。

封装选型时的热计算示例2

“封装选型时的热计算示例1”的结果,实际上无需探讨也知道275.9℃相对于Tjmax=150℃来说是严重不合格的。

本次将基于上次的结果,在上述另一个PCB板条件②下进行计算。

PCB板②:4层PCB(2、3层铜箔,背面铜箔74.2mm×74.2mm)

条件②:θja=40.3℃/W

Tj=Ta+θja×P⇒85℃+40.3℃/W×1.008W=125.6℃→Tjmax=150℃以下,结果OK

在条件②下,得益于4层PCB的散热效果,热阻从189.4℃/W降至40.3℃/W,降低了近4/5,因此,即使是Ta=85℃的条件,相对于Tjmax来说也具有约24℃的余量。这也可以从上述容许损耗曲线图中来确认,图中红色虚线所示的1.008W的线和Ta=85℃线的交点,位于条件②的容许损耗曲线内侧。

这证明希望使用的封装HTSOP-8是可以使用的,但需要采用4层的PCB。

虽然这两次的示例有点极端,但通过这样的计算和经验积累,很快就会锁定所需的大致条件。但是,要想拿出具体结论,计算损耗功率并进行热计算当然是不容忽视的步骤。

损耗因素

上文介绍过在电源电路的很多部位都会产生损耗,整体损耗的构成部分–特定部位的损耗在某些工作条件下会增加。所以需要先认识到工作条件是造成损耗增加的因素之一。下面汇总了与条件相关的造成损耗的因素,同时还给出了损耗的计算公式,这样可以更明确地理解其关联性。

随着负载电流  的增加而增加的损耗因素:

的增加而增加的损耗因素:

高边侧的MOSFET导通电阻  带来的传导损耗

带来的传导损耗

低边侧的MOSFET导通电阻  带来的传导损耗

带来的传导损耗

电感(线圈)的DCR  带来的导通损耗

带来的导通损耗

随着频率  的提高而增加的损耗因素:

的提高而增加的损耗因素:

栅极电荷损耗

受负载电流  和频率

和频率 两者影响的损耗因素:

两者影响的损耗因素:

开关损耗

Dead Time损耗

这些是和电源电路的规格变更和条件变动有关的因素。只要理解了这些关系,就可以明白探讨规格和条件变更时的注意要点。

通过提高开关频率来实现小型化时的注意事项

在开关方式的DC/DC转换器电路中,如果提高开关频率,就可以降低外置电感和电容器的值,也就是说,就可以使用更小形状、更小封装的电感和电容器,使电路所需的安装面积变小,从而可实现设备的小型化。这是在小型便携设备中常用的方法。

上文中介绍过,受开关频率 fSW 影响的损耗因素主要有三项:①栅极电荷损耗、②开关损耗、③死区时间损耗。

针对这些因素,下面来计算一下当开关频率提高时,实际会增加多少损耗。条件使用“电源IC的功率损耗计算示例”中使用过的右侧条件。将开关频率从0.1MHz提高到2MHz。

下面是各计算公式和实际的计算值。栅极电荷损耗为H和L之和。

<随着频率  的提高而增加的损耗因素>

的提高而增加的损耗因素>

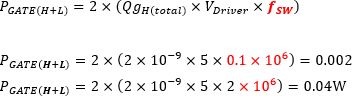

①栅极电荷损耗

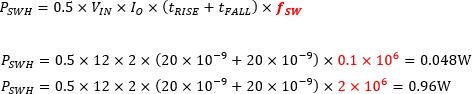

②开关损耗

③死区时间损耗

从计算公式可以看出,由于开关频率 fSW 从0.1MHz提高到2MHz(20倍),几种功率损耗也直接提高了20倍。然而,从整体功率损耗中每个值的比例来看,②开关损耗和③死区时间损耗占主导地位。下图是相对于开关频率的每种损耗数据。

如果用具体的数值来表示整体损耗,那就是:开关频率0.1MHz时损耗为0.632W,开关频率1MHz时损耗为1.208W,开关频率2MHz时损耗为1.848W,很明显随着开关频率的提高,损耗也在增加。

再计算一下效率:输出功率为10W(5V/2A),输入功率为输出功率+损耗功率,因此在0.1MHz时效率为94.1%,1MHz时效率约为89.2%,2MHz时效率为84.4%,在实际上可能发生的从1MHz到2MHz的变化过程中,效率下降达4.8%。

考虑因素及对策

提高开关频率可使用更小型的外置电感和电容器,从而可进一步实现电源及应用的小型化。然而,提高开关频率后,开关损耗和死区时间损耗随之增加,效率随之下降。也就是说,提高开关频率所带来的小型化和损耗增加(效率下降)之间,存在着此起彼消的矛盾关系。

作为其对策方案是基于应用的要求,在可接受的损耗(效率)和尺寸范围进行平衡来设置开关频率。如果是尺寸为第一优先要素,则采用最快的开关频率;如果是效率为第一优先要素,则选择最慢的开关频率。不过很多情况下是综合衡量尺寸和效率,取折中方案。

高输入电压应用时的注意事项

对于DC/DC转换器的输入电源来说,通常工业设备的12V总线等几乎是恒定电压,而汽车的电池电压等虽然标称12V,但需要考虑到瞬态波动等因素,设想相当宽范围的电压进行设计。

本文将在此前提到的条件(输入电压12V,最高达60V)下来探讨效率。

在“损耗因素”一文的公式中提到,输入电压的升高能够对效率造成影响的是“开关损耗”。

<随着输入电压 VIN 的升高而增加的损耗因素>

开关损耗:

从公式可以看出,开关损耗随VIN的升高而增加,由于是乘法算式,因此将会造成很大的影响。

下面来实际计算一下当VIN为12V和60V时的损耗。

PSWH(12VIN)=0.5×12V×2A×(20 nsec+20 nsec)×1MHz=0.48W

PSWH(60VIN)=0.5×60V×2A×(20 nsec+20 nsec)×1MHz=2.4W

VIN升高了5倍,所以计算后开关损耗也增加了5倍。下图为相对于输入电压的整体损耗变化示意图。基本上开关损耗是主要增加的损耗。

考虑因素及对策

要将输入电压范围扩展为12V~60V,需要对当初选择用于12VIN的MOSFET重新评估包括额定电压(耐压)在内的几项规格。以下汇总了重新评估要点和注意事项。

在使用开关晶体管(MOSFET)外置的控制器IC的案例中,重新评估MOSFET的额定电压(VD)。

开关损耗会增加,因此MOSFET的容许损耗也需要重新评估。

随着MOSFET的变更,探讨采用tr和tf更快且导通电阻和Qg低的产品。

电源规格中,如果能够降低开关频率就将其降低。如果将fSW减半(降至500kHz),则损耗也会减半。

如果是开关晶体管内置型的IC,则需要对IC本身进行评估。

至此仅考虑了损耗方面的因素,其实在涉及更高输入电压时,还有一项考虑因素。虽然并非本文的主题内容,但在现实中是非常重要的,因此在这里提一下。

应该是将最大60VIN降压至5VOUT,但降压比受电源IC的控制参数之一的最小导通时间的限制,故必须对降压比和最小导通时间进行探讨。由于降压比是60:5,按开关频率1MHz进行简单计算的话,需要能够控制周期1µs的1/12、即83.3ns的导通时间的电源IC。然而,现实中最小导通时间83.3ns以下的电源IC并不多。在ROHM的产品中,DB9V100MUFF这款电源IC可以满足该条件,但在多数情况下,很多产品因无法满足最小导通时间要求而被迫降低开关频率。如果降低开关频率,则不仅需要重新确认损耗,其他相关的所有元器件常数等都需要重新确认。但在车载设备中,基本上都要求2MHz以上的开关频率,因此无法通过降低开关频率来解决该问题。

综上所述,在探讨高电压应用时,需要考虑到降压比和损耗增加这两方面的因素。

高输入电流应用时的注意事项1

在此前使用的条件中,设想输出电流的范围为1A~5A。

随着输出电流增加而增加的损耗有低边/高边MOSFET的导通电阻损耗、开关损耗、死区时间损耗以及电感的DCR损耗。

下面是“损耗因素”中列出的各损耗公式。

<随着输出电流  的增加而增加的损耗因素>

的增加而增加的损耗因素>

・高边侧的MOSFET导通电阻  带来的传导损耗

带来的传导损耗

・低边侧的MOSFET导通电阻  带来的传导损耗

带来的传导损耗  ・开关损耗

・开关损耗  ・死区时间损耗

・死区时间损耗  ・电感(线圈)的DCR

・电感(线圈)的DCR  带来的导通损耗

带来的导通损耗

从公式中可以看出,MOSFET的导通电阻和电感的DCR损耗尤为增加。由于Io为二次方,因此1A时为1,但5A时变为25,与其他损耗相比,其系数变为5倍。下面是当Io从1A变为5A时的各损耗示意图。

考虑因素及对策

MOSFET的导通电阻带来的传导损耗是损耗增加的主要因素,因此在开关MOSFET外置的控制器IC配置的情况下,应选择导通电阻低的MOSFET。如果是MOSFET内置型IC,则基于同样的观点,应选择内置MOSFET的导通电阻小的IC,但由于没有单独选择MOSFET的选项,因此需要对比整体的损耗进行选择。

电感的DCR损耗也很大,因此需要选择DCR小的电感。在IC组成的电源电路中,一般情况下电感为外置,因此与MOSFET外置型和内置型的思路相同。

关于开关损耗,选择tRISE和tFALL较快、即MOSFET的开关速度快的产品可抑制开关损耗。基本上需要选择Qg低的MOSFET。另外,控制器IC的栅极驱动能力高也可有效抑制损耗,但本次使用IC本身的条件。有的MOSFET内置型IC是以高速开关为特点的。

此次的条件设置中,是以不改变开关频率为前提的,不过也有通过降低开关频率来降低损耗的手法。但是,这与电感的大小之间存在矛盾平衡关系。

死区时间损耗是死区时间中因低边MOSFET的体二极管的正向电压VF和Io而产生的损耗,因此理论上应该使用缩短死区时间、体二极管的VF小的MOSFET。然而,在大多数情况下,死区时间是按控制器IC优化的值设置的,是无法调整的,而且根据死区时间来选择控制IC的做法也不太现实。此外,对于MOSFET也是一样,寻找体二极管的VF小的产品也并不现实。如果无法容忍死区时间损耗,可以通过在低边MOSFET的漏极-源极间增加VF小的二极管(如肖特基二极管)来降低VF。另外,虽然这种方法与本次的条件不符,但还可以通过降低开关频率的方法来处理。

最终需要使用导通电阻低的MOSFET,提高开关速度,并选用DCR低的电感。但是,关于MOSFET的选型还有一些需要探讨的事项,相关内容将在“其2”中进行说明。

高输入电流应用时的注意事项2

如上文中所介绍的,要想提高输出电流,需要使用导通电阻小的MOSFET。然而,高耐压且低导通电阻的MOSFET通常会具有较大的栅极电容,并且往往具有较高的Qg,因此,需要注意栅极电荷损耗。

下面将在此前使用的条件下,在栅极电荷Qg具有从1nC到50nC的范围条件下,来探讨损耗。

・栅极电荷损耗

下图表示Qg和损耗之间的关系。当Qg增加时,栅极电荷损耗也会随之增加。

对策

作为应对这种损耗增加问题的对策,可探讨使用输出电流增加时所需的低导通电阻的MOSFET,且Qg低的MOSFET。实际上存在导通电阻低且Qg足够低的MOSFET,这是可以避免的问题。

需要注意的是,Qg低的MOSFET可能会具有急剧的开关上升/下降,这可能会导致开关噪声变大。虽然这种对策具有提高开关速度、降低开关损耗的优点,但需要充分评估EMI问题,也需要考虑PCB设计。

小结:在探讨输出电流大的应用时,需要使用导通电阻低的MOSFET,提高开关速度,并选择DCR低的电感。关于MOSFET,需要选择导通电阻低、Qg低的产品。在这种情况下,开关速度往往会提高,因此需要确认开关噪声是否有增加。

责任编辑:haq

-

电源

+关注

关注

184文章

17779浏览量

250852 -

转换器

+关注

关注

27文章

8732浏览量

147465 -

损耗

+关注

关注

0文章

197浏览量

16046

原文标题:干货|解析电源损耗的评估与计算

文章出处:【微信号:电子工程世界,微信公众号:电子工程世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电源滤波器的插入损耗与其滤波效果之间有何关系?

是德频谱分析仪的回波损耗测试

二极管的反向恢复损耗定义

开关电源的损耗跟输出有关系吗,开关电源的损耗主要包括哪些内容

如何减少开关电源的导通损耗

开关电源MOS管的主要损耗

涡流损耗的大小与铁芯材料的性质

如何使用示波器测量电源开关损耗

PWM方式开关电源中IGBT的损耗分析

电源损耗的定义分析

电源损耗的定义分析

评论