嵌入式 FPGA (eFPGA) 的时代终于到来了,这从其在无线基础设施、人工智能 (AI)、智能存储,甚至对成本敏感的微控制器的芯片中的影响力中可见一斑。作为片上系统 (SoC) 子系统,就像 CPU 或 DSP 一样,它动态地重新配置硬件逻辑,其大小范围从 1,000 到 500,000 个查找表 (LUT)。

EDN采访了 Flex Logix Technologies 的 IP 销售、营销和解决方案架构副总裁 Andy Jaros,以了解这种新兴可编程技术的优势。Flex Logix 成立于 2014 年,是一家 IP 公司,声称提供高密度 FPGA 架构以促进逻辑可重构性,而无需设计工程师进行繁重的工作。

我们通过向 Jaros 询问这项技术的起源来开始讨论。Jaros 是半导体行业的资深人士,其职业道路从 Arm 和 ARC 到摩托罗拉和 Synopsys。

历史:没那么快

eFPGA 的概念有一段曲折的历史,可以追溯到 1990 年代。长期以来,半导体行业的人们一直在谈论将 LUT 纳入 ASIC 以获得额外的灵活性。然而,与带有强大工具链的 FPGA 不同,工具的缺乏是在芯片中实现嵌入式 FPGA IP 的主要障碍。

Jaros 回忆说,几十年来一直有人声称创建了 eFPGA 结构。“一些老牌半导体公司的人说,他们在大约 20 到 30 年前曾经这样做过,但他们实施嵌入式 FPGA 的方式占据了很大的领域。”

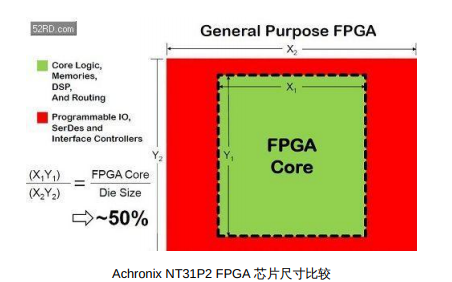

传统FPGA采用网状互连,FPGA中80%的面积被互连占用。Flex Logic 联合创始人 Cheng Wang 开发了一种分层互连,与网状互连相比,它占用的面积只有一半。反过来,这提供了显着的面积和成本优势。eFPGA IP 供应商还声称其互连实现了 90% 的利用率;另一方面,在分立 FPGA 中使用网状互连时,我们看到近 70% 的利用率。

图 1eFPGA 可以针对各种总线大小轻松优化。资料来源:Flex Logix

现状:生意不错

eFPGA 技术非常通用,因为它支持从非常小的实例到非常大的各种应用实例。eFPGA 的工作原理类似于现成的 FPGA 芯片,可以在几天内交付任意大小的阵列。

“我们对 ASIC 公司的吸引力很大,”Jaros 说。“将 FPGA 功能集成到 ASIC 中提高了性能并降低了系统级的功耗和成本。” 这允许设计工程师根据应用要求完全取消 FPGA 或使用更便宜的 FPGA。

Jaros 还指出,传统上使用 FPGA 的系统公司正开始与其 ASIC 合作伙伴一起探索 eFPGA IP。它允许系统制造商停留在中间堆栈的较低级别。此外,虽然市场需求瞬息万变,但汽车原始设备制造商和一级供应商等系统制造商迫不及待地等待一年来添加新功能。“因此,某些 RTL 可配置性比 10 年前更有意义。”

然后,有更高端的 MCU 开始集成硬件加速器,无论是用于神经网络 AI 处理还是专有代码加速。这些场景通常使用 16,000 到 20,000 个 LUT。接下来,Jaros 看到了混合信号公司的更多兴趣。“数字方面唯一改变的是状态机,”Jaros 说。“因此,混合信号设计人员正在寻找 eFPGA,以便在无需投资 MCU 和完整的软件工具流程的情况下,为状态机增加一定程度的可配置性。”

图 2Flex Logix 的 eFPGA 基于 EFLX 4K,该 tile 有两个版本:所有逻辑或主要是带有一些乘法累加器 (MAC) 的逻辑。资料来源:Flex Logix

未来:与分立 FPGA 的竞争

关于 eFPGA 业务的普遍看法是,它将对独立 FPGA 细分市场构成威胁。然而,英特尔和赛灵思正在做的是开发复杂的产品。“英特尔和赛灵思正在进入更大的 FPGA 空间以支持超大规模数据中心,为此,他们正在他们的 FPGA 周围添加硬件 CPU 子系统,”Jaros 说。“我认为 eFPGA 不会影响英特尔和赛灵思,因为它们正在销售具有大量功能的大型、昂贵的 FPGA。”

他补充说,eFPGA 业务非常互补。“我们已经与赛灵思和英特尔的人员进行了交谈,他们根本没有发现任何冲突。” 这也是因为对可重构性的要求跨越了广泛的行业领域,因此与传统的 FPGA 公司可能不会有太大的冲突。

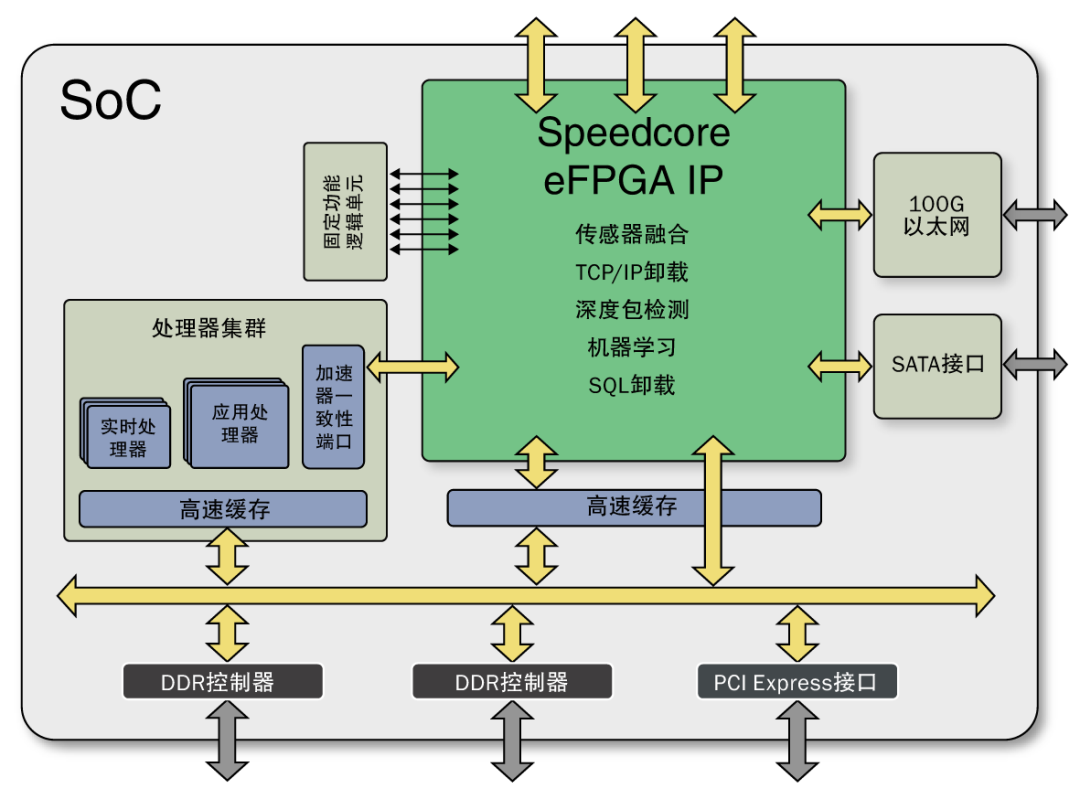

图 3eFPGA IP 供应商认为与传统 FPGA 公司没有太大冲突。资料来源:Flex Logix

推动 eFPGA 业务发展的另一个因素是希望控制其供应链的公司。他们可能拥有自己的 MCU 或 ASSP,并围绕这些 MCU 或 ASSP 构建了软件堆栈。因此,通过添加某种程度的 eFPGA 可重构性,他们可以交换安全算法或专有代码。

eFPGA IP 可从多个供应商处获得,虽然这些 IP 的集成度相对更高,但 FPGA 的密度开始对某些应用有意义。另一件使钟摆转向 eFPGA 的事情是转向更小的工艺节点。Flex Logix 在支持从 180 nm 到 5 nm 的工艺节点的同时,目前一直从事芯片设计一直到 3 nm。

“我们看到越来越多的人愿意为了可配置性而牺牲一点面积,”Jaros 总结道。“因此,在未来 5 到 10 年内流片的绝大多数芯片都将具有一定程度的 eFPGA 内容。” 快速发展的标准和独特的 AI 算法支持这种叙述,以及随后 eFPGA 在不久的将来的承诺。

编辑:fqj

-

FPGA

+关注

关注

1625文章

21664浏览量

601691 -

芯片

+关注

关注

453文章

50378浏览量

421670 -

嵌入式

+关注

关注

5068文章

19013浏览量

303065

发布评论请先 登录

相关推荐

首款嵌入式FPGA诞生 能为AI带来什么?

嵌入式FPGA的相关资料下载

嵌入式 FPGA (eFPGA) 时代已到!浅谈FPGA技术的过去、现在和未来

SoC设计中嵌入FPGA(eFPGA)内核实用评估方法

eFPGA是什么?几个关于eFPGA的常见迷思

如何简单快速的实现嵌入式FPGA

eFPGA在嵌入式360度视域视觉系统中有何应用

如何使用SoC实现嵌入式FPGA的设计

嵌入式FPGA的未来是怎么样的?

对嵌入式FPGA的详解

Achronix Speedcore eFPGA的特性和功能

嵌入式 FPGA (eFPGA) 技术的过去、现在和未来

嵌入式 FPGA (eFPGA) 技术的过去、现在和未来

评论