摘要:近年来,随着轻便便携、多功能化、智能穿戴移动电子产品的发展趋势,驱动电子元器件特别是集成电路(IC)轻薄化、多功能化发展,PCB的厚度也越来越薄。而且,消费电子产品组装工艺已完全无铅化。随着无铅焊料在消费电子产品中的推广应用,给电子产品焊接组装带来巨大挑战,特别是WLCSP/BGA/SIP封装、POP封装器件的批量导入SMT贴片加工生产。由于无铅焊料液化温度(217°C)远高于锡铅焊料(183°C),PCB和元器件在回流焊接过程中产生变形在所难免,BGA焊点锡球虚焊,又名“枕头效应”(Head-in-Pillow)伴随而来。

本文将系统、全面地介绍 BGA 和 CSP 封装器件“枕头效应”产生机理、原因分析、以及结合作者10多年来的现场实际改善案例经验汇总,详细讲解“枕头效应”的如何改善和预防的措施,希望此文能为电子装联的业界的朋友提供一些借鉴和参考作用,提升各自公司/工厂的SMT产线的CSP/BGA类器件的焊接工艺水平。

关键词 枕头效应 切片SEM分析 X-Ray检测 炉温曲线 锡球氧化 枕头效应(Head-in-Pillow,HIP)

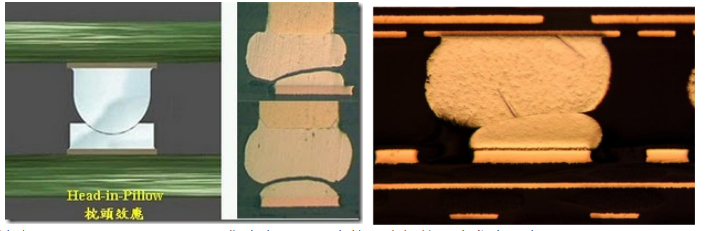

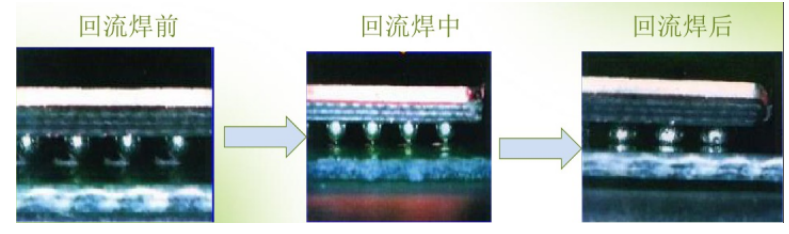

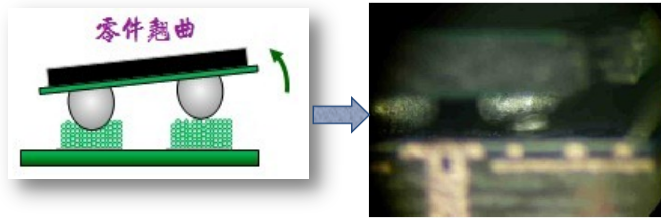

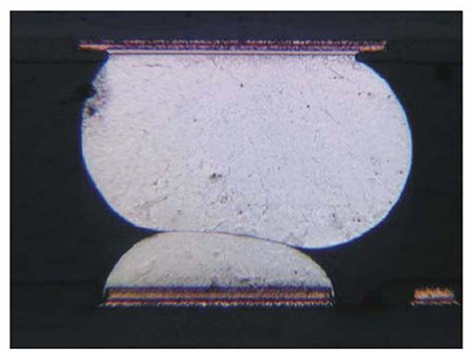

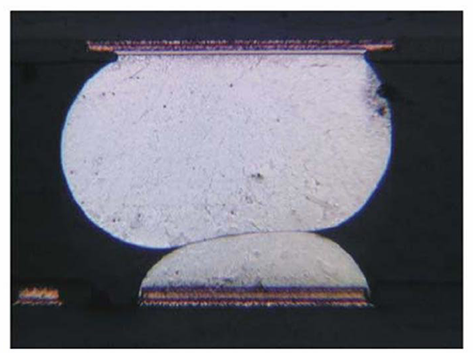

是指BGA类焊点的不良结构、现象从切片的剖面图片来看,类似一个人的头靠在枕头上的形状而得名。枕头效应(Head-in-Pillow , HIP)最主要是用来描述电路板的BGA零件在回焊(Reflow)的高温过程中,BGA载板或是电路板因为受不了高温而发生板弯、板翘(War page)或是其他原因变形,使得BGA的锡球(Ball)与印刷在电路板上的锡膏分离,当电路板经过高温回焊区后温度渐渐下降冷却,这时IC载板/本体与电路板的变形量也慢慢回复到变形前的状况(有时候会回不去),但这时的温度早已低于锡球与锡膏的熔锡温度了,也就是说锡球与锡膏早就已经从熔融状态再度冷却回固态。当BGA的本体与电路板的翘曲慢慢恢复回到变形前的形状时,已经变回固态的锡球与锡膏才又再次互相接触,于是便形成类似一颗头靠在枕头上的虚焊或假焊的焊接形状。

枕头效应(Head-in-Pillow , HIP)主要发生在BGA/CSP、POP封装的器件上,从切片和染色实验结果中可以看出,BGA锡球与PCB焊盘上的焊料虽然接触,但存在明显的界线,不能形成有效的电气和机械连接。这种问题可能在线通过功能测试检测出来(开路),但也可能检测不出(微弱连接)而导致可靠性问题,影响产品的使用,对产品的使用寿命和可靠性上影响很大。

枕头效应(Head-in-Pillow , HIP)集中在SMT工序的回流焊接工序发生,在IPC-7095《Design and Assembly Process Implementation for BGAs》的文件也有详细介绍和定义。

枕头效应的检测和鉴定

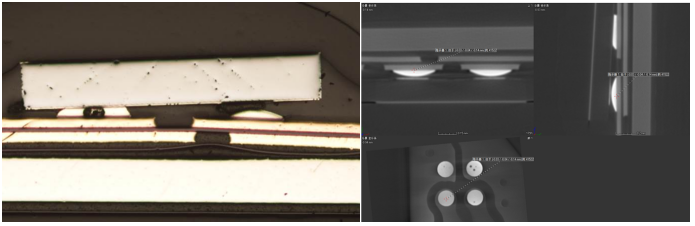

按照上面的理论,枕头效应(HIP)大部分一般发生在BGA & CSP 零件的边缘和四角,尤其是角落的位置,因为那里的翘曲最严重,如果是这样,就可以试著使用显微镜或是光纤内视镜来观察,但通常这样只能看到最外面的两排锡球,再往内就很难辨认了,而且这样观察BGA的锡球还得确保其旁边没有高零件挡住视线,以现在电路板的高密度设计,有一定的局限性。

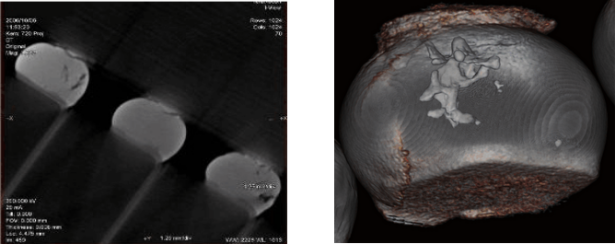

另外,枕头效应(HIP)一般也很难从现在的2D X-Ray检查机发现得到,因为X-Ray大多只能由上往下检查,看不出来断头的位置,如果有可以上下旋转角度的X-Ray机台设备,在枕头效应明显的情况下,BGA/CSP锡球焊点数量较少情况,或者已经明确知道焊点的缺陷位置,仔细采用2.5 D X-Ray去进一步分析才能发现重影有细微的差别,笔者近期内就遇到一起: 0.4 mm pitch CPU的600PCS+锡球的BGA器件,采用YXLON 的2D X-Ray反复去检验未有任何发现。

目前比较可靠可以分析HIP不良现象的方法是使用红墨水染色试验(Red Dye Penetration),以及微切片分析(Cross Section)以及SEM分析,但这两种方法都属于破坏性检测,所以非到必要不建议使用;一般此项方法用于枕头效用的进一步分析来运用。

近年来【3D/5D X-Ray CT】的技术有了突破和发展,对BGA类的虚焊和焊点应力引起的系列问题,可以有效的检查到这类缺陷,进行无损检测,并能够图文并茂展示焊点缺陷。业界一般常见的3D/5D AOI有:伟特科技(Vitrox:原安捷伦技术)、YXLON(德国依科视朗)、凤凰(PHOENIX)、达格(DAGE)、欧姆龙(Omron)、VISCOM、岛津(SHIMADZU)等等

3D/5D X-RAY检测图

枕头效应的形成机理

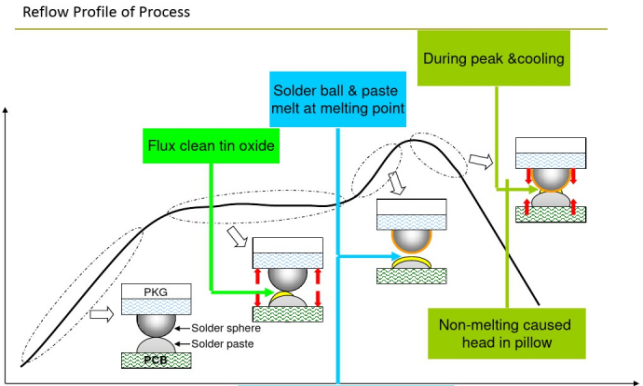

SMT业界认为,枕头效应(Head-in-Pillow , HIP)的形成是因为无铅焊料液化的过程中,无铅制程工艺抬高了回流焊接温度,相对于锡铅焊料高20-30°C(锡铅回流温度210--230°C,无铅回流温度230—250°C)。在回流阶段,BGA/CSP、POP封装元件产生翘曲变形导致锡球与锡膏分离,高温也导致锡膏中的助焊剂成分过度消耗,在冷却恢复过程中,熔融焊料球表面覆盖一层氧化膜导致其不能与PCB上锡膏完全熔融、焊接在一起而形成枕头形状。可以明显看出锡球与焊盘锡膏的分离状态。

枕头效应的产生原因

枕头效应(Head-in-Pillow , HIP)虽然是在回流焊接期间产生的,但是其真正形成枕头效应的原因则可以追溯到PCB、BGA/CSP材料不良、锡膏印刷的不良、贴片精度和稳定性问题、以及回流炉炉温曲线和加热稳定性、MSD器件防潮管控、PCB DFM设计和选材等方面的问题,从人、机、料、法、环等几个方面分析,导致枕头效应发生的潜在因素有很多:

1.钢网开孔设计,开孔面积比小,导致锡膏印刷不良,锡膏在焊盘上分布不均;

2.锡膏印刷,印刷参数设置不当,锡膏在焊盘上分布不均;

3.贴装精度,元件贴装偏位,导致元件锡球不能与锡膏充分接触进行焊接;

4.PCB变形,高温阶段发生变形,导致锡球与锡膏分离而接触不充分;

5.BGA和CSP元件变形,高温阶段发生变形,导致锡球与锡膏分离而接触不充分;

6.锡膏化学成分,助焊剂活性成分沸点低,回流时很容易消耗怠尽,失去活性;

7.回流曲线,回流时间过长,温度过高,导致元件或PCB变形加剧及助焊剂成分过度消耗。

下文将结合笔者在实际工作过程遇到的案例进行逐一讲解和介绍,形成枕头效应(Head-in-Pillow , HIP)原因。

BGA/CSP/POP器件封装(Package)和材料

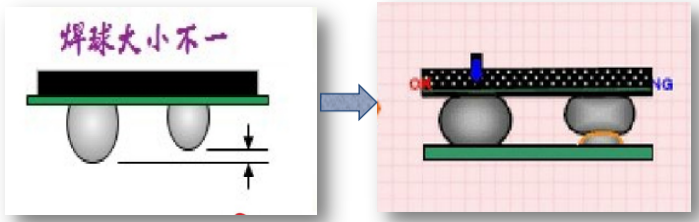

如果同一个BGA/CSP/POP的封装有直径、高低大小不一的焊球(Solder Ball)存在,较小的锡球就容易出现枕头效应的缺点。另外BGA封装的本体载板耐温不足时也容易在回流焊的时候发生本体载板翘曲变形的问题,进而形成枕头效应(Head-in-Pillow , HIP)。

IPC相关标准规定,对于BGA/CSP/POP等底部焊球的器件的共面性有明确的定义,0.5mm pitch以下尺寸封装的器件共面度一般要求控制在0.08mm以内,详细内容可以查询对应器件的技术规格书(Data sheet),贴片机可以通过编程软件的Vision Data数据库来进行有效控制此类异常。

锡膏印刷(Solder paste printing)

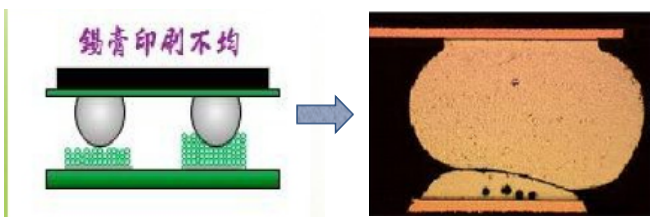

锡膏印刷于焊盘上的锡膏量高度、体积差异太大,或是电路板上有所谓的导通孔在垫(Vias-in-Pad),就会造成锡膏无法接触到焊球的可能性,并形成枕头效应。

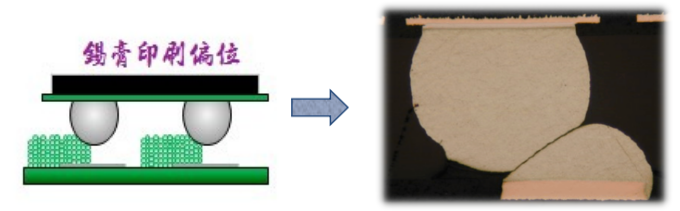

如果锡膏印刷出现偏位现象,这通常发生在多拼板的PCBA时候,当锡膏熔融时将无法提供足够的焊锡形成桥接,同样会有机会造成枕头效应。

目前业界印刷工艺之后一般都会配置SPI检测设备,一般对于BGA/CSP/POP类的器件,都会重点检验其印刷品质,一般的锡膏厚度控制范围:钢网厚度-0.03mm---钢网厚度+0.05mm;锡膏的体积和面积控制范围:40%~180%,锡膏印刷的偏位Offset值一般控制在35%以内,如果是0.4mm pitch封装尺寸以下CSP器件,则管控范围应该缩小。

贴片机的精度不足(Pick & Placement)

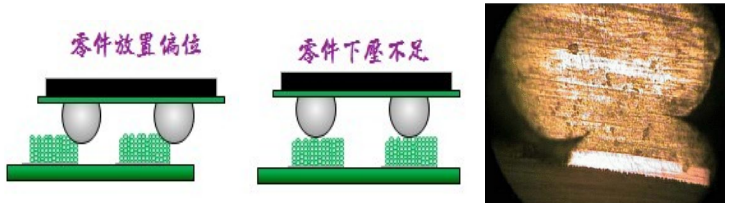

贴片机如果精度不足、稳定性差或是贴装时XY坐标位置及角度没有调整好,也会发生BGA的焊球与焊盘错位的问题;另外,贴片机放置IC零件于电路板上时都会稍微下压一定的Z轴高度,以确保BGA的焊球与电路板焊垫上的锡膏有效接触,这样在经过回流焊时才能确保BGA焊球完美的焊接在电路板的焊垫。如果这个Z轴下压的力量或行程不足,也有机会让部份焊球无法接触到锡膏,也有形成枕头效应HIP的可能。

目前业界BGA/CSP、POP封装类器件贴装一般采用高精度的多功能贴片机,并且在炉前配有AOI,可以有效控制上述器件的贴装精度,选择的贴片机的精度和重复精度为:30μm@3σ,CPK/CMK为1.67以上,可以有效规避上述问题。

贴片偏位的BGA器件的焊接过程

回流焊温度(Reflow Profile)和形变因素

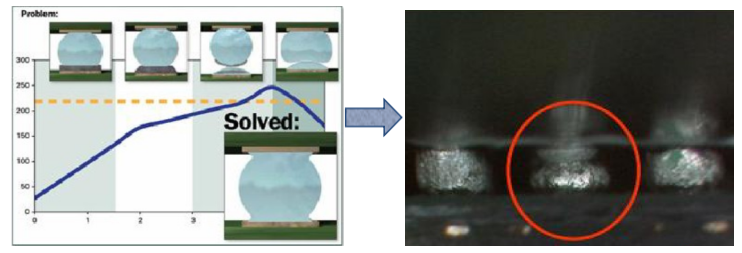

当回流焊(Reflow)的温度或升温速度没有设好时,就容易发生没有融锡或是发生电路板及BGA载板板弯或板翘…等问题,这些都会形成枕头效应。了解BGA本体载板与电路板因为CTE系数、或者PCB板材采用TG值偏低,回流焊接时形变的差异过大,以及回流时间TAL(Time Above Liquids)过长,而造成的PCB板弯板翘所形成的BGA空/虚焊及短路的分析。

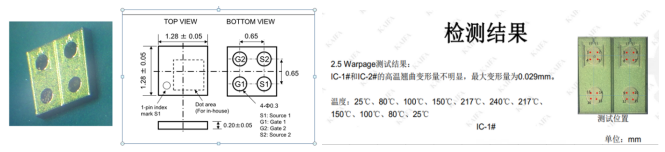

笔者近期改善解决一个因WLCSP玻璃芯片在回流焊接时变形量偏大的HIP & NOW 焊接不良,不良状况和图片如下:

-

改善前后数据对比:

1. 改善MOS空焊不良:1.2%(从去11月至今年4月份一直未得到有效改善,具体原因一直未调查清楚);

2. 改善后投入124000,不良数3PCS,不良率:0.0024%。

-

主要原因:

1) 是该WLCSP 芯片在回流焊接时产生一定量形变,导致焊接时形成了空焊HIP & NOW现象;

2) 送第三方实验室分析,热仿真阴影鱼纹图像数据,也初步证实MOS物料在回流焊接产生一定的形变;

3) 元件的厚度只有0.15~0.20mm,变形量0.03mm,已经达到16.7~20%,超过元件本体厚度的15%以上(业界一般要求控制在10%以内在回流焊接是变形量,研发物料选型的评估的时候应该关注此问题)。

-

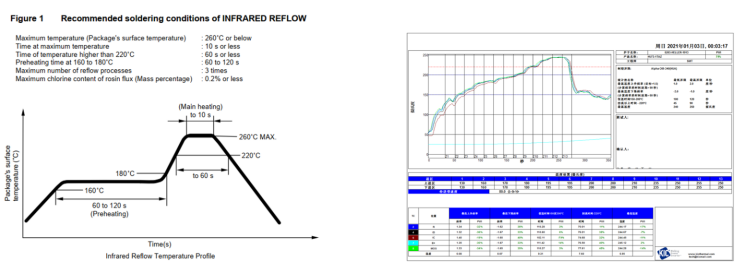

炉温参数:该物料的炉温推荐曲线与我们实际生产炉温曲线有一定区域;(WLCSP MOS芯片需要参考该物料推荐炉温曲线进行炉温参数设置)

1. 该物料的推荐炉温曲线如下:回流时间(即220℃以上时间只能小于60S)

2. 实际炉温参数设置,测出Profile曲线,回流时间220℃以上时间已经达到75S(参考客户推荐SPEC和锡膏的推荐炉温曲线)。

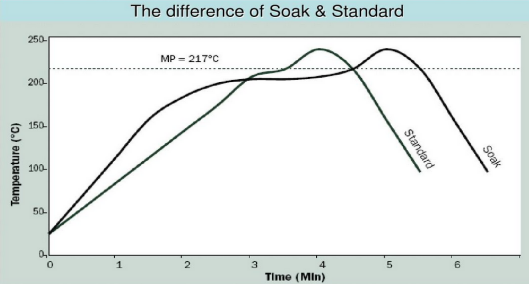

另外,要注意预热区的温度升温如果太快的话容易驱使助焊剂过早挥发,这样就容易形成焊锡氧化,造成润湿不良。其次最高温度(Peak Temperature)也最好不要调得过高及过久,建议最好参考一下BGA/CSP、POP封装器件的温度及时间的建议,并进一步结合锡膏厂家推荐炉温曲线,二者有效结合,才能有效规避因炉温设置不合理导致枕头效应(Head-in-Pillow , HIP)

如下为:Indium8.9HF和Indium10.8HF锡膏推荐和建议的炉温曲线,适当优化Soaking zone profile可以有效降低枕头效应发生的几率

BAG焊球氧化、脏污(Solder ball Oxidization and Dirty)

BGA/CSP、POP封装器件在IC封装厂完成后都会使用探针来接触焊球作F/T功能测试,如果探针没有及时清洁或者针头有异物残留,有机会将污染物粘污于BGA的焊球而形成虚焊、假焊、空洞等焊接不良。其次,如果BGA封装未被妥善存放于温湿度管控的环境内(MSD管理失控),也很有机会让焊球氧化至影响焊锡的结合性。

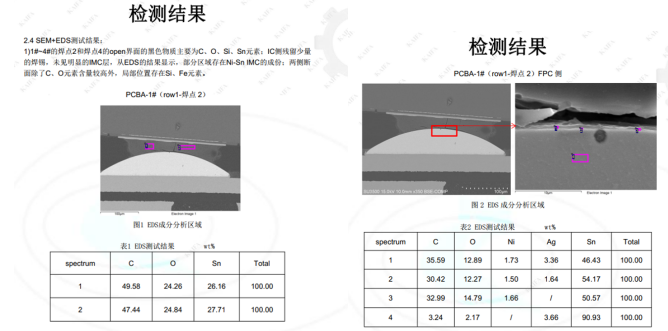

笔者前文分享遇到的案例,根据对不良PCBA/PCM的SEM/EDS分析,焊接界面C、O元素有一定量偏高,详细数据如下:

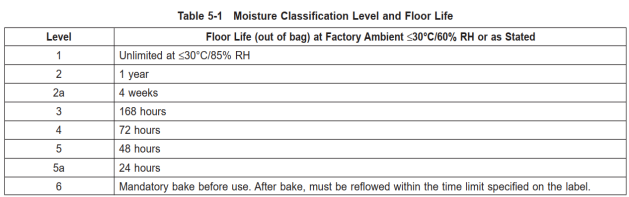

BGA/CSP、POP封装器件都是MSD(Moisture Sensitive Devices)潮湿敏感器件,需要按照IPC/JEDEC J-STD-033A文件规定的内容进行管控,包括:使用寿命、车间寿命、包装方式、烘烤方式等;因此SMT产线产生的此类散料、抛料等需要有效管控、确保其在有效的车间使用寿命内,如果超过车间使用寿命,则需要按文件规定烘烤处理后,重新真空包装处理,并采用手工或者公司的系统记录处理。如下表格为:各等级的MSD器件的开袋后的车间寿命

PCB材料选型和焊盘设计(PCB DFM)

目前,便携式电子产品PCB的厚度越来越薄,如果PCB板材采用TG值偏低(中TG或者低TG值),PCB的热膨胀系数CTE(Coefficient of thermal expansion)值偏大,即回流焊接时容易产生形变,增加了产生枕头效用的风险,建议产品在立项评估阶段时就需要谨慎评估PCB的板材,如果产品芯片BGA焊点锡球数量都是400PCS+以上,建议采用高TG值材质的PCB板材,减少PCB在无铅回流焊接时候的热形变因素。(Remarks: 一般TG的板材为130度以上,High-TG一般大于170度,中等TG约大于150度,基板的TG提高了,印制板的耐热性,耐潮湿性,耐化学性,耐稳定性道等特征都会提高和改善。)

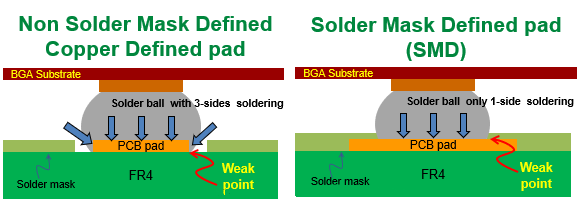

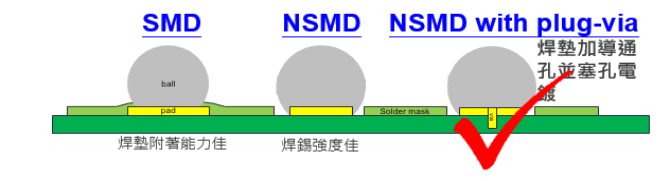

另外,PCB的阻焊开窗方式(Solder Mask)也会对枕头效应和焊点的可靠性有一定的影响,一般BGA/CSP、POP封装器件对应的PCB焊盘设计,强烈建议采用NSMD+Via,而且焊垫上的导通孔(via)必须镀铜填孔塞平,最好还要尽量加大焊垫的尺寸,如果无法让BGA所有焊垫都这样执行,至少要让BGA最外一排的焊垫这样设计。下图为SMD(Solder Mask Defined)与NSMD(Non-Solder Mask Defined)阻焊开窗方式的示意图:

回流炉的热稳定性和充氮、底部支撑( Reflow Stability and Fill N2 and Supporting Pin )

这是最容易忽视的一个因素,由于涉及到SMT工厂前期的投入和成本控制,从长远角度和失效损失成本来看,采用热稳定良好、热均匀性良好、冷却效果更佳的10温区以上回流炉更能够有效规避枕头效应(Head-in-Pillow , HIP)等焊接异常的产生,如果对应BGA/CSP芯片的间距在0.5mm pitch以下、以及含有POP、Flip chip封装器件,导入N2回流炉是一种优先考虑的选择(条件允许的情况可以考虑真空回流焊)。如果前期投入回流炉设备的时候不考虑产品的升级换代、而一味考虑设备的成本问题的话,EMS工厂工艺、品质、设备人员会因为各种离奇的焊接缺陷问题,天天忙于救火的。整个SMT环节中,只有回流焊接过程是不可视的,涉及到复杂的物理和化学反应,以及微观的变化;而SMT工艺人员只能通过炉温曲线去监控回流炉运行状况。

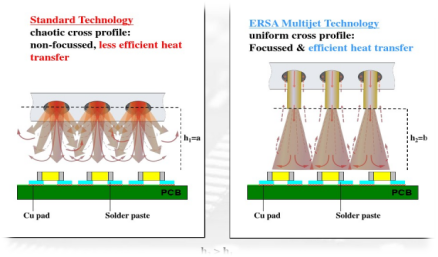

ERSA回流炉与一般回流炉内部加热效果的对比

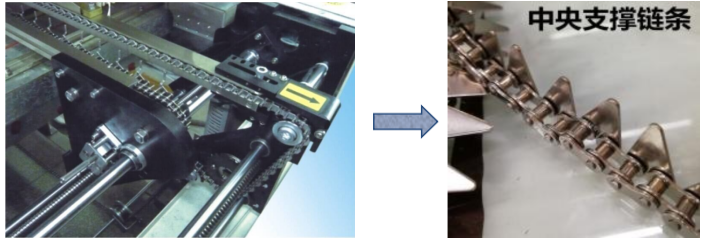

前面文章有描述的PCB材料变形因素、以及回流炉无铅高温热冲击引起的变形问题,这都是客观存在问题,由于涉及的投入成本问题,不可能所有的产品SMT都采用使用过炉载具(Fixture)支撑辅助过炉焊接,因此回流炉轨道中央支撑技术应运而生,示意图如下:

随着焊接工艺技术的发展,回流设备的技术也越来越高,根据笔者10来年的从业经验,目前业界焊接稳定性较好的回流焊国外品牌有:ERSA、Vitronic Soltec、REHM、BTU、Heller、ETA;国内的日东、劲拓的回流炉技术也在不断发展。

目前,真空回流焊技术日趋成熟稳定,在国防军工、医疗产品、汽车电子等高可靠性产品逐步推广使用,使用真空回流焊接技术,在回流焊接时规避BGA焊盘和锡球的二次氧化,提高锡膏FLUX的活性确实也能有效规避枕头效应HIP的产生。

总结与改善思路

1.电子产品中有BGA/CSP、POP封装器件的元件确实容易产生枕头效应也是常见现象,枕头效应产生相关因素确实很多;

2.BGA/CSP的封装和PCB基材的翘曲和以及锡膏中助焊剂的过快消耗容易导致枕头效应的产生;

3.优化回流焊接曲线、采用高稳定性的回流炉、外加充N2辅助焊接,通过减低最高温度和缩短190℃到220℃的升温段的时间可以减少枕头效应等焊接缺陷的产生;

4.使用具有抗高温性和强防氧化保护能力助焊剂的锡膏能减少枕头效应缺陷的发生,推荐使用业界具有消除枕头效应(Head-in-Pillow , HIP)的锡膏品牌,例如:Indium10.8 HF Solder Paste;

5.SMT的印刷、贴装、回流焊接的稳定性也会导致枕头效应(Head-in-Pillow , HIP)的产生,需要提升工厂内部的SMT制程工艺水准;

6.BGA/CSP、POP封装器件、锡膏等物料管控、先进先去(FIFO)、MSD器件的有效管理也是不可忽视的一个环节,PCB的选材和设计也是前期需要重点主管的问题;

7.工程人员的分析思维能力、严谨务实作风、以及辅助的分析工具和失效分析方法可以有效提升解决枕头效应(Head-in-Pillow , HIP)的水平,并提供改善方向和思路。

简而言之:工欲善其事,必先利其器,巧妇难为无米之炊等古语其实也在一定程度上描述解决和消除枕头效应(Head-in-Pillow , HIP)的方法和思路,举个不恰当例子:某个人由于起身体抵抗力、免疫力不强、体质差,容易感冒,冬天的时候冷空气南下、晚上睡觉之前没有开空调、又没有盖好被子,晚上睡一觉醒来之后,第二天出现感冒现象,很难说出来该人出现的感冒的根本原因和主要原因是什么,应该从:内部因素、外部因素、触发因素、其他因素等多方面去分析和改善。

Some of IPC standards and References (IPC标准文件和参考资料)

IPC-7095B/C BGA的设计及组装工艺的实施

IPC-2222 Sectional Design Standard for Rigid Organic Printed Boards

IPC-2221 Generic Standard on Printed Board Design

IPC JEDEC 9703 焊点.可靠性的机械冲击测试指南

ANSI-J-STD-005 Requirements for soldering pastes

IPC JEDEC J-STD-033A 湿敏元件的控制文件

IPC-7527-2012 Requirements for Solder Paste Printing

IPC-9850 Surface Mount Equipment Characterization

IPC-A-610F/G 电子组件的可接受性 CN-2014

IPC-EIA-J-STD-002A 元件引线、端子、焊片、接线柱及导线可焊性试验

铟泰科技(苏州) 通过材料和工艺优化来消除枕头缺陷 PPT/PDF

中国赛宝(广州) 邱宝军 BGA 焊点枕头效应案例分析 PPT/PDF

邹雅冰

善思科技(国际) 常 江 BGA枕头效应2016 PPT/PDF

美信检测(深圳) BGA枕头效应的形成原因和观察方法 HTML

铟泰科技(苏州) Indium8.9HF、10.8HF Pb-Free Solder Paste

RODUCT DATA SHEET PDF/HTML

昇贸科技 Case Study BGA Head-in-Pillow defect issue PDF/HTML

-

pcb

+关注

关注

4333文章

23224浏览量

401855 -

smt

+关注

关注

41文章

2949浏览量

70072 -

BGA

+关注

关注

5文章

549浏览量

47298 -

CSP

+关注

关注

0文章

125浏览量

28256

发布评论请先 登录

相关推荐

BGA焊点空洞的形成与防止

BGA和CSP封装技术详解

BGA枕头效应的形成原因和观察方法

微焦 X 射线在枕头效应缺陷检测应用研究

PCBA布局对温度和形变影响进行HIP缺陷改善

枕头缺陷的产生机理和原因分析

微电子封装技术BGA与CSP应用特点

BGA和CSP枕头效应的形成机理和改善方向

BGA和CSP枕头效应的形成机理和改善方向

评论